如今隨著有源相控陣雷達技術的不斷發展,雷達信號所需要實時處理的數據量也在迅猛的增大,這就使得數據流的高速傳輸面臨著較大的挑戰[1]。以往系統多采用并行方式傳輸高速的數據流,這種方式實現起來相對簡單,但是當數據率超過1 Gb/s時,信號的同步管理變得十分困難,同時接口的數據對齊問題也影響著與外部設備的有效通信。為了解決這一難題,高速串行I/O技術應運而生。串行傳輸所需的引腳數少,降低了背板開發的要求,印制電路板的制作更加簡單,同時可以滿足遠距離高速通信可靠性的要求,被各行各業運用在通信系統的設計中[2]。

為了適應串行技術發展的趨勢,Xilinx公司也推出了內嵌高速串行收發器Rocket I/O的FPGA產品,并在此基礎上開發了Aurora協議。Aurora協議是一款可自由使用相對較簡便的點對點鏈路層協議。其設計目的是使其他高層協議可以很簡單地運行在Aurora之上[3]。其中Aurora IP核支持與光纖的無縫連接,傳輸過程中抗電磁干擾能力強,集成度高,具有很強的靈活性。

1 Aurora IP核的實現

Rocket I/O是內嵌在FPGA中的一款高速串行收發器,支持多種通信協議標準,如Aurora、PCI Express、光纖通道、千兆以太網等[4]。該收發器提供單工或全雙工的數據傳輸模式。

每個Rocket I/O支持622 Mb/s~3.125 Gb/s的數據傳輸速率,并且利用通道綁定功能可以實現更高的數據傳輸速率。收發器模塊物理媒質適配層(PMA)集成了串行/解串器(SERDES)、時鐘和數據恢復電路(CDR)、電流模式邏輯(CML)、預加重/均衡電路等,物理編碼子層(PCS)集成了8 bit/10 bit編解碼電路、循環冗余校驗(CRC)、相位調整FIFO、彈性緩沖器、PRBS產生和檢測等[5]。這些集成的模塊可用于補償信號的高額損耗,減小時鐘的偏差和內部噪聲對接收性能的影響,從而提高信號的質量。

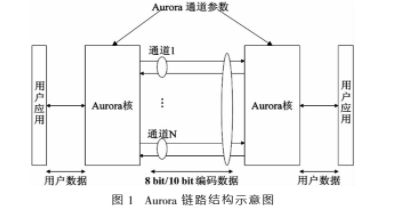

Aurora協議是一款高帶寬、低成本、可擴展、框架簡潔、適合點對點串行數據傳輸的協議。該協議支持專用的上層協議或符合工業標準的協議(例如以太網、TCP/IP),提供了透明接口的串行互連協議,其允許數據進行任何分組封裝,可以使芯片間的數據傳輸在一個較高的水平而不需要改變已有的通信系統或計算機系統[6]。Aurora協議可以配置每個通路中的Rocket I/O工作在全雙工或半雙工的模式下,其鏈路結構圖如圖1所示。

Aurora IP核是Xilinx公司在Aurora協議和高速串行收發器Rocket基礎上研發出來的硬核。該核嵌入在Rocket I/O模塊中,提供了簡單的用戶接口,極大地方便了信號的可操作性。通過IP核用戶界面可以改變Rocket I/O中復雜的控制結構。Aurora IP核主要包括本地流控制、用戶流控制、用戶數據接口、時鐘輸入與時鐘修正模塊、高速串行收發模塊和狀態信息控制模塊[7-8]。

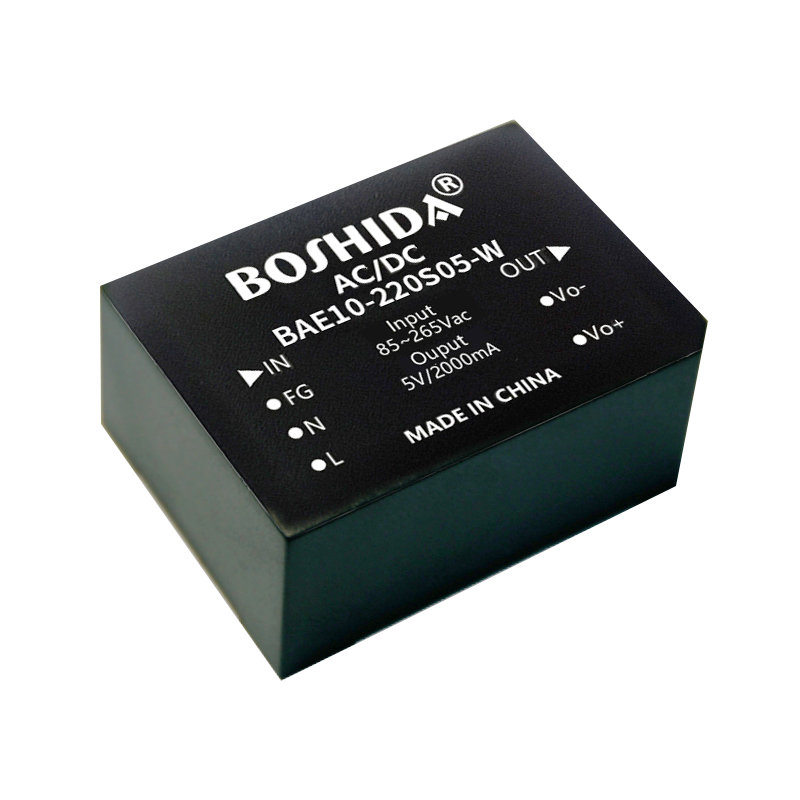

本系統所用Aurora IP核為全雙工模式,通道的線速度為2 Gb/s,輸入參考時鐘為125 MHz,用戶時鐘100 MHz,發送和接收位寬都為16 bit,采用流控的數據傳輸模式。由于發送數據經過Rocket I/O進行了8 bit/10 bit編碼,故而通道串行線性速率為1.6 Gb/s。IP核封裝圖如圖2所示。

其中IP核設計的參考時鐘需要選擇高精度的差分時鐘,這里選用3.3 V供電的貼片差分時鐘,經過IBUFG一級緩沖直接連接到GTX的參考時鐘輸入端,而不能使用經過DCM分頻/倍頻而來的時鐘。因為由DCM引出來的時鐘抖動較大,Rocket I/O在數據傳輸時相當不穩定,會造成數據丟失。

由于Aurora IP核具有時鐘補償功能,在數據接口寬度為2 B的情況下,每5 000個user_clk就需要6個user_clk的時鐘補償,一旦啟用時鐘補償功能,數據流將不能進入Rocket I/O,所以在Aurora IP 核收發器的兩端需要加上一個16 KB的FIFO為數據緩沖做準備,以避免IP核在進行時鐘補償時的數據丟失,同時可以用來匹配AD采樣信號數據時鐘和用戶時鐘user_clk的不一致。解決方案程序如下:

process(USER_CLK)

begin

if USER_CLK‘event and USER_CLK=’1‘ then

count_16bit《=count_16bit+1;

if count_16bit》0 and count_16bit《=2 then

DO_CC《=’1‘; else DO_CC《=’0‘; end if;

end if;

end process;

IP核封裝程序如下:

My_Aurora_AXI4_2Gbps is

Port (

GTX_CLK_125MHz : in std_logic; -- MUST

be 125 MHz

TXP ,TXN : out std_logic; --2 Gbps

RXP ,RXN : in std_logic; --2 Gbps

local_clk : in std_logic; -- 《=200 MHz

reset : in std_logic;

S_AURORA_TX_TDATA : in std_logic_vector

(15 downto 0);

S_AURORA_TX_TVALID: in std_logic;

S_AURORA_TX_TREADY: out std_logic;

M_AURORA_RX_TDATA : out std_logic_vector

(15 downto 0);

M_AURORA_RX_TVALID: out std_logic;

ERROR : out std_logic;

CHANNEL_UP: out std_logic

);

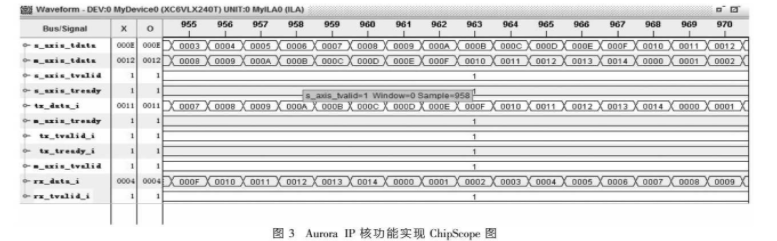

Aurora IP核功能實現ChipScope圖如圖3所示。

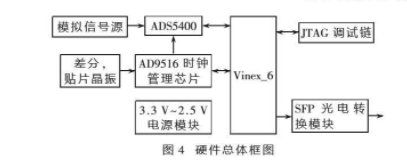

2 測試系統結構

該系統主要由FPGA、ADS5400模/數轉換器以及AD9516時鐘生成模塊、SPF光纖收發模塊、電源模塊等功能模塊組成。首先高頻信號經由ADS5400模/數轉換器采樣,送入并存儲到FPGA的FIFO中。然后經過一系列的邏輯控制,高頻數字信號進入Aurora IP核中,經過Rocket I/O進入SPF光纖模塊將電信號轉換成光信號,通過光纖進行有效的傳輸。系統總體框圖如圖4所示。

2.1 超高速A/D轉換與系統時鐘的實現

在系統發送端采用的是12 bit分辨率及1 GS/s采樣率的ADS5400模/數轉換器。ADS5400中可調節的精細增益、失調和相位可以大幅度地簡化兩個ADC的交錯,這樣就簡化了I/Q接收機中兩個ADC的平衡問題。ADS5400同時有著較好的信噪比,這使其在較高的中頻條件下能夠完成模/數轉換,極大地提高雷達信號處理的速度。

ADS5400的輸入時鐘(也就是采樣頻率)由專用的時鐘芯片產生,其寫配置接口遵循SPI總線接口,采用125 MHz時鐘頻率經由FPGA向其中寫入配置,其中時鐘必須是獨立的外部時鐘且不能和Rocket I/O共用同一時鐘,以防止芯片不能正常工作。此模塊ADS5400輸出采用雙端口模式,clkout被2分頻,使用內部參考時鐘。

在本系統中,AD9516的輸入時鐘是由外部晶振產生的高精度差分時鐘,頻率為200 MHz,使用內部VCO,內部壓控振蕩器的頻率為2 GHz。經過分頻器在LVPECL端和LVDS端分別產生100 MHz的時鐘信號。其中LVPECL端產生的時鐘作為ADS5400的輸入時鐘,LVDS端產生的時鐘作為FPGA的信號時鐘,以便對信號在FPGA中進行進一步的處理,以滿足信號的同源問題,時鐘信號具有較大的靈活性。

2.2 性能測試

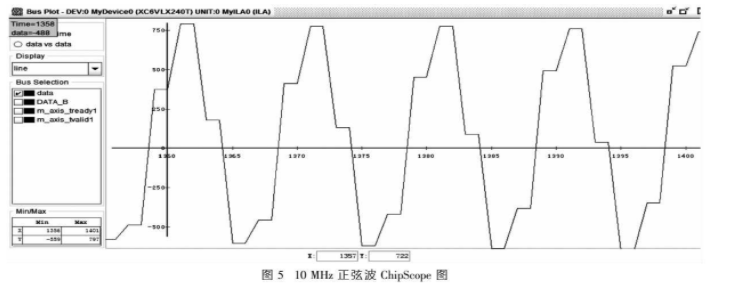

在本系統中采用了Rocket I/O進行光纖通信,為了測試系統的通信性能,Rocket I/O采用了全雙工、流控制的工作模式,其數據傳輸速率為2 Gb/s。由于GTX內部采用了8 bit/10 bit編碼,因而實際上傳輸的有效數據率為1.6 Gb/s。在SFP光纖收發模塊發送器發送數據的同時,接收器立刻接收數據。本設計中選擇Finisar公司的FTLF8519P2xTL光電轉換模塊。主要測試步驟為:(1)給FPGA 處理板上電,向ADS5400和AD9516寫配置之后分別產生100 MHz的采樣信號和100 MHz FPGA時鐘信號;(2)信號發生器產生10 MHz的正弦波連接到ADS5400模/數轉換器;(3)ADS5400把模擬信號轉換成數字信號;(4)將轉換完成的數字信號寫入FPGA的FIFO中;(5)FPGA 將FIFO中的數據通過Aurora IP核經由光纖模塊發送出去,同時光纖模塊接收剛剛發送的數據,并將數據傳入FPGA的FIFO中;(6)運用ChipScope觀測發送和接收到的數據,比較數據傳輸是否正確。

經過長時間的測試,ChipScope抓取的發送和接收數據一致,這表明本系統的光纖通信模塊能夠正常地工作,完成了預期的設計。在硬件實現上的10 MHz ChipScope圖如圖5所示。

本文首先介紹了Rocket I/O在雷達信號處理中的應用,可以極大地提高通信卡之間的通信速率;然后描述了Rocket I/O功能和Aurora核實現高速通信的具體實現過程。整個系統主要實現了對超高速AD采樣信號的高速光纖傳輸,數據傳輸速率達到了2 Gb/s,并且解決了不同通信卡進行數據傳輸Aurora時鐘補償時的數據丟失問題。同時,Aurora核自身有著通道擴展的功能,可以進一步提高數據的傳輸速率,并且可以在實際情況中根據不同的信號頻率動態地調整采樣頻率。由于系統的可編程性,不需要對系統的結構進行大的調整,只需對具體功能進行有效實現,提高了系統的靈活性。

參考文獻

[1] 李江濤.RocketIO高速串行傳輸原理與實現[J]。雷達與對抗,2004(3):48-50.

[2] SAVAGE S.Implementing high-speed serial and custom digital protocols thru FPGA technology and graphical programming techniques[C].Baltimore,2007 IEEE Autotestcon,2007:214-223.

[3] 林振華。基于PCI-X和RocketIO的高速數據傳輸系統設計[J]。現代雷達,2011,33(6):49-52.

[4] Xilinx.Aurora protocol specification[Z].2007.

[5] Xilinx.Virtex_6 FPGA GTX transceivers user guide UG366(v2.6)[Z].2011.

[6] 楊雷,龍哲仁,盧繼華,等.LVDS高速并口通信協議設計[J]。電子技術應用,2013,39(3):119-122.

[7] Zhou Dexiang,Zheng Liping.Study of Aurora IP nuclear communication module based on FPGA[C].2011 IEEE 3rd International Conference on ICCSN,2011:581-583.

[8] Xilinx.LogiCORE IP Aurora 8B/10B V7.1 user guide UG766[Z].2011.

編輯:jq

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605311 -

IP

+關注

關注

5文章

1716瀏覽量

149842 -

cdr

+關注

關注

1文章

50瀏覽量

18141 -

內嵌

+關注

關注

0文章

3瀏覽量

7490

發布評論請先 登錄

相關推薦

常見串口通信協議 如何設置串口參數

高速點焊工藝中先進控制電源的關鍵技術探究與應用

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

PROFINET通信協議是什么

NFC協議分析儀的技術原理和應用場景

USB協議分析儀的技術原理和應用場景

從表象到本質:深入探究TCP/IP協議

高速串行通信協議都有哪些

高速串行通信協議詳解

epa通信協議是什么?epa協議介紹

epa通信協議是什么?epa協議介紹

CC-Link協議是什么?CC-Link協議詳細介紹

高效節能的DC電源模塊技術探究

探究Aurora協議的高速通信技術

探究Aurora協議的高速通信技術

評論