因為最近事情還挺多的,有一段時間沒有更新了,然后想想還是再積累一下再寫新的文章,結果就一個月過去了。。。。所以避免拖延癥繼續發作還是寫一篇一直想寫的文章吧。

最近自己嘗試搭建一個簡單的驗證平臺,入門就先從簡單開始!

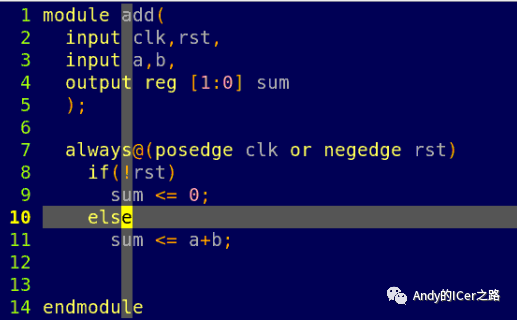

1 RTL設計

RTL就是一個帶時序的1bit加法器,然后驗證是否功能正確。理論上的正確功能應該是輸入數據a和數據b之后的下個周期輸出結果sum等于a+b。

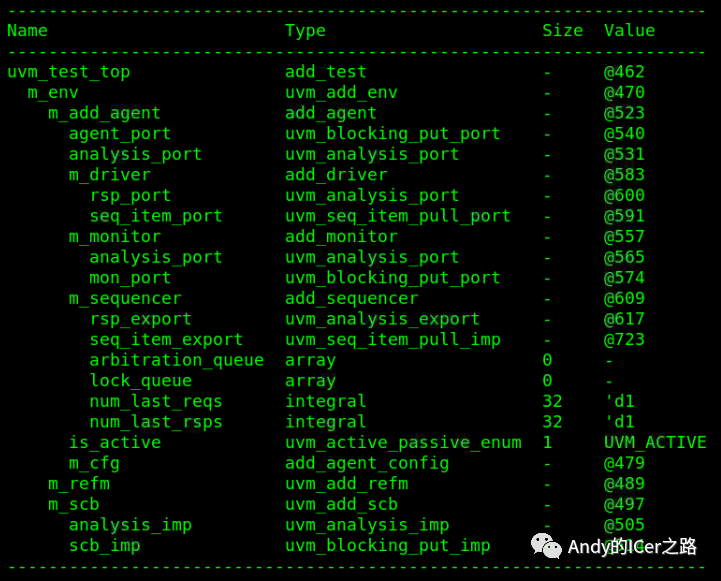

2 UVM驗證平臺建立

將整個UVM驗證平臺分為4個部分agent、env、test、tb,逐層遞進,關于層次大小結構圖可以看這篇文章,下圖是整個驗證平臺的hierarchy。

AndyICer,公眾號:Andy的ICer之路路由器的System Verilog驗證平臺

2.1 agent

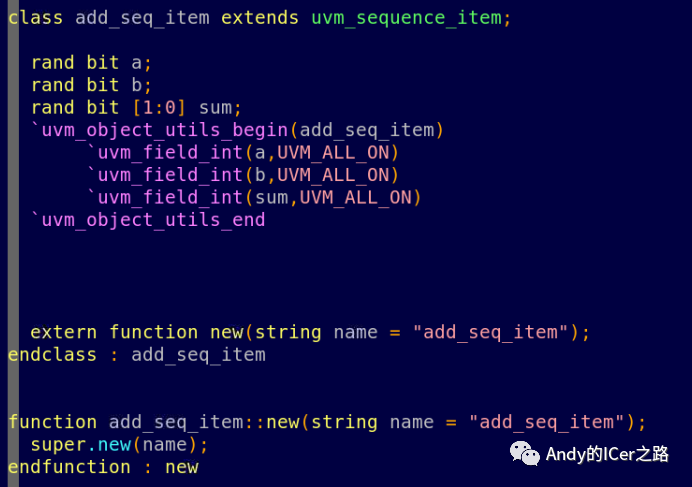

2.1.1 add_seq_item

首先建立一個transaction,即建立一個數據包。

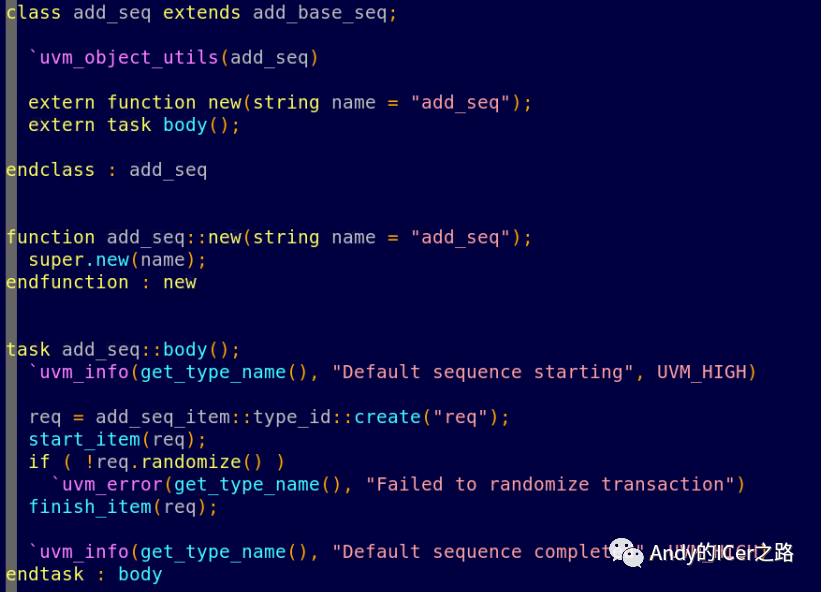

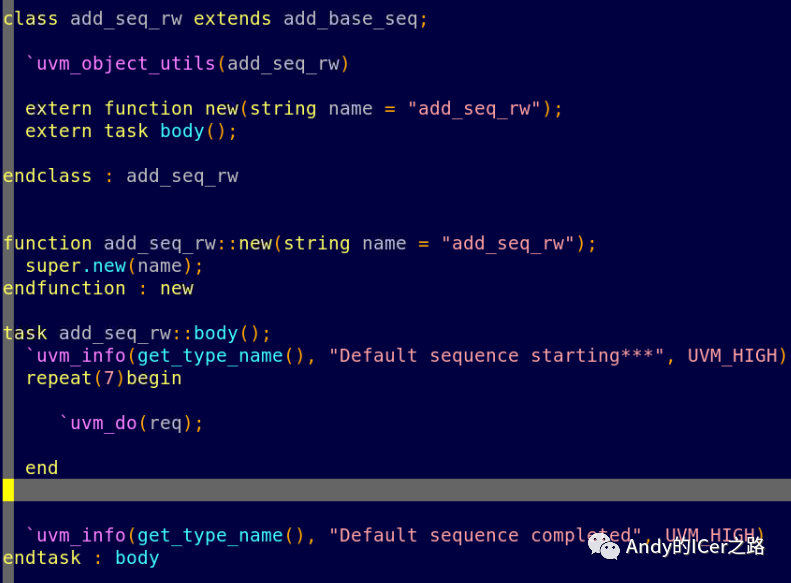

2.1.2 add_seq

建立一個sequence,用來發送transaction。發送transaction的方式有兩種,一種是用start_item()和finish_item(),另外一種是用`uvm_do()的宏。但是兩種方法的原理是一樣的。

法一:

法二:

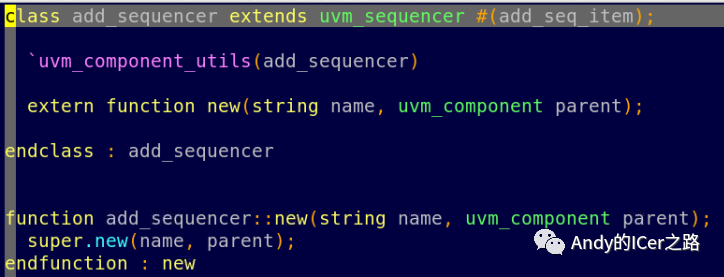

2.1.3 add_sequencer

建立一個sequencer用于與其他模塊通信。

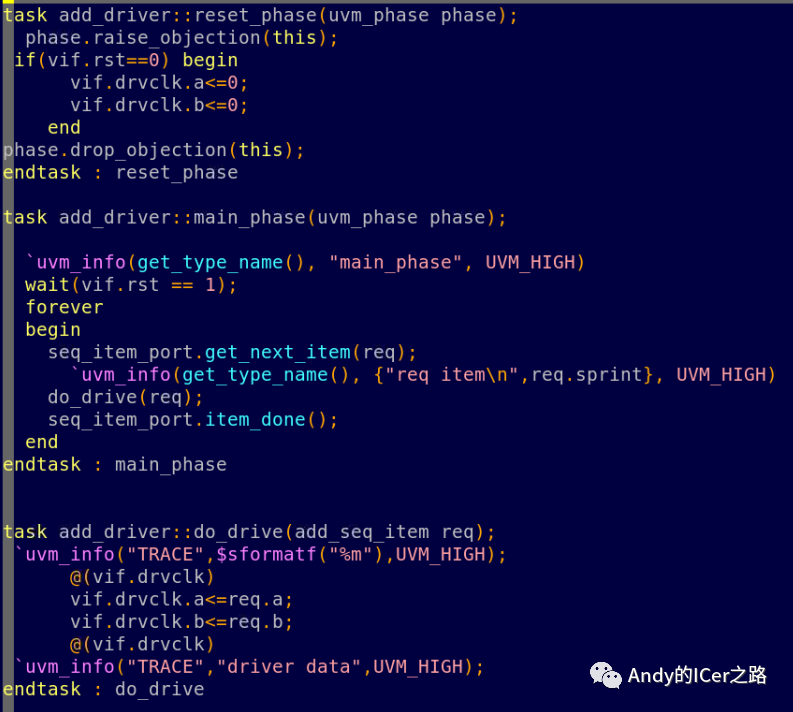

2.1.4 add_driver

driver模塊進行給DUT傳輸數據,reset phase進行DUT復位,main phase進行激勵輸入。

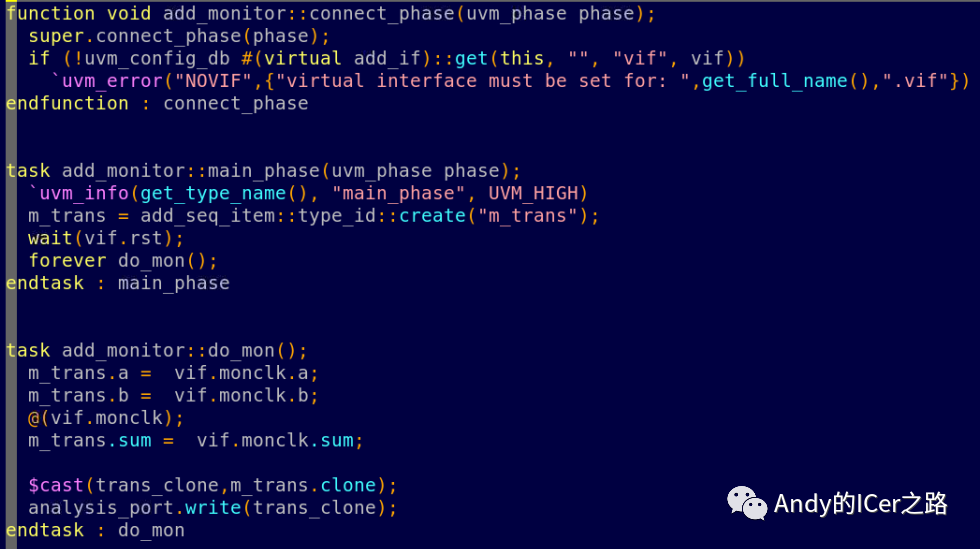

2.1.5 add_monitor

monitor模塊接收DUT發來的數據,并通過TLM通信發送給scoreboard。

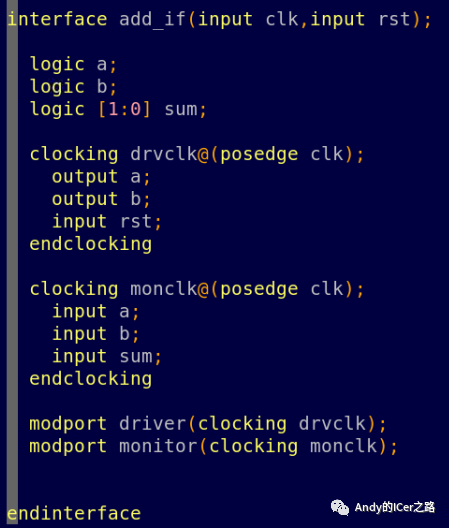

2.1.6 add_if

定義一個Interface,里面包含有兩個clocking block,定義了driver和monitor接口的輸入輸出方向。

2.2 env

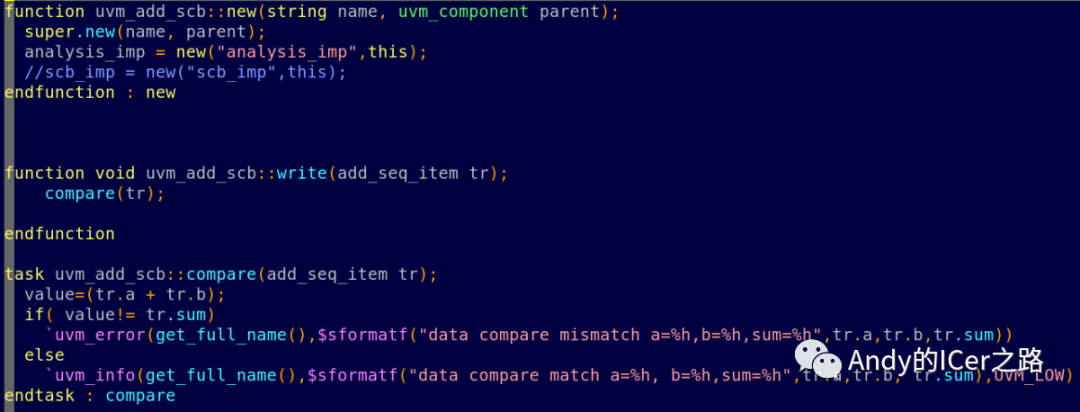

2.2.1 add_scoreboard

建立scoreboard,進行硬件結果和軟件結果的對比。

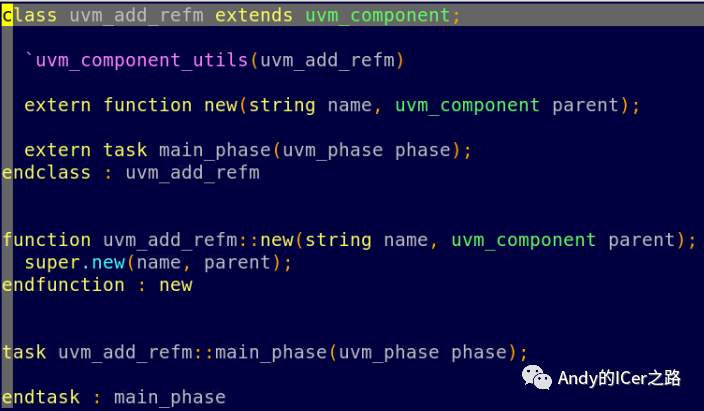

2.2.2 add_reference_model

這里的邏輯比較簡單,就沒有使用到reference model了,但是還是保留有這個模塊。

2.2.3 add_env

env就是把agent、scoreboard、reference model都build并connect起來。

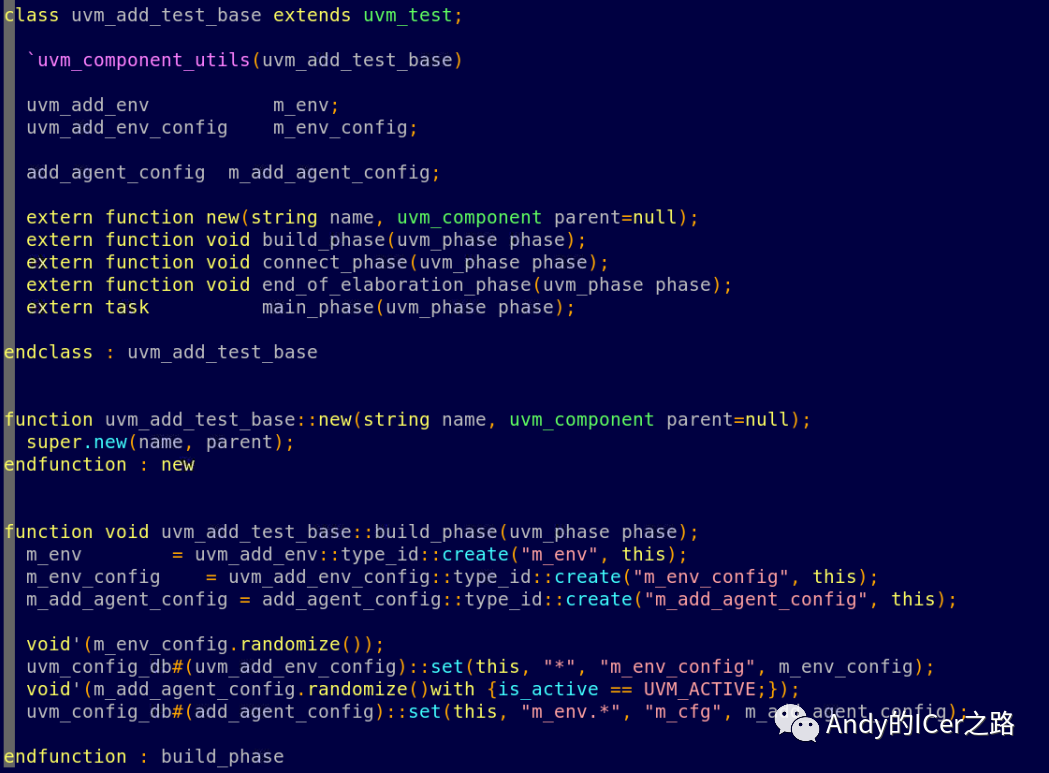

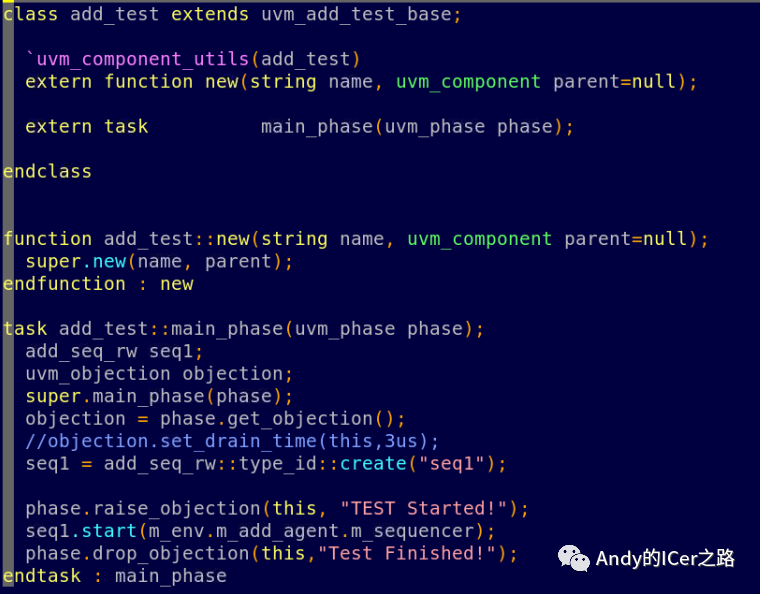

2.3 test

test是驗證環境的頂層,頂層中將env建立好并將configure也建立好,在頂層中進行設置。

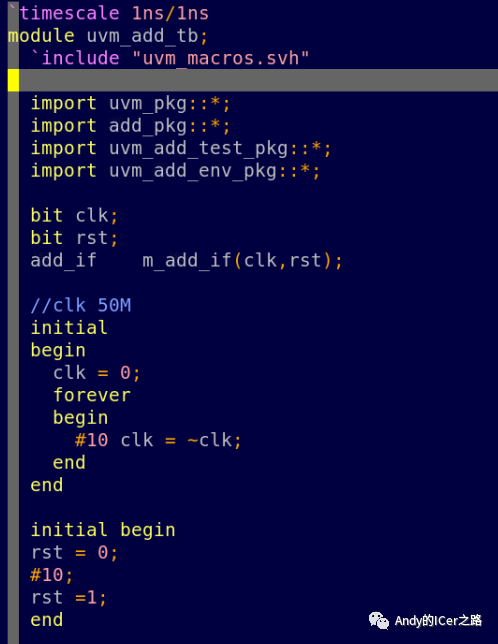

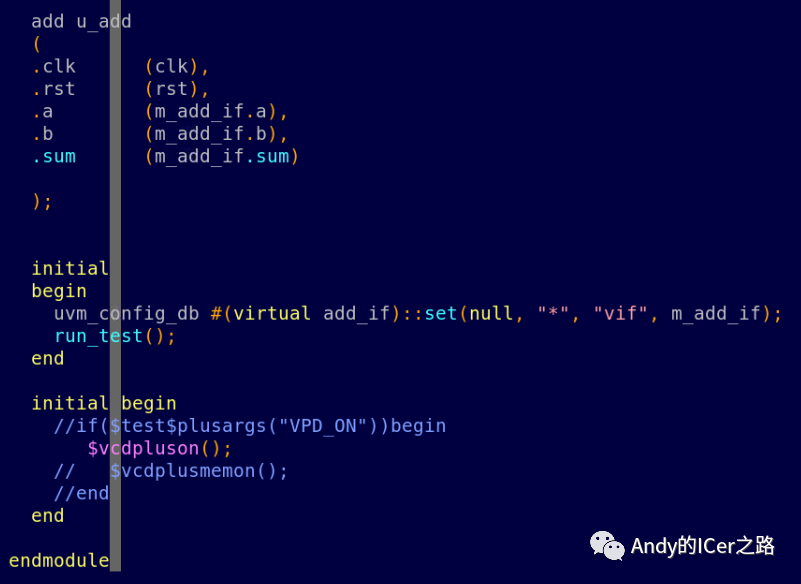

2.4 Testbench

將硬件DUT和軟件驗證環境聯系起來,形成一個完成的測試平臺。

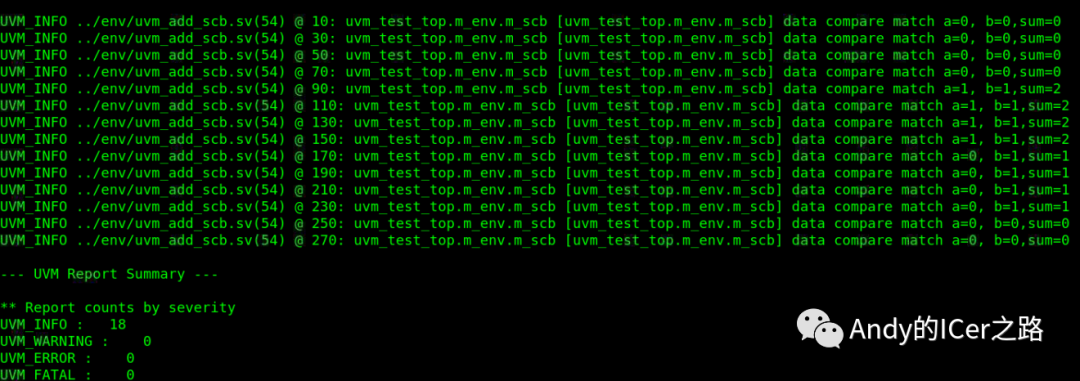

3 驗證結果

可以看出驗證功能正確,并且通過對于driver和monitor時序的調整可以控制輸出結果的時序,大家也可以嘗試搭建一個驗證平臺,對于UVM會有一個更加直觀的感受。

編輯:lyn

-

加法器

+關注

關注

6文章

183瀏覽量

30344 -

UVM

+關注

關注

0文章

182瀏覽量

19283

原文標題:一個加法器的UVM驗證平臺設計

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何搭建一個加法器的UVM驗證平臺

如何搭建一個加法器的UVM驗證平臺

評論