摘要: 為了提高全數字鎖相環的系統運行速度、降低系統功耗,同時提高鎖相系統的動態性能與穩態性能,提出一種基于流水線技術的全數字鎖相環。采用電子設計自動化技術完成了該系統的設計,并對所設計的電路進行了計算機仿真與分析。仿真結果證明,該鎖相環中數字濾波器的參數能夠根據相位誤差的大小進行動態調節,既可加快鎖相速度,又能增強系統的穩定性。利用流水線技術優化的整體電路能夠減小系統延遲,降低系統總功耗。該鎖相環可作為功能模塊嵌入到片上系統,具有十分廣泛的用途。

0 引言

鎖相環是一個能對輸入信號進行自動跟蹤的負反饋控制電路。鎖相環在通信、無線電電子學、自動控制和電力系統自動化等領域得到了極為廣泛的應用,其性能的好壞將直接影響整個電子系統的工作性能[1]。隨著數字技術的不斷發展,全數字鎖相環的應用范圍也更加廣泛[2]。全數字鎖相環具有比模擬鎖相環更多的優點,它可以解決模擬鎖相環中設計復雜性較高、可移植性較差和對噪聲十分敏感等問題[3]。

對于系統芯片而言,系統運行速度和功耗是衡量其性能優劣的重要指標之一,如何提高其運行速度和降低其功耗是國內外學者關注的熱點問題[4]。全數字鎖相環作為系統芯片中常用的功能模塊,這些問題也是我們在設計鎖相環時迫切需要解決的問題。

另一方面,提高鎖相環的鎖相速度與增強鎖相環的穩定性是相互矛盾的。在鎖相環設計時,若數字濾波器的參數取較小值,可加快鎖相環的鎖相速度,縮短鎖相時間,但在系統鎖定后會出現相位抖動,影響系統的穩定性;而其參數取較大值時,雖可減小相位抖動,增強系統的穩定性,但卻又會造成鎖相速度變慢。

由于傳統全數字鎖相環中數字濾波器的參數是固定不變的,不能實現參數的動態調節,因此,在鎖相環設計時只能取某一固定的折中值,這就不能從根本上解決同時提高鎖相環的動態性能與穩態性能之間所存在的矛盾,也就不能最大限度地提高鎖相系統的整體性能。

本文提出的基于流水線技術的全數字鎖相環,一是能夠提高鎖相系統的運行速度,降低系統功耗;二是可實現數字濾波器參數的動態調節,從根本上解決提高鎖相速度與增強系統穩定性之間的矛盾。文中介紹了該鎖相環的系統結構、工作原理及主要模塊的設計方案。利用 Quartus II軟件工具對電路系統進行了仿真驗證,并根據仿真結果對電路參數的變化對鎖相系統的影響進行了分析[5]。

1 流水線技術

1.1 流水線技術的工作原理

流水線技術在速度優化中是常用的技術之一,它能顯著地提高設計電路的運行速度上限[6]。為了保障數據的快速傳輸,必須使系統運行在盡可能高的頻率上,但如果某些復雜邏輯功能的完成需要較長的延時,就會使系統很難運行在高的頻率上。在這種情況下,可使用流水線技術,即在長延時的邏輯功能塊中插入觸發器,使復雜的邏輯操作分步完成,減少每個部分的處理延時,從而使系統的運行頻率得以提高[7-8]。流水線設計的代價是增加了寄存器邏輯,即增加了芯片資源的耗用。具體工作原理如圖1所示。

圖1(a)中的最高工作頻率為1/Ta;在圖1(b)中,將圖1(a)中延時較大的組合邏輯電路分解為兩個延時較小的組合邏輯電路,并在該電路中插入一個寄存器,其中Ta=T1+T2,T1≈T2。該電路中第一級由輸入寄存器、組合邏輯電路和插入的寄存器構成,其最高工作頻率約等于1/T1;第二級由后一個組合邏輯電路和寄存器構成,其最高工作頻率約等于1/T2。因此,該流水線電路結構的最高工作頻率約等于1/T1,與圖1(a)的電路結構相比較,其電路的整體運行速度得到顯著的提高。

1.2 流水線技術的應用

采用流水線技術可以優化計數器的電路,以24位計數器為例,該計數器的進位鏈很長,必然會降低工作頻率。若將其分割成3個8位的計數器,每當8位的計數器計到255后,可利用進位信號觸發下一個8位的計數器工作,這樣便可減少系統的工作延遲,從而達到提高系統信息處理速度的目的[9]。具體實現過程如圖2所示。

其中圖2(a)為沒有采用流水線技術的24位的電路結構,圖2(b)為采用流水線技術設計的電路。從圖2(b)中可以看出,將24位的計數器分為三級流水線設計,每一級為一個8位計數器,其中第一級計數器的位數為0~7位,第二級計數器位數為8~15位,第三級計數器的位數為16~23位。每當低一級的8位計數器產生進位信號時,觸發高一級的8位計數器開始計數,以此類推進行累加計數。采用這種流水線計數器的電路結構,可提高計數器在進位鏈上的處理速度,進而提高整體電路的運行速度。

2 鎖相環主要電路模塊的設計

本文所提出的全數字鎖相環的系統框圖[10]如圖3所示,該鎖相環主要由數字鑒相器、自動變模電路、數字濾波器、加扣脈沖控制電路和N分頻器組成。其中數字鑒相器由雙D觸發器實現,其主要作用是通過比較輸入信號fin與輸出反饋信號FOUT之間的相位變化,產生相位誤差信號ue、超前信號up和滯后信號ud。數字濾波器主要由可逆計數器構成,它可根據超前信號或滯后信號進行加計數或減計數,當計數值達到計數器的模值時,產生進位信號inc或借位信號dec,其中可逆計數器的模值km(即該濾波器的參數)由自動變模電路提供,該信號可根據誤差信號ue的大小自動產生。

加扣脈沖控制電路和N分頻器構成了數字振蕩器,當inc信號為高電平時,在數字序列信號IDout中插入一個脈沖;當dec信號為高電平時,在IDout中扣除一個脈沖,再經過N分頻器得到調節后的輸出信號FOUT。將該輸出信號反饋到數字鑒相器,通過鎖相系統對相位誤差的反復調節,最終達到相位的鎖定。

2.1 流水線自動變模電路設計

數字濾波器的動態參數主要由自動變模電路提供,其中自動變模電路主要是由一個時間數字轉換模塊(TDC)和變模控制器構成,其主要作用是根據數字鑒相器輸出的相位誤差的大小來改變數字濾波器中可逆計數器的模值km。當相位誤差較大時,輸出較小的模值,以便加快鎖相速度;而當相位誤差較小時,輸出較大的模值,以減小環路鎖定后的相位抖動。

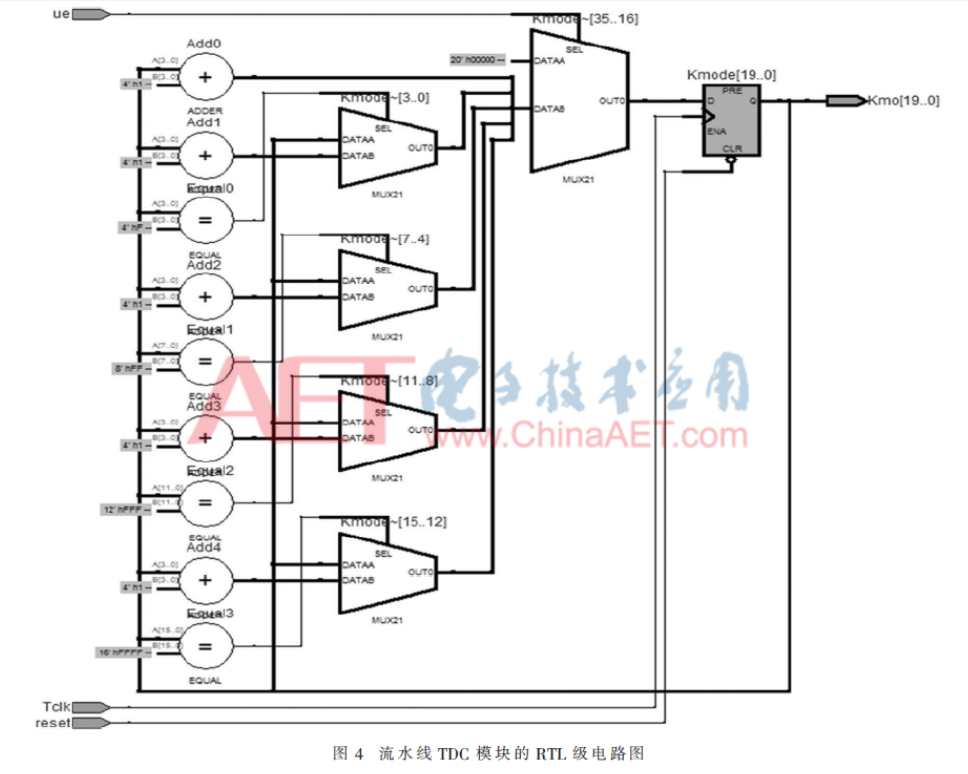

根據本文提出的流水線計數器的設計理念,對TDC模塊中的20位計數器采用5級流水線設計,其中第一級計數器的位數為0~3位,第二級計數器位數為4~7位,第三級計數器的位數為8~11位,第四級計數器的位數為12~15位,第五級計數器位數為16~19位。采用超高速集成電路硬件描述語言(VHDL)對流水線電路結構的TDC模塊進行設計,該模塊的RTL級電路圖如圖4所示。

在采用VHDL完成變模控制器的設計之后,再將兩個模塊連接起來,便可得到流水線自動變模的電路如圖5所示。其輸入信號ue為相位誤差信號,輸出信號km是提供給數字濾波器中可逆計數器的可變模值。

2.2 流水線數字濾波器設計

數字濾波器主要由8位可逆計數器構成,對該可逆計數器采用2級流水線設計,第一級計數器的位數為0~3位,第二級計數器為位數為4~7位。采用 VHDL對流水線電路結構的數字濾波器進行設計,該模塊的RTL級電路如圖6所示。其輸入信號km為計數器的模值,輸出信號dec和inc信號分別為加扣脈沖控制電路的控制信號。

數字濾波器的仿真波形如圖7所示,從圖中可以看出當km的值分別取2,4,8,32時,相應dec和inc信號出現的頻率是不同的。這說明該數字濾波器能夠根據模值km的大小,自動調節其輸出控制信號的頻率,進而可實現對鎖相環工作過程的動態調節。

2.3 流水線分頻器設計

該分頻器是由24位計數器構成,其分頻系數可調。對該計數器采用3級流水線設計,其中第一級計數器的位數為0~7位,第二級計數器位數為8~15位,第三級計數器的位數為16~23位。同樣,采用 VHDL對流水線電路結構的分頻器進行設計,該模塊的RTL級電路圖如圖8所示。

3 鎖相系統的整體設計與仿真

該鎖相系統的整體設計采用自頂而下的設計方法,首先,用VHDL語言對各模塊進行編程設計,在完成各模塊的設計之后,再按照系統設計方案將各模塊連接起來構成系統頂層電路,該系統電路如圖9所示。其中jianxq為數字鑒相器,zdjc為自動變模電路,bknjs8為數字濾波器,ID為加減脈沖控制電路,divN8為N分頻器。Clk為時鐘信號,fin為輸入信號,km為可逆計數器的模值。

系統時鐘頻率取200 MHz,輸入頻率為50 MHz時,對頂層電路進行系統仿真,其結果如圖10所示。

取同一系統時鐘頻率,當輸入頻率由50 MHz跳變為25 MHz時,其仿真波形如圖11所示。

從圖10可以看出,在相位調節區間,鎖相環中可逆計數器的模值km 隨著相位誤差的不同而變化,這樣可以加快其鎖定速度;在相位鎖定區間,則會自動選擇本系統所設置的最大模值km,故可大大減小環路輸出信號相位的抖動,提高了系統的穩定性。從圖11可以看出當輸入頻率發生跳變時,鎖相環能夠在輸入信號頻率發生跳變后的第一個周期內快速鎖定信號的頻率,并迅速對相位誤差進行調整,大約經過2.5 μs便可鎖定,且鎖定后同樣自動選擇最大的km值。

由此可以看出該鎖相環能夠根據其不同的工作過程對系統參數進行動態調節,從根本上解決了提高鎖定速度與穩定性之間的矛盾,提高了鎖相系統的整體性能。

取系統時鐘頻率為200 MHz,輸入信號頻率為50 MHz時,分別對傳統鎖相環和流水線鎖相環進行了系統仿真,并對仿真結果進行時序分析和功耗分析。具體結果分析如表1所示。

從以上表格可以看出,首先,與傳統的鎖相環相比,流水線電路結構鎖相環的系統延時減少了1.278 ns。其次,時鐘頻率為200 MHz時,其系統的總功耗比傳統的鎖相環減少了630 μW。由此可見,具有流水線電路結構的全數字鎖相環可以減少系統延時,提高系統的工作速度,并可減少系統的總功耗。

4 結論

本文所提出的全數字鎖相環采用流水線技術優化了系統的電路結構,減少了系統延遲,提高了系統的運行速度,降低了系統的總功耗。由于數字濾波器的參數可以動態調整,故既能提高鎖相速度,又可增強系統的穩定性,從而很好地解決了兩者之間所存在的矛盾。

參考文獻

[1] Guo Xiaoqiang,Wu Weiyang,Chen Zhe.Multiple complex-coefficient-filter based phase-locked loop and synchronization technique for three-phase grid-interfaced converters in distributed utility networks[J].IEEE Transactions on Industrial Electronics,2011,58(4):1194-1204.

[2] 彭詠龍,路智斌,李亞斌。基于FPGA的改進型全數字鎖相環的設計[J]。電源技術,2015,39(2):410-412.

[3] STASZEWSKI R B,MUHAMMAD K,LEIPOLD D,et al.All-digital TX frequency synthesizer and discrete time receiver for Bluetooth radio in 130-n/n CMOS[J].IEEE Journal of Solid-State Circuits,2004,39(12):2278-2291.

[4] 單長虹,陳忠澤,單健。基于雙邊沿觸發計數器的低功耗全數字鎖相環的設計[J]。電路與系統學報,2005,10(2):142-145.

[5] 黃保瑞,楊世平。基于FPGA的全數字鎖相環設計[J]。電子測試,2014(8X):33-34.

[6] 潘松,黃繼業.EDA技術實用教程VHDL版(第5版)[M]。北京:科技出版社,2013.

[7] 崔秀敏。基于FPGA的流水線技術設計與實現[J].Science & Technology Information,2010(7):76-77.

[8] 何永泰,董剛,黃文卿。流水線技術在FPGA設計中的實現[J]。天津工業大學學報,2006,25(4):84-86.

[9] Xu Liangge,LINDFORS S.A high-speed variable phase accumulator for an ADPLL architecture[J].2008 IEEE International Symposium on Circuits and Systems,2008.

[10] 單長虹,鄧國揚。一種新型快速全數字鎖相環的研究[J]。系統仿真學報,2003,15(4):581-583.

編輯:jq

-

濾波器

+關注

關注

161文章

7858瀏覽量

178671 -

編程

+關注

關注

88文章

3637瀏覽量

93903 -

鎖相

+關注

關注

0文章

12瀏覽量

11611 -

脈沖控制

+關注

關注

0文章

19瀏覽量

8254

發布評論請先 登錄

相關推薦

SMT流水線布局優化技巧

鎖相環PLL的工作原理 鎖相環PLL應用領域

數字鎖相環固有的相位抖動是怎樣產生的,如何解決

數字鎖相環提取位同步信號怎么設置

簡述鎖相環的基本結構

探究流水線技術的全數字鎖相環設計

探究流水線技術的全數字鎖相環設計

評論