1984年,Xilinx公司的創(chuàng)始人之一,密西根大學(xué)畢業(yè)生,RossFreeman第一次提出了可編程邏輯器件(PLD)的概念,讓芯片成為一個(gè)空白的畫(huà)布,可由工程師通過(guò)編程在上面任意“涂鴉”。

Freeman也因?yàn)檫@項(xiàng)發(fā)明進(jìn)入2009美國(guó)發(fā)明家名人堂。遺憾的是英年早逝的他沒(méi)能看到他所締造的FPGA帝國(guó)是多么的輝煌。

清華大學(xué)微電子研究所所長(zhǎng),中國(guó)半導(dǎo)體行業(yè)協(xié)會(huì)副理事長(zhǎng)魏少軍先生曾用印一本書(shū)來(lái)區(qū)別芯片的設(shè)計(jì)、制造、封測(cè)過(guò)程:設(shè)計(jì)相當(dāng)于作家寫(xiě)了一本書(shū),制造相當(dāng)于印刷,封裝相當(dāng)于裝訂。那么FPGA是什么?如果是一個(gè)專(zhuān)業(yè)從事FPGA工作的老攻城獅可能會(huì)告訴你,”Field Programmable Gate Array“,然后再補(bǔ)上一句”It can be anything you want“。網(wǎng)上也有很多通俗易懂的類(lèi)比。例如把FPGA的開(kāi)發(fā)看作是數(shù)字積木搭建,東南大學(xué)湯勇明老師就寫(xiě)過(guò)一本《搭建你的數(shù)字積木——數(shù)字電路與邏輯設(shè)計(jì)》

一個(gè)個(gè)IP就像是一塊塊積木,通過(guò)調(diào)用IP"搭建"特定功能的電路,這個(gè)比喻來(lái)說(shuō)明FPGA的開(kāi)發(fā)再合適不過(guò)了。

也有人將FPGA比作是空白的大腦,大腦里面存在成千上萬(wàn)的神經(jīng)元細(xì)胞,但是神經(jīng)元之間并沒(méi)有連接起來(lái),也就還沒(méi)有大腦強(qiáng)大的功能,但是當(dāng)工程師用Verilog或者vhdl來(lái)對(duì)FPGA進(jìn)行布局布線之后,神經(jīng)元就連接到了一起,大腦也就有了一些功能,給大腦輸入羊肉泡饃的畫(huà)面,會(huì)流口水之類(lèi)的反應(yīng)。這個(gè)比喻來(lái)形容FPGA的設(shè)計(jì)原理再合適不過(guò)了。

另外,還有人將FPGA中的一些組成部分和生物化學(xué)有機(jī)體類(lèi)比。FPGA中最基本的單元——可編程邏輯單元(CLB),可以類(lèi)比為有機(jī)體中的蛋白質(zhì)分子,生物化學(xué)的角度上,蛋白質(zhì)可以合成更高更復(fù)雜的器官,例如心,肝,胃,胳膊腿等,那么同樣CLB作為電子有機(jī)體中的蛋白質(zhì)分子,當(dāng)然就可以合成一個(gè)電子有機(jī)體(類(lèi)比人)的各個(gè)模塊(器官),有的器官?gòu)?fù)雜,需要很多蛋白質(zhì)分子分層次合成,那么同樣,有的電子系統(tǒng)的模塊的也極其復(fù)雜,需要CLB分層次合成。

那么蛋白質(zhì)分子在合成各種不同的器官的時(shí)候,靠什么做指導(dǎo)嘞?人體內(nèi)部有著極其龐大復(fù)雜的DNA序列,這個(gè)DNA序列記錄著人體的所有信息。在受精卵生成胚胎階段,其中的某一段序列指導(dǎo)胚胎的這一坨(也就是這一堆蛋白質(zhì)分子)成為未來(lái)的手,另一端序列指導(dǎo)胚胎的另一堆蛋白質(zhì)分子成為未來(lái)的胳膊。那么同樣,在FPGA中也會(huì)有等價(jià)于生物化學(xué)有機(jī)體中的DNA,就是bit_stream。bit_stream和DNA完全類(lèi)似,就是一段序列,指導(dǎo)著若干CLB合成某一個(gè)執(zhí)行具體功能的模塊。

在有機(jī)體中還有脂肪的存在,脂肪的一大作用就是存儲(chǔ)能量,在FPGA中負(fù)責(zé)存儲(chǔ)的是BRAM,不同的是脂肪儲(chǔ)存的是能量,BRAM儲(chǔ)存的是數(shù)據(jù)。

FPGA中還有一個(gè)很重要的東西叫做DSP,即數(shù)字信號(hào)處理器,在人的大腦里面有一片腦回溝區(qū)域?qū)iT(mén)負(fù)責(zé)數(shù)學(xué)運(yùn)算,兩者可以做一個(gè)類(lèi)比。

生物體中還有一個(gè)十分重要的器官叫心臟,而FPGA中有一個(gè)東西叫時(shí)鐘,心臟控制脈搏,時(shí)鐘則負(fù)責(zé)整個(gè)系統(tǒng)的工作頻率。有了心臟,人類(lèi)才得以正常活動(dòng),有了時(shí)鐘,系統(tǒng)才得以有條不紊的運(yùn)行。

在FPGA的設(shè)計(jì)當(dāng)中編寫(xiě)的RTL代碼,通過(guò)軟件工具可以生成人類(lèi)看不懂的bit_stream,也就是說(shuō)工程師每天的工作都是在編寫(xiě)FPGA的DNA,在生物學(xué)領(lǐng)域,我相信大多數(shù)的科學(xué)家畢生都在做著解讀‘人類(lèi)天書(shū)’DNA的工作吧。這樣一一類(lèi)比下來(lái)感覺(jué)FPGA的開(kāi)發(fā)就像是在造人一樣,頓時(shí)感覺(jué)代碼都不枯燥了。

首款 FPGA,即賽靈思 XC2064,只包含 64 個(gè)邏輯模塊,每個(gè)模塊含有兩個(gè) 3 輸入查找表 (LUT) 和一個(gè)寄存器。按照現(xiàn)在的計(jì)算,該器件有 64 個(gè)邏輯單元——不足 1000 個(gè)邏輯門(mén)。盡管容量很小,XC2064 晶片的尺寸卻非常大,比當(dāng)時(shí)的微處理器還要大;而且采用 2.5 微米工藝技術(shù)勉強(qiáng)能制造出這種器件。但隨著IC制造工藝的發(fā)展,F(xiàn)PGA也迅速發(fā)展,資源爆炸式增長(zhǎng),ZYNQ系列的Z-7100的邏輯單元已經(jīng)到了444k。

與FPGA同為PLD的還有CPLD,CPLD(Complex Programmable Logic Device),復(fù)雜可編程邏輯器件。CPLD由可編程邏輯的功能?chē)@一個(gè)可編程互連矩陣構(gòu)成,由固定長(zhǎng)度的金屬線實(shí)現(xiàn)邏輯單元之間的互連,并增加了I/O控制模塊的數(shù)量和功能。

CPLD的基本結(jié)構(gòu)可看成由可編程邏輯陣列(LAB),可編程I/O控制模塊和可編程內(nèi)部連線(PIA)等三部分組成。

可編程邏輯陣列(LAB):由若干個(gè)可編程邏輯宏單元(Logic Macro Cell,LMC)組成,LMC主要包括與陣列、或陣列、可編程觸發(fā)器和多路選擇器等電路,能獨(dú)立地配置為時(shí)序或組合工作方式。

FPGA由可編程邏輯塊(CLB),輸入/輸出模塊(IOB)及可編程互連資源(PIR)等三種可編程電路和一個(gè)SRAM結(jié)構(gòu)的配置存儲(chǔ)單元組成。CLB是實(shí)現(xiàn)邏輯功能的基本單元,他們通常規(guī)則排列成一個(gè)陣列,散布于整個(gè)芯片中。可編程輸入/輸出模塊(IOB)主要完成芯片上的邏輯與外部引腳的接口,它通常排列在芯片的四周。可編程互連資源(PIR)包括各種長(zhǎng)度的連線線段和一些可編程鏈接開(kāi)關(guān),他們將各個(gè)CLB之間或CLB與IOB之間以及IOB之間連接起來(lái),構(gòu)成特定功能的電路。

CLB主要由邏輯函數(shù)發(fā)生器,觸發(fā)器,數(shù)據(jù)選擇器等電路組成。邏輯函數(shù)發(fā)生器主要由查找表(Look Up Table)構(gòu)成。

查找表LUT實(shí)質(zhì)上是一個(gè)RAM,當(dāng)用戶描述了一個(gè)邏輯電路后,軟件會(huì)計(jì)算所有可能的結(jié)果,并寫(xiě)入RAM。每一個(gè)信號(hào)進(jìn)行邏輯運(yùn)算,就等于輸入一個(gè)地址進(jìn)行查表,找出地址對(duì)應(yīng)的內(nèi)容,輸出結(jié)果。這樣也大大加快了FPGA的運(yùn)算速度。

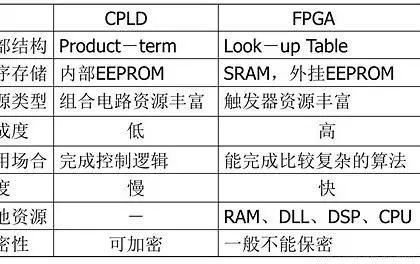

FPGA和CPLD的區(qū)別主要有以下幾點(diǎn):

(1) FPGA采用SRAM進(jìn)行功能配置,可重復(fù)編程,但系統(tǒng)掉電后,SRAM中的數(shù)據(jù)丟失,因此,需要在FPGA外加EPROM,將配置數(shù)據(jù)寫(xiě)入其中,系統(tǒng)每次上電自動(dòng)將數(shù)據(jù)引入SRAM中。CPLD器件一般采用EEPROM存儲(chǔ)技術(shù),可重復(fù)編程,并且系統(tǒng)掉電后,EEPROM中的數(shù)據(jù)不會(huì)丟失,適用于數(shù)據(jù)的保密。

(2)FPGA器件含有豐富的觸發(fā)器資源,易于實(shí)現(xiàn)時(shí)序邏輯,如果要求實(shí)現(xiàn)較復(fù)雜的組合電路,則需要幾個(gè)CLB結(jié)合起來(lái)實(shí)現(xiàn)。CPLD的與或陣列結(jié)構(gòu),更適用于實(shí)現(xiàn)大規(guī)模組合功能,但觸發(fā)器資源相對(duì)較少。

(3)FPGA是細(xì)顆粒度結(jié)構(gòu),CPLD是粗粒度結(jié)構(gòu)。FPGA內(nèi)部有豐富連線資源,CLB分塊較小,芯片利用率高。CPLD宏單元的與或陣列較大,通常不能完全被應(yīng)用,且宏單元之間的主要通過(guò)高速數(shù)據(jù)通道連接,其容量有限,限制了器件的靈活布線,因此,CPLD利用率較FPGA器件低。

(4)FPGA為非連續(xù)式布線,CPLD為連續(xù)式布線。FPGA器件每次編程時(shí)實(shí)現(xiàn)的邏輯功能一樣,但走的路線不同,因此延時(shí)不易控制,即時(shí)序延遲不可預(yù)測(cè)。CPLD每次布線路徑一樣,消除了分段式互連結(jié)構(gòu)在定時(shí)上的差異,并在邏輯單元之間提供快速且具有固定延時(shí)的通路,CPLD的延時(shí)小,且時(shí)序延遲可預(yù)測(cè)。CPLD比FPGA可工作在更高的頻率。

所以FPGA是什么?

Itcan beanything you want!

原文標(biāo)題:FPGA掃盲文

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605907 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131491

原文標(biāo)題:FPGA掃盲文

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

大多數(shù)FPGA的程序存儲(chǔ)器(FLASH)為什么都放在外面呢?FPGA的主要應(yīng)用

FPGA基礎(chǔ)知識(shí)及設(shè)計(jì)和執(zhí)行FPGA應(yīng)用所需的工具

點(diǎn)焊機(jī)的起源和發(fā)展

輝煌的FPGA帝國(guó)起源是什么?

輝煌的FPGA帝國(guó)起源是什么?

評(píng)論