傳統的流程將驗證留給實驗室樣機測試,或發生在設計的最后階段。然而在后期階段才對設計進行整改將明顯浪費成本和時間并且也沒有辦法對問題產生的原因進行根本性分析,或者尋找解決問題的方案。 這也讓傳統的仿真驗證成為了電子電路設計項目開發過程中的一個難以突破的瓶頸。加速評審的唯一選擇就是減少每個設計驗證的覆蓋率和次數。

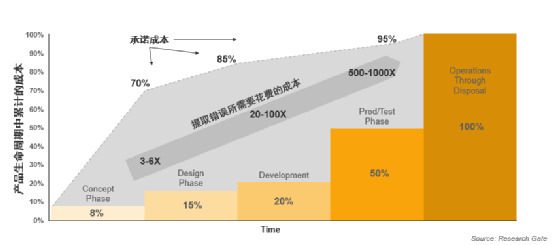

重新設計造成的成本隱藏在產品的整個生命周期之中,據Lifecycle Insights的報告顯示,平均每個項目會有2.9次的設計重制, 而平均每次設計重制,將會造成8.5天的項目延期,直接導致約44000美金的成本損失。除了這些確定的損失,產品生命周期中包含的潛在成本,例如后期的維護費用、品牌聲譽、問題管理費用等等,都可能給整個項目開發的累積更高的成本。而導致重新設計的原因主要是:對設計仿真分析覆蓋度不足,以及在人工評審時疏忽遺漏造成的。

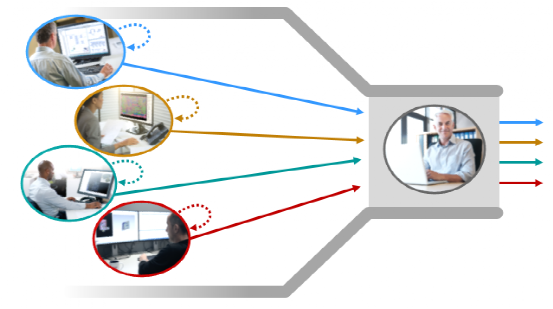

那么如何優化設計流程?設計工程師需要在將設計交付給分析專家之前進行多次的“內循環”,通過為分析專家“減負”來提高驗證的吞吐量。在整個工程項目中,讓仿真驗證來驅動設計的更迭,而不是僅僅通過經驗。

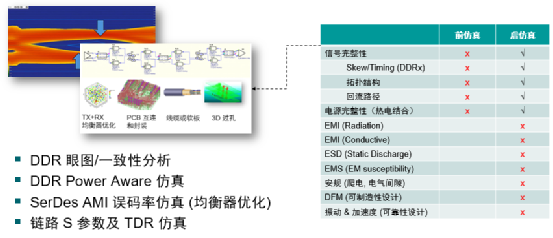

在傳統的驗證流程中,大多數公司僅對那些有明確目標的部分進行驗證,比如 DDR 總線、部分 SerDes 差分線,重要芯片的PDN 阻抗等。但將仿真局限在這些范圍中會讓許多同樣重要的問題被忽略,復雜設計中上千根的通用信號、電源網絡爬電效應、PDN信號回路形成的天線效應等都是傳統的仿真流程所不能覆蓋的。

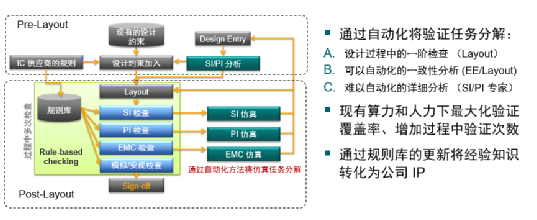

Siemens EDA 推薦使用混合驗證流程解決仿真覆蓋度和仿真效率的問題。通過自動化的手段將驗證的工作拆分成多個部分,分別由團隊中不同的工程師處理。通過自動化的平臺,工程師將能夠通過標準化的流程在設計過程中對項目進行高覆蓋度、快速、多次迭代的仿真或驗證,同時不會引入過多的學習成本。

如何從根本上優化仿真驗證的流程,是系統設計者的一大挑戰。

責任編輯:xj

原文標題:如何優化驗證的設計流程,減少設計驗證的覆蓋率和次數?

文章出處:【微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

-

仿真

+關注

關注

50文章

4123瀏覽量

133861 -

電子電路

+關注

關注

78文章

1225瀏覽量

66994

原文標題:如何優化驗證的設計流程,減少設計驗證的覆蓋率和次數?

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【書籍評測活動NO.54】典型電子電路設計與測試

電子電路中的地是什么?什么是數字地和模擬地

電子電路分析求解!!!

正業科技亮相2024泰國電子電路亞洲展

高頻電子線路和微波電子電路區別

電子電路開發者

中京電子亮相2024國際電子電路(上海)展覽會

電子電路仿真的意義和作用

E-Val Pro Plus有線驗證解決方案,功能升級,優化制藥流程,確保安全性和合規性!

功率電子電路中續流和換流的區別

fpga原型驗證流程

金絲球焊工藝參數影響性分析和優化驗證

如何優化驗證電子電路的設計流程

如何優化驗證電子電路的設計流程

評論