在學(xué)習(xí)ZYNQ嵌入式開發(fā)的過程中,正點(diǎn)原子的教程是采用SDK,而我下載的vivado2020.1已經(jīng)變成了vitis,所以寫一這篇博客,方便后續(xù)查閱。

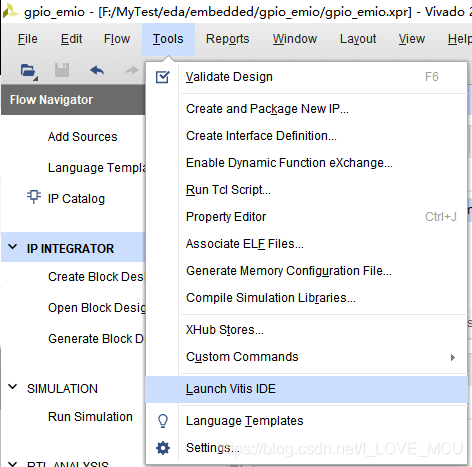

找到vitis

vivado->tools->launch vitis ide

如果打開失敗,說明沒有安裝vitis,先進(jìn)行安裝

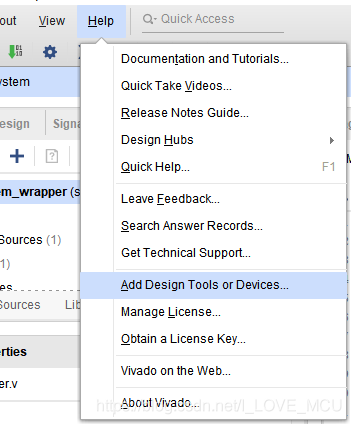

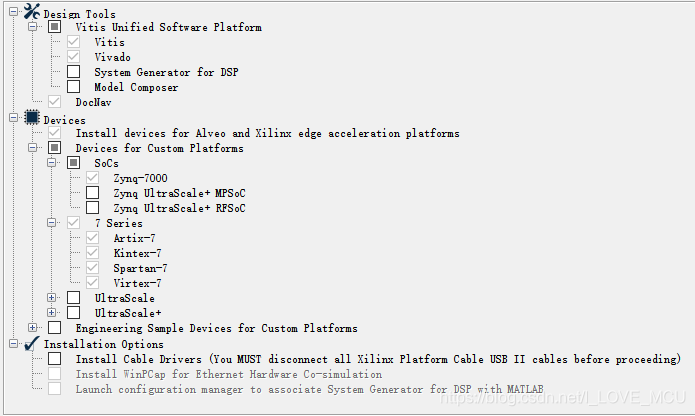

安裝vitis

vivado->help->Add Design Tools or Devices…

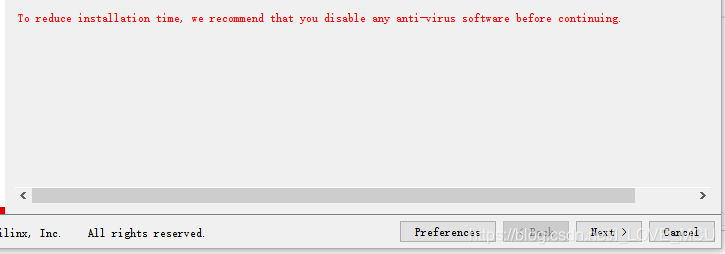

退出殺軟來加速安裝,下一步,登錄,

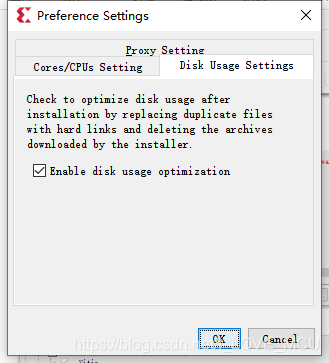

建議點(diǎn)擊preference,關(guān)閉optimize disk usage,否則安裝結(jié)束后可能會卡在optimize disk usage上。有人優(yōu)化了一晚上沒結(jié)束,不得已重裝。我晚上打開安裝程序,第二天發(fā)現(xiàn)電腦已經(jīng)睡眠了,程序卡在optimize disk usage上,等了半上午,快失去耐心得時候安裝完成了。

我已經(jīng)安裝完成了,所以是灰色狀態(tài)。

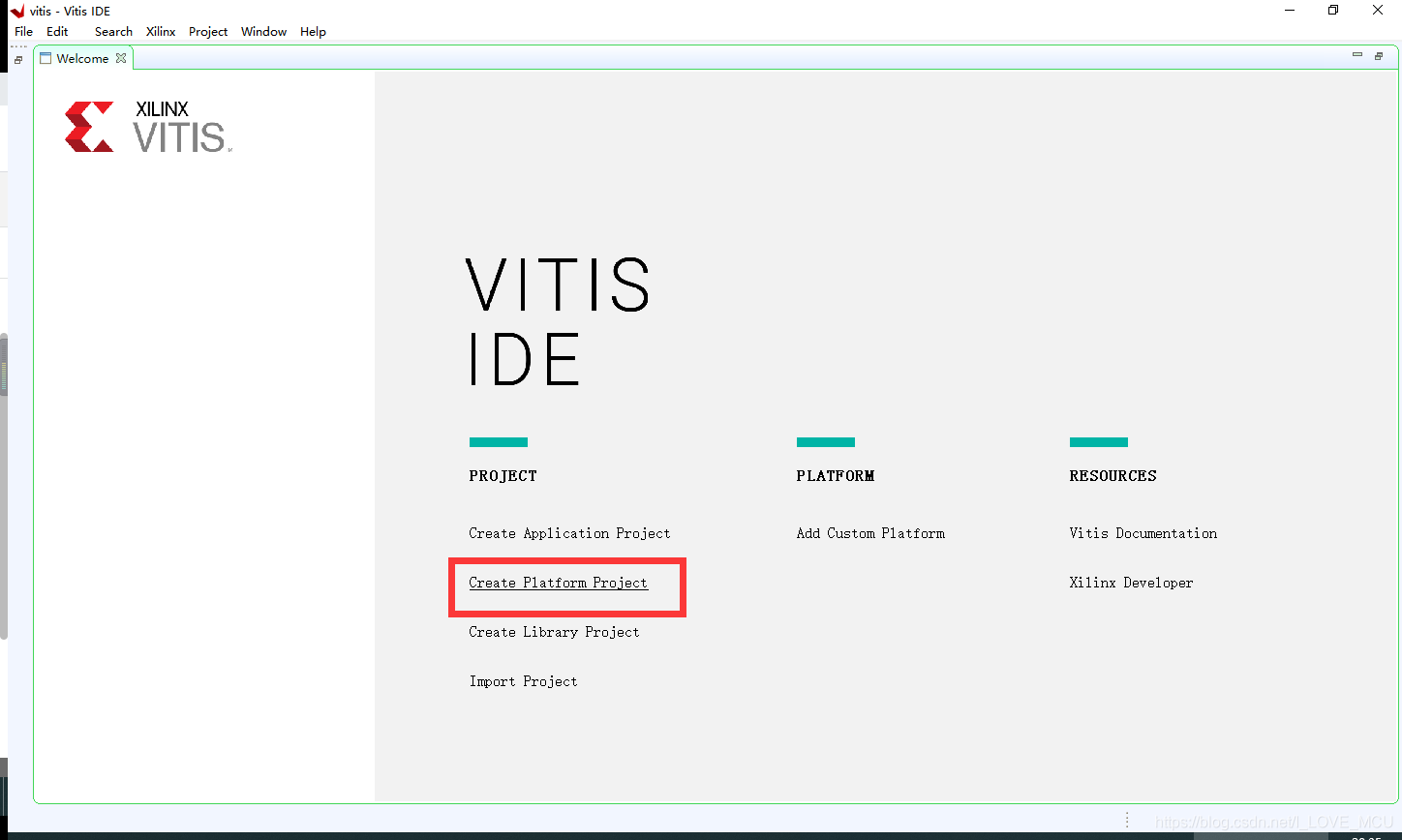

創(chuàng)建platform工程

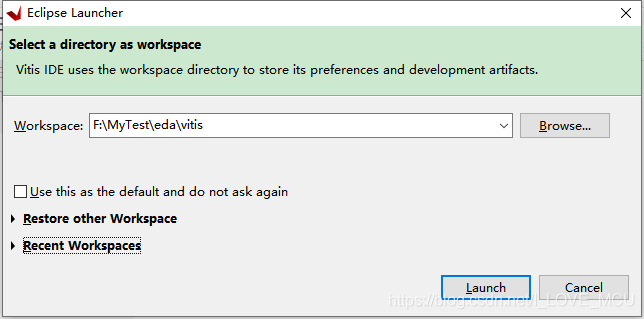

vivado->tools->launch vitis ide

選擇工作路徑

先創(chuàng)建一個 platform project,填寫工程名

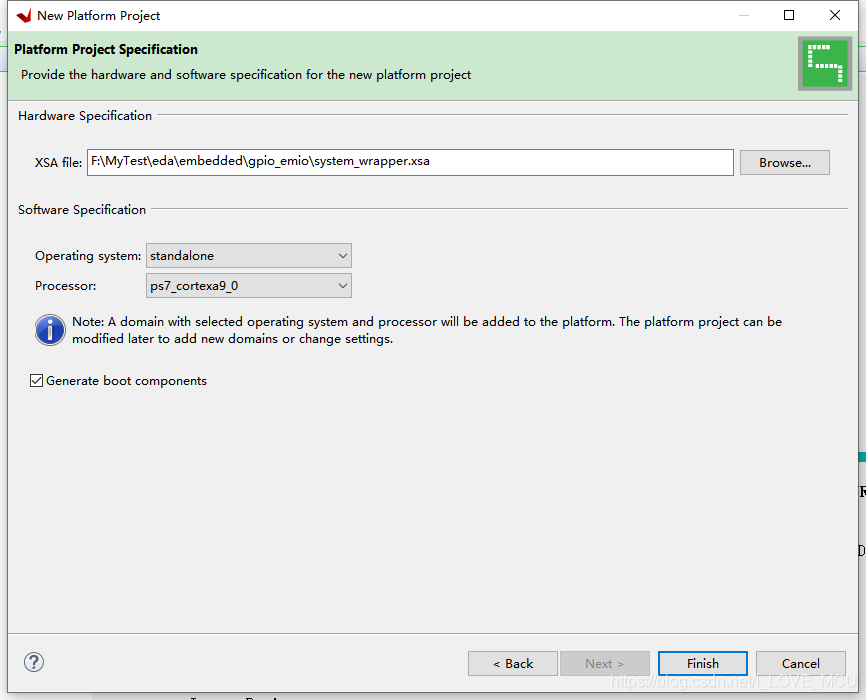

選擇xsa文件路徑

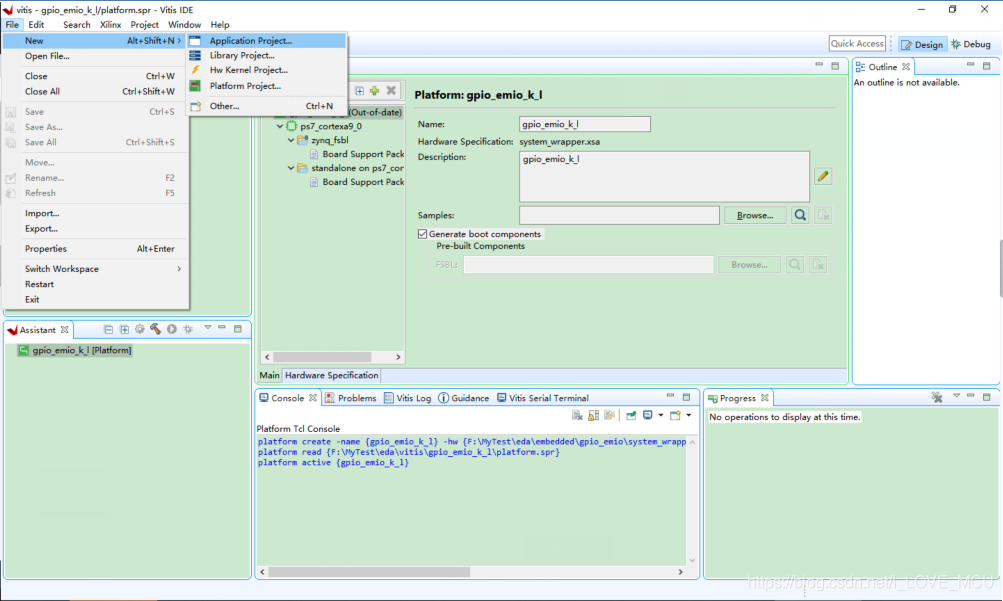

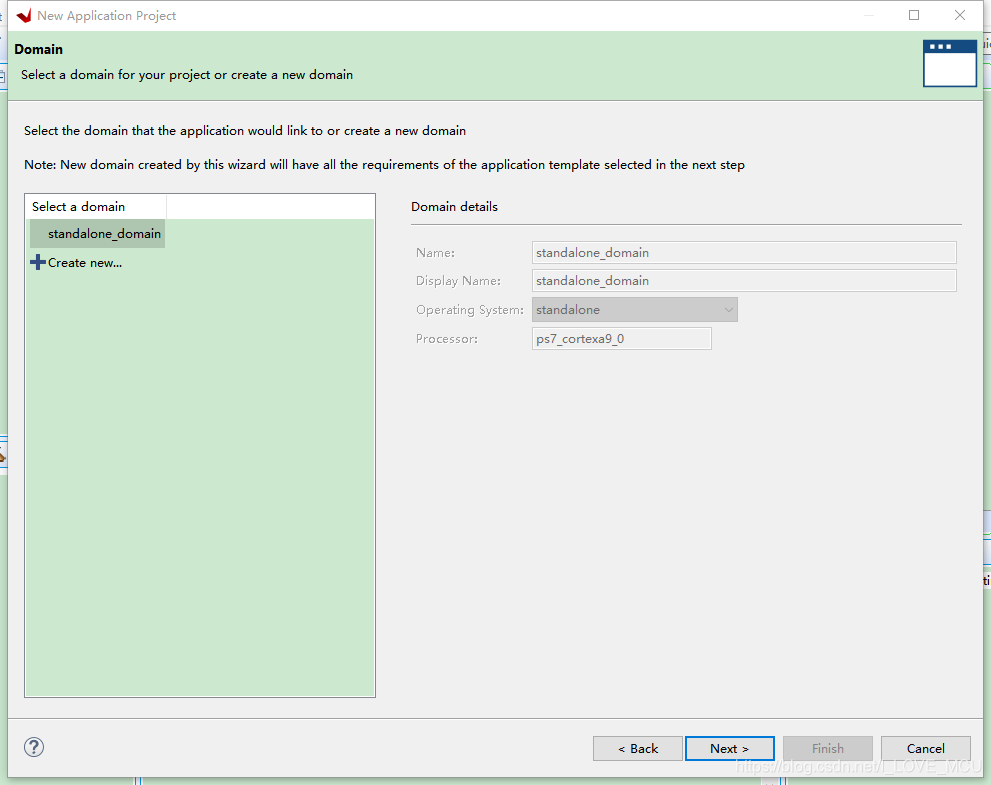

創(chuàng)建application工程

新建一個應(yīng)用工程

選擇剛剛創(chuàng)建的平臺

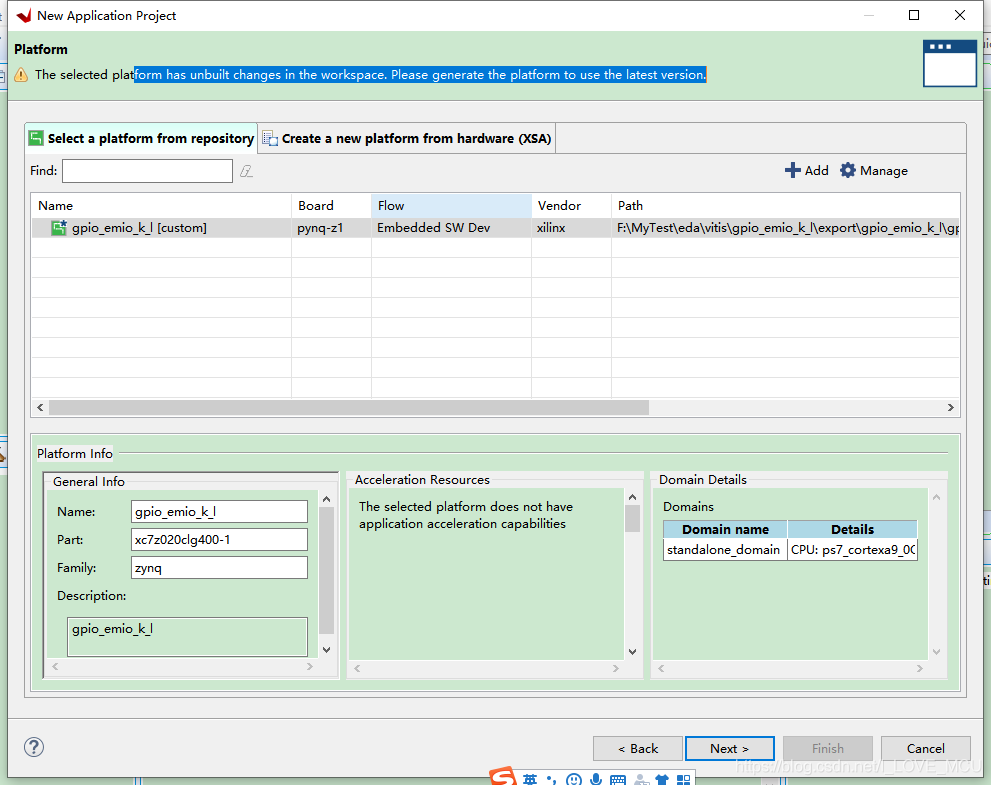

填寫應(yīng)用工程名

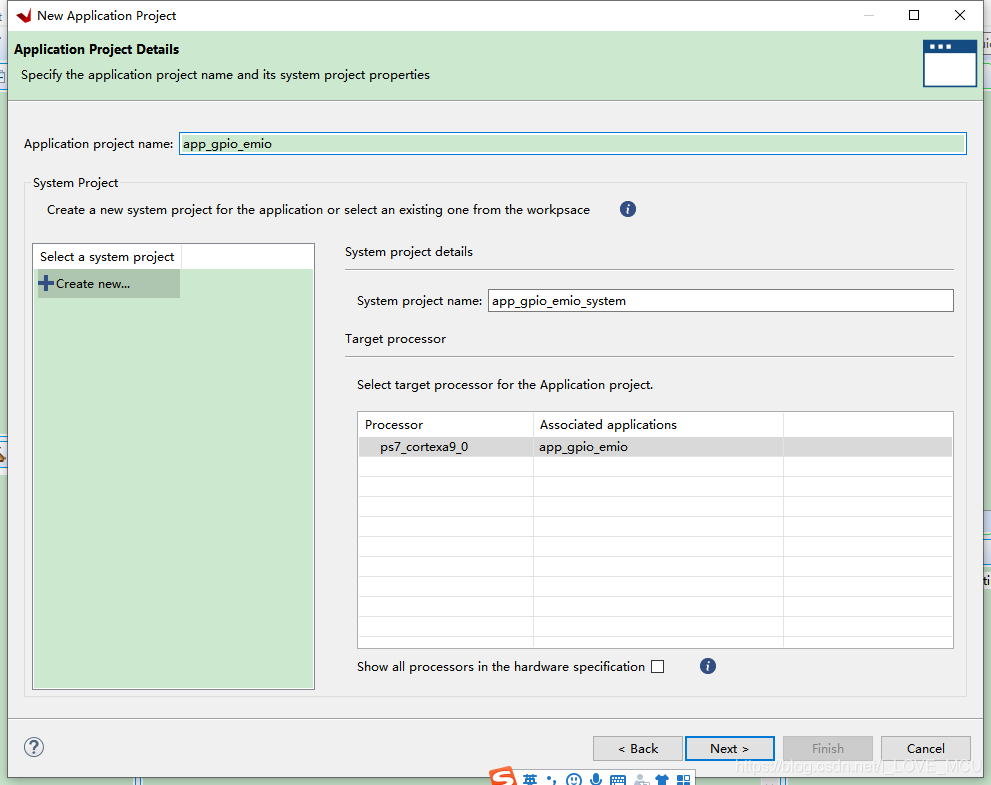

默認(rèn)、

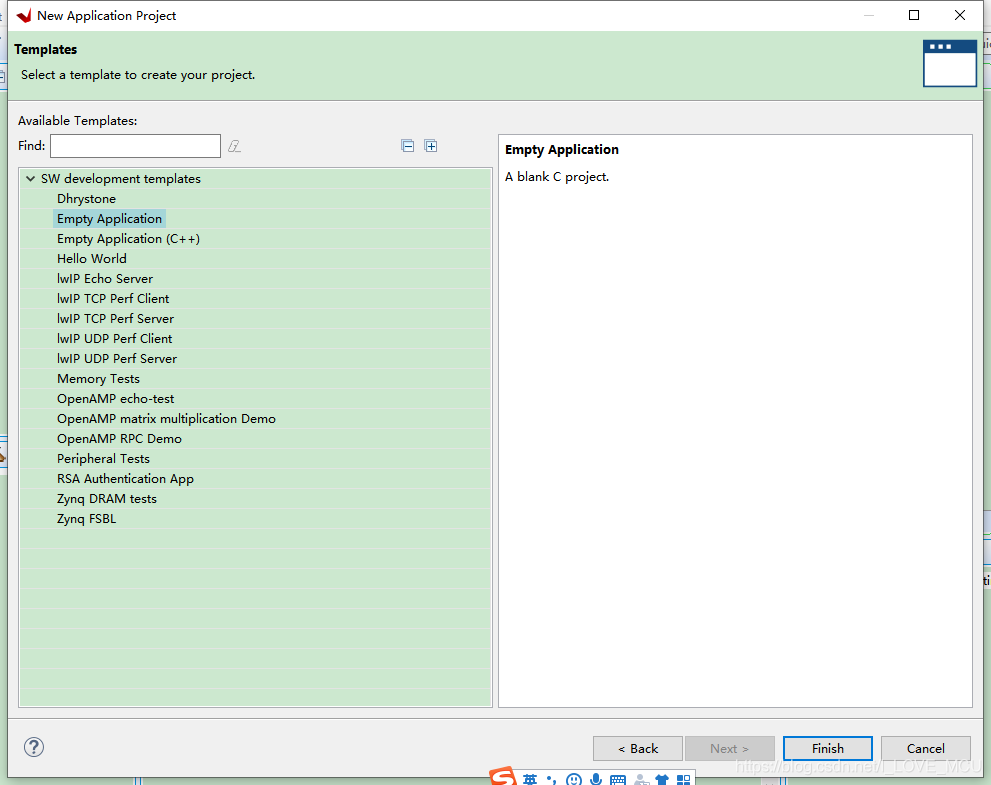

選擇空白C工程

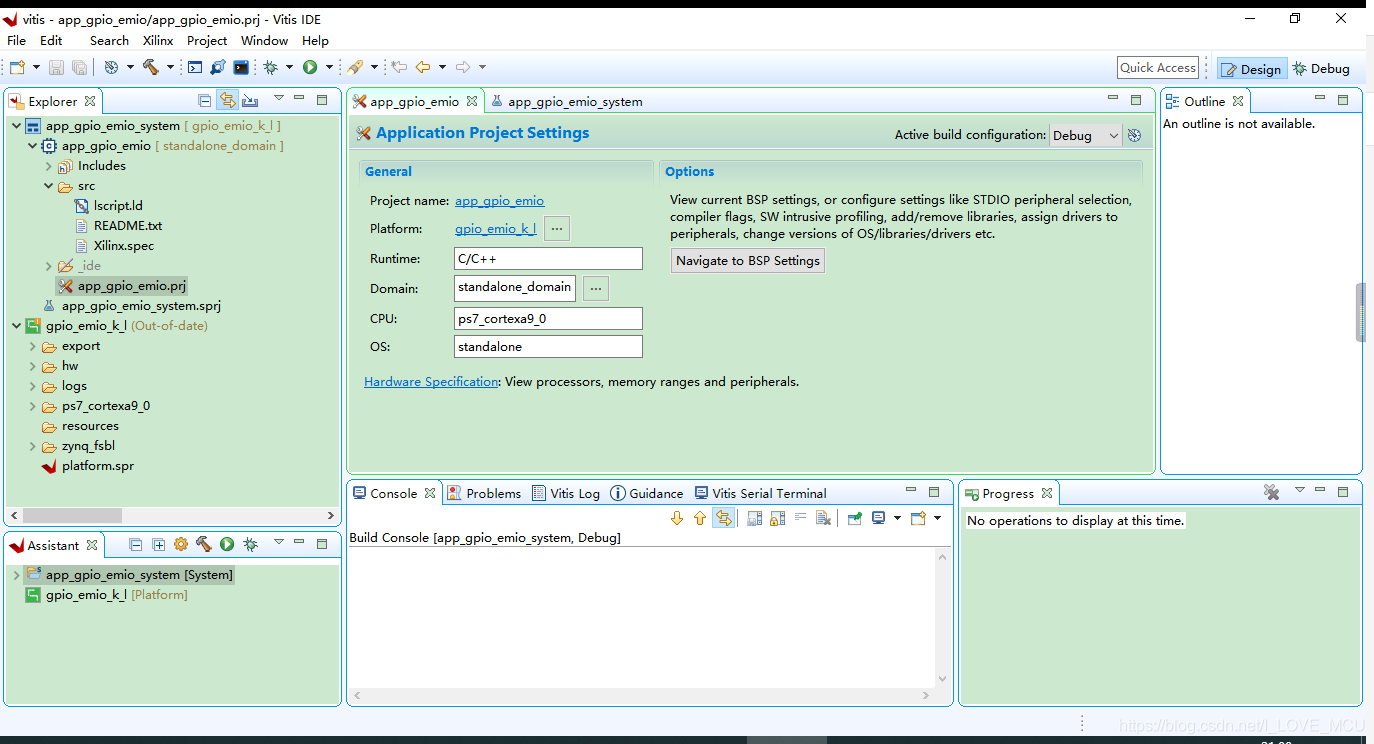

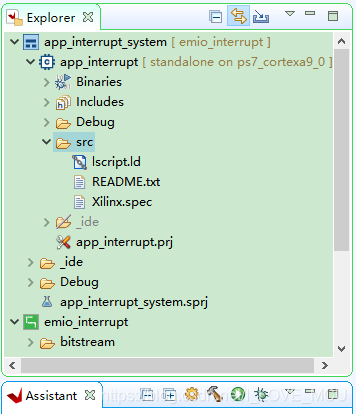

結(jié)束工程創(chuàng)建

找例程

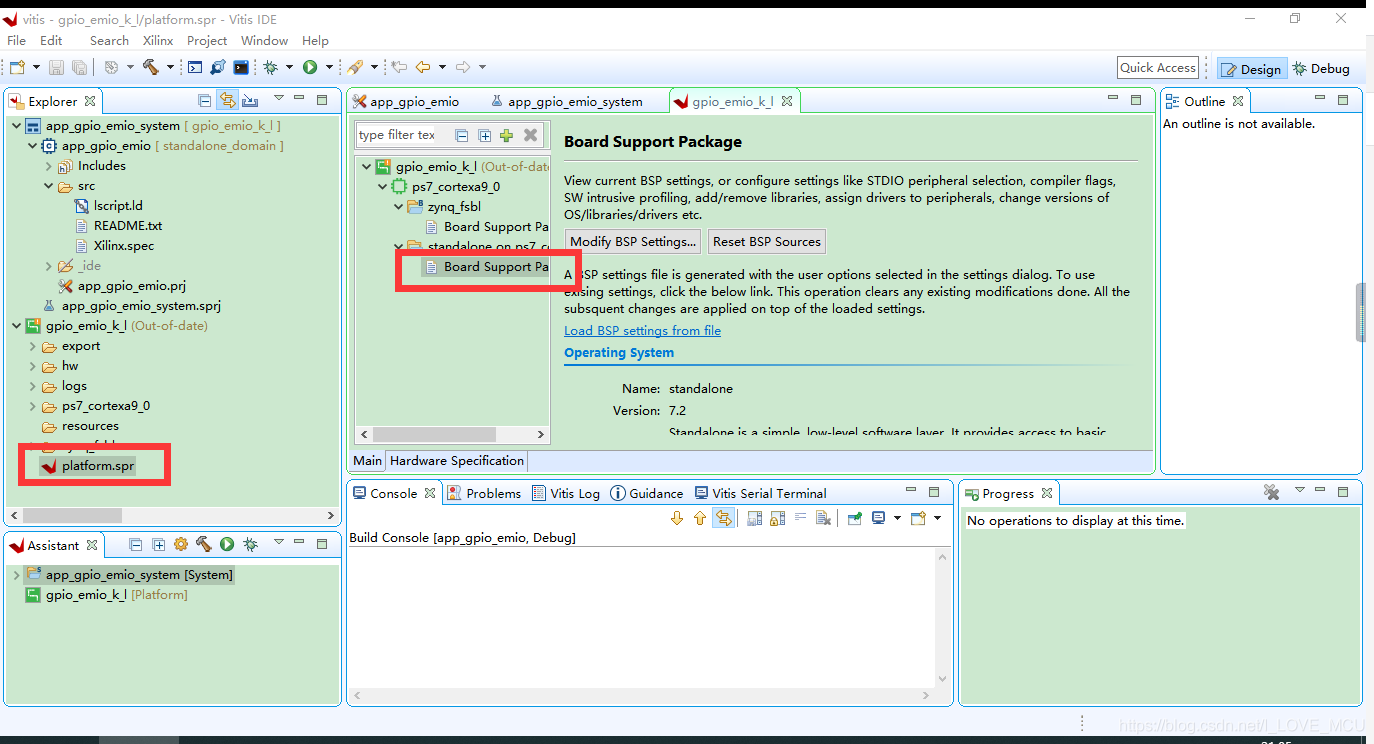

explorer->platform工程名->platform.spr->board support package

board support package點(diǎn)擊一次顯示

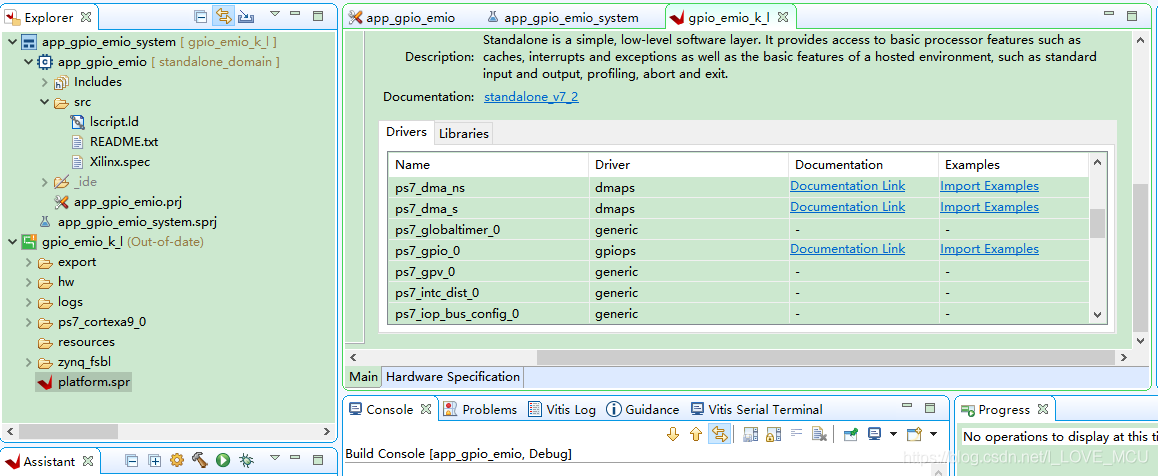

board support package再點(diǎn)擊一次,并拖動滾動條找到GPIO部分

可以查看文檔documentation,也可以加載例程

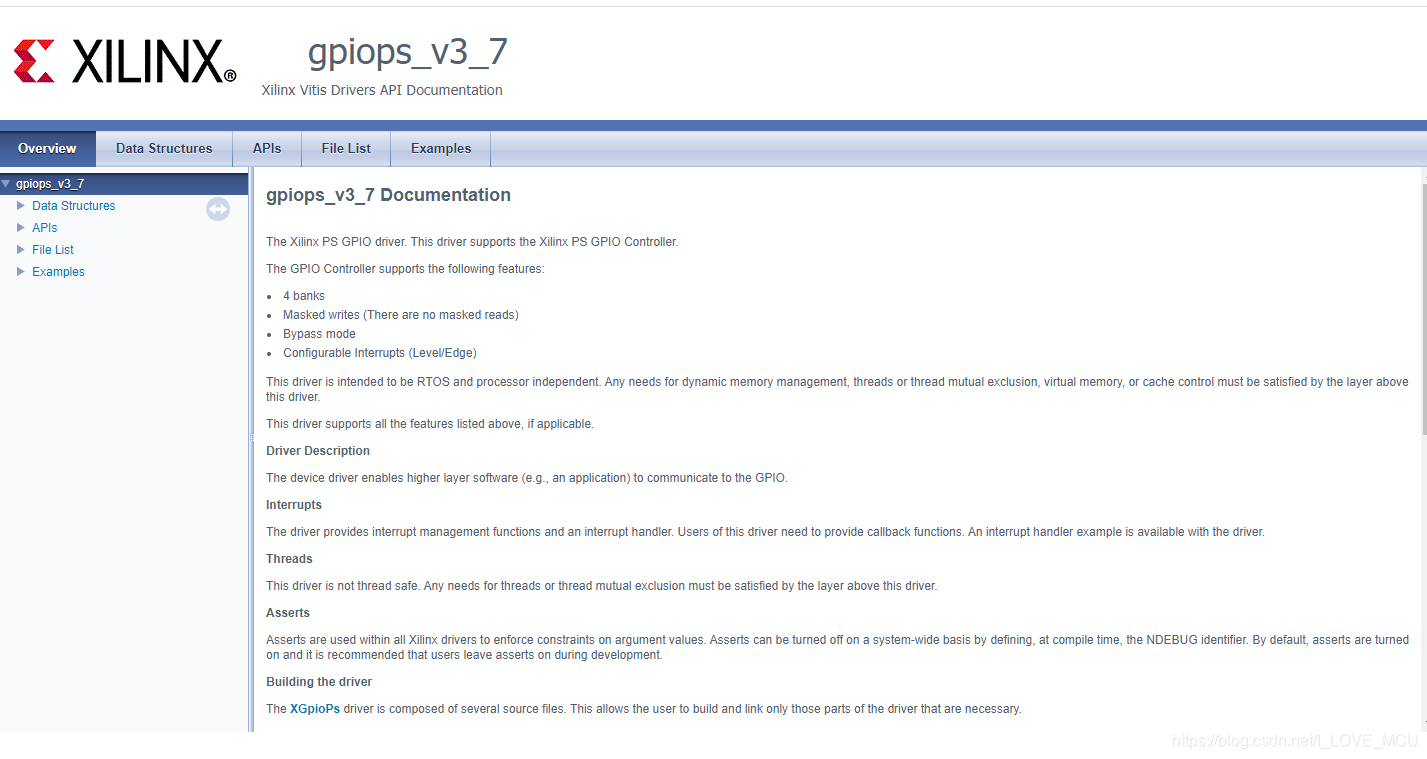

點(diǎn)擊 Documentation 將在瀏覽器窗口打開 GPIO 的 API 文檔,里面有關(guān)于 GPIO 的詳細(xì)信息

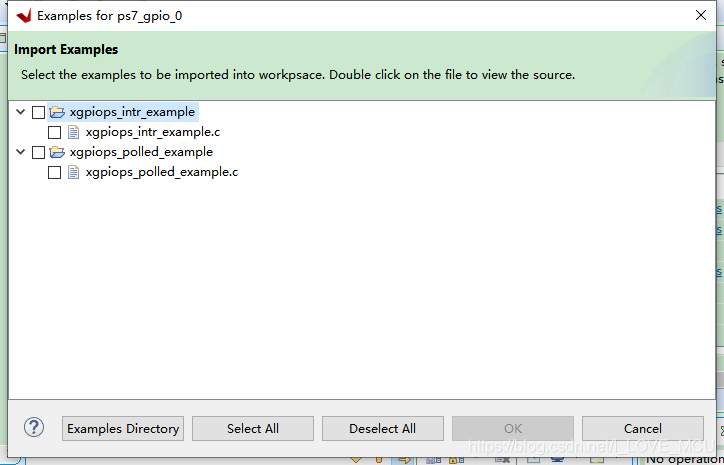

點(diǎn)擊 Import Examples,會彈出下圖所示的導(dǎo)入示例界面

這兩個示例的介紹可以在剛才打開的 API 文檔中看到。

xgpiops_intr_example.c 包含有關(guān)如何直接使用 XGpiops 驅(qū)動程序的示例。此示例顯示了中斷模式下驅(qū)動程序的用法,并使用 GPIO 的中斷功能檢測按鈕事件,根據(jù)輸入控制 LED 輸出。

xgpiops_polled_example.c同樣包含有關(guān)如何直接使用 XGpiops 驅(qū)動程序的示例。此示例提供了用于讀取/寫入各個引腳的 API 的用法。

選擇 xgpiops_polled_example 示例

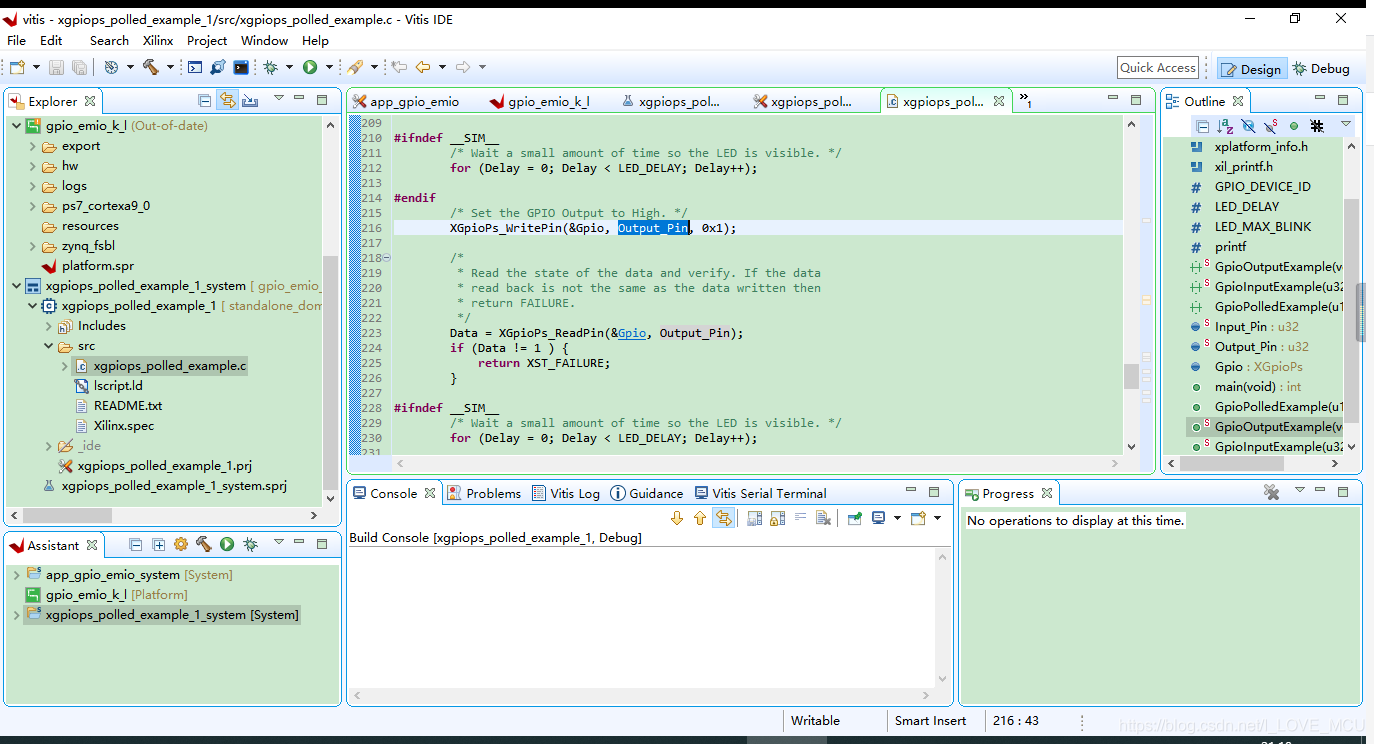

在 Project Explorer 中,新增了 pio_mio_bsp_xgpiops_polled_example_1 目錄,我們打開其 src 目錄下的 xgpiops_polled_example.c 文件。

代碼沒看懂,先放放,刪了,寫其他的吧。

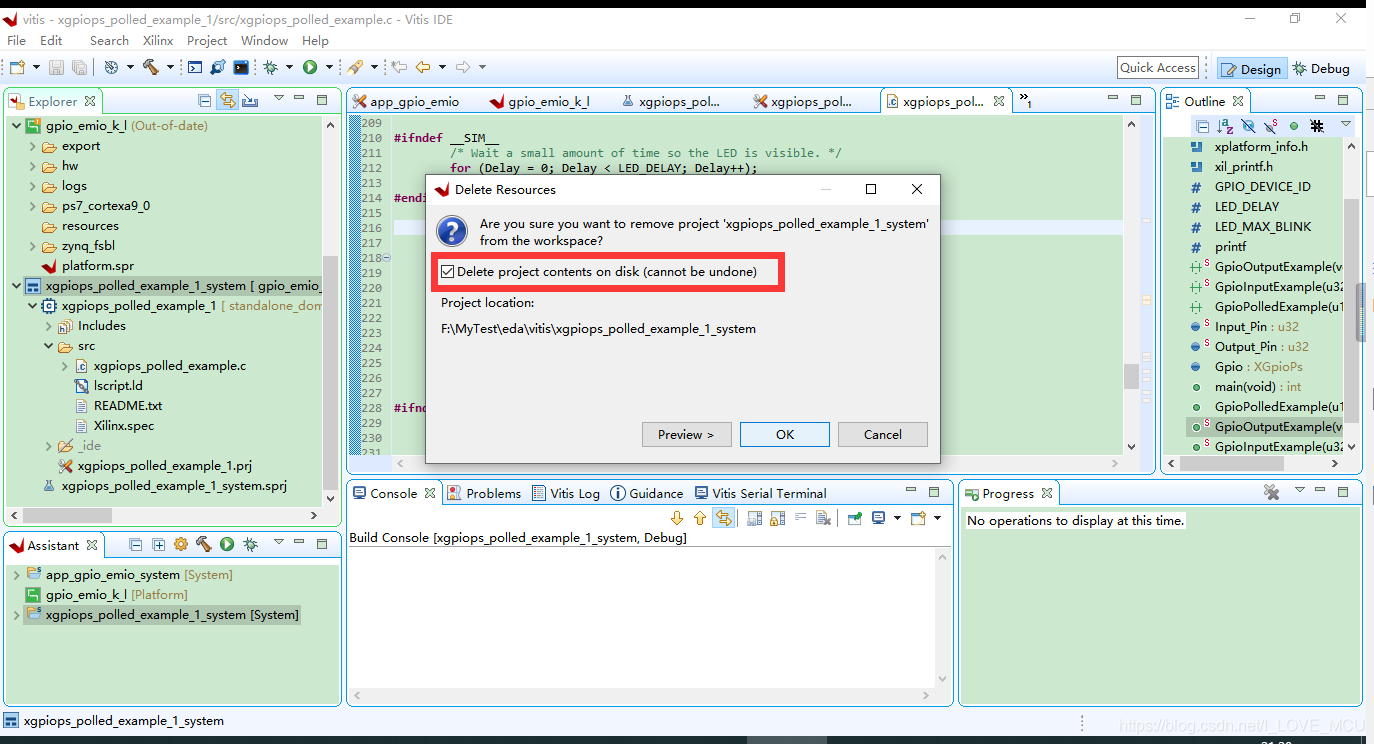

刪除應(yīng)用工程,連本地文件一起刪除

之前寫了一半,但是突然有感覺了,就只顧著寫代碼了,教程沒有寫完。第二天接著前面的進(jìn)度寫了,工程名不太一樣,但過程都是一樣的。

編寫源碼

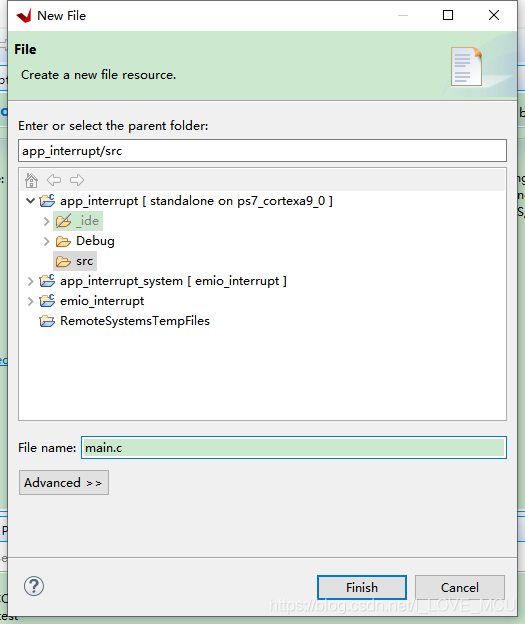

src右鍵,新建文件

文件名main.c

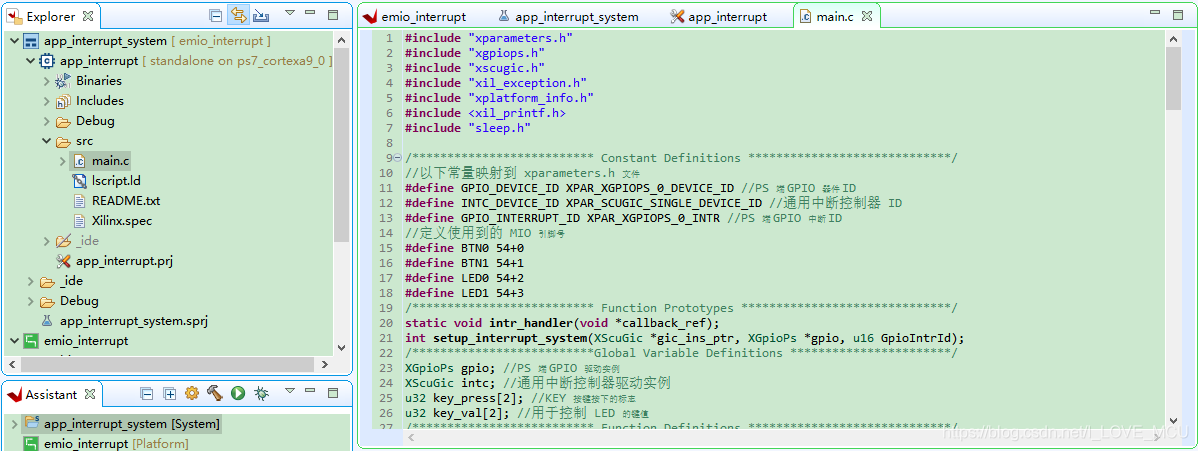

寫代碼,我直接粘貼現(xiàn)成的代碼了

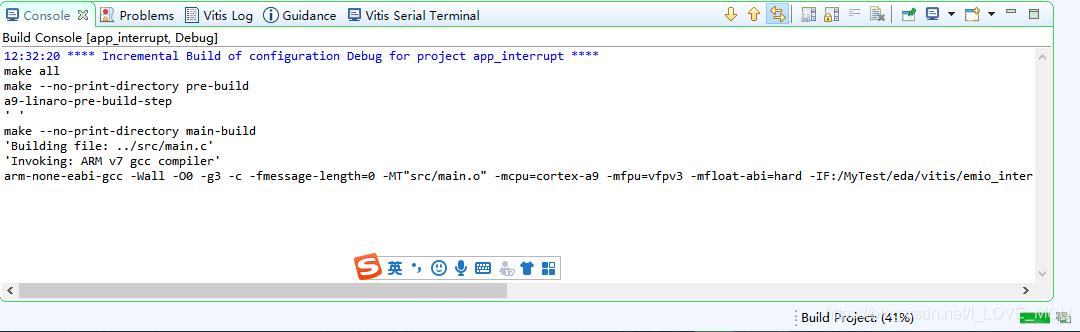

編譯工程,點(diǎn)擊一下應(yīng)用工程名

再點(diǎn)擊Project->build project

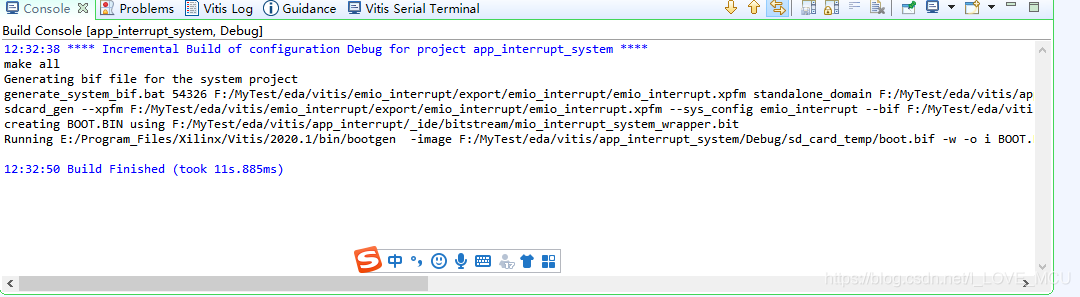

等右下角進(jìn)度條跑完,build finished

下載程序

如果使用到了PL資源,需要加載比特流,反之不用。

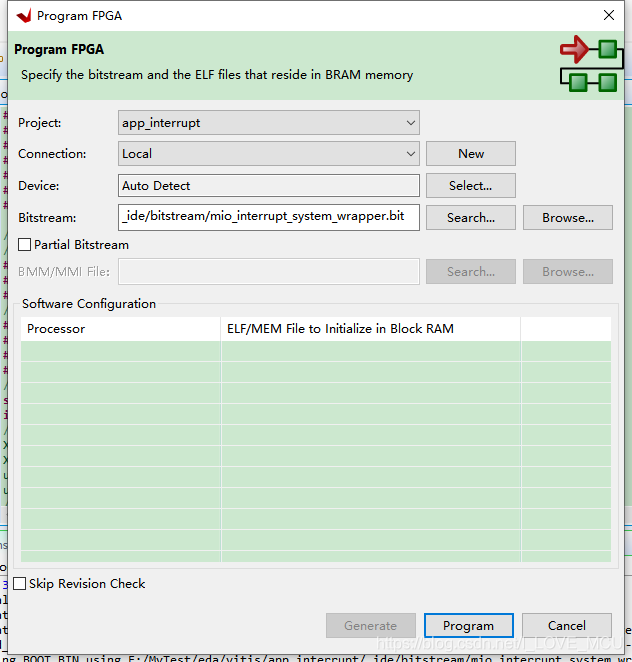

因為本次實(shí)驗使用了 PL 內(nèi)的資源,因此我們在下載軟件編譯生成的 elf 文件之前,需要先下載硬件設(shè)計過程中生成的 bitstream 文件,對 PL 部分進(jìn)行配置。

點(diǎn)擊“ Xilinx-> Program FPGA

點(diǎn)擊右下角的“Program”

一段進(jìn)度條過去了

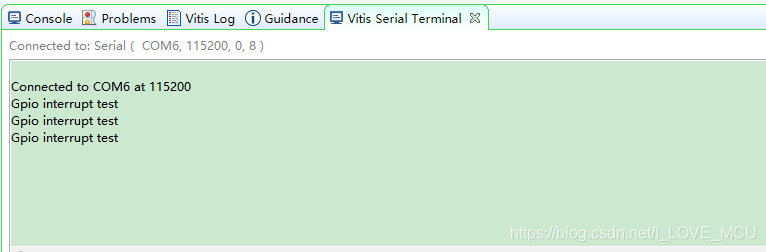

配置 PL 完成后, 接下來我們要下載軟件程序。在應(yīng)用工程 上右擊,選擇“Run As->launch hardware

一段進(jìn)度條過去了

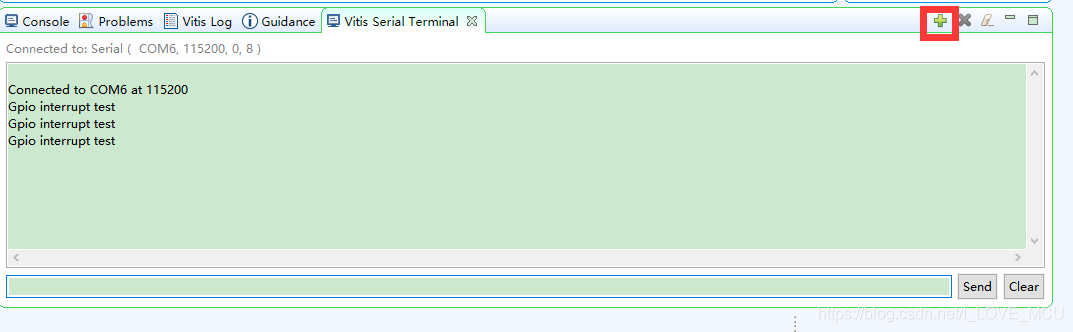

程序就已經(jīng)運(yùn)行了,可以從串口的打印結(jié)果上看到。

沒了

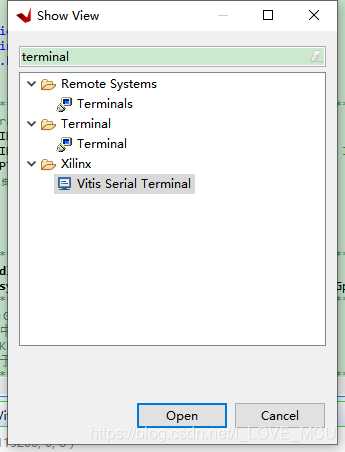

插入一下,串口界面可以在windows->show view

搜索terminal

單機(jī)右上角+連接相應(yīng)串口

參考文獻(xiàn)

正點(diǎn)原子ZYNQ嵌入式開發(fā)

Xilinx vitis學(xué)習(xí)教程:ZYNQ之Hello world(1)

審核編輯 黃昊宇

-

教程

+關(guān)注

關(guān)注

25文章

265瀏覽量

54214 -

Vitis

+關(guān)注

關(guān)注

0文章

147瀏覽量

7493

發(fā)布評論請先 登錄

相關(guān)推薦

使用AMD Vitis進(jìn)行嵌入式設(shè)計開發(fā)用戶指南

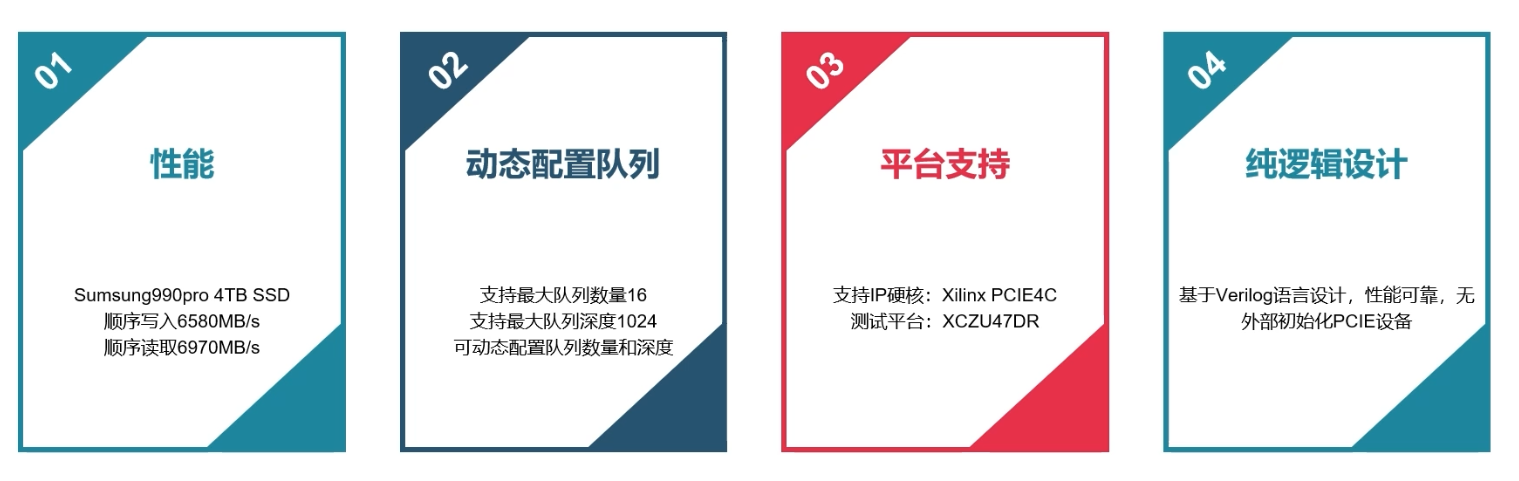

NVMe IP over PCIe4.0:高速,超高速!

全新AMD Vitis統(tǒng)一軟件平臺2024.2版本發(fā)布

AMD Vitis Unified Software Platform 2024.2發(fā)布

U50的AMD Vivado Design Tool flow設(shè)置

AMD Vitis統(tǒng)一軟件平臺2024.1全新發(fā)布

FPGA無芯片HDMI接入方案及源碼

一個更適合工程師和研究僧的FPGA提升課程

AMD Vitis?設(shè)計工具中的Libraries新功能介紹

在Windows 10上創(chuàng)建并運(yùn)行AMD Vitis?視覺庫示例

如何使用Vitis自帶的LWIP模板進(jìn)行PS端千兆以太網(wǎng)TCP通信?

AMD Vitis? Embedded嵌入式軟件開發(fā)套件的功能和特性概述

FPGA版通用圖形處理架構(gòu)創(chuàng)新解決方案

Vitis的使用教程

Vitis的使用教程

評論