作者:ALINX

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

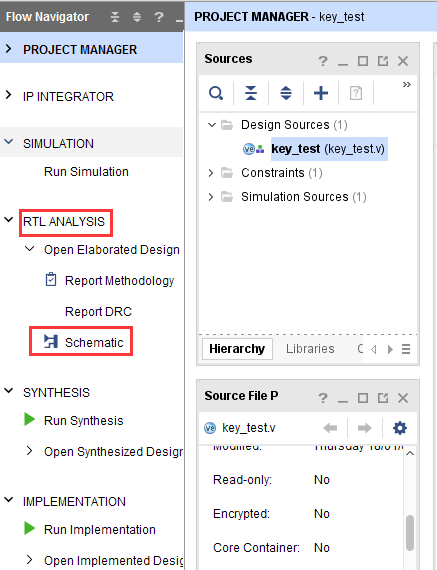

按鍵是FPGA設計當中最常用也是最簡單的外設,本章通過按鍵檢測實驗,檢測開發板的按鍵功能是否正常,并了解硬件描述語言和FPGA的具體關系,學習Vivado RTL ANALYSIS的使用。

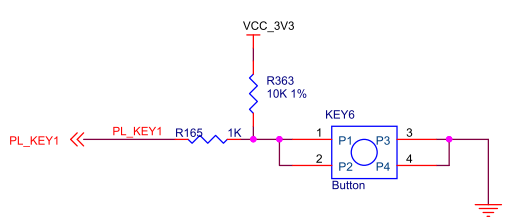

1.按鍵硬件電路

開發板按鍵部分電路

從圖中可以看到,電路的按鍵松開時是高電平,按下時是低電平。

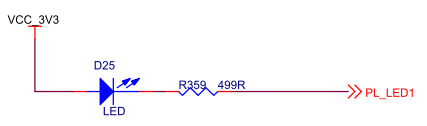

開發板LED部分電路

而LED部分,高電平滅,低電平亮

2. 程序設計

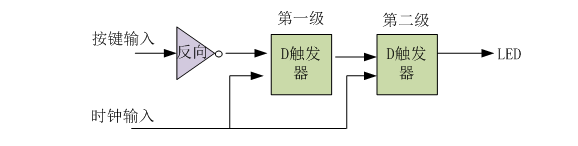

這個程序沒有設計的很復雜,通過簡單的硬件描述語言看透硬件描述語言和FPGA硬件的聯系。首先我們將按鍵輸入經過一個非門后再經過2組D觸發器。經過D觸發器的信號,會在D觸發器時鐘輸入的上升沿鎖存然后再送到輸出。

在進行硬件描述語言編碼之前,我們已經把硬件構建完成,這是一個正常的開發流程。有了硬件設計思路無論是通過畫圖還是通過Verilog HDL、VHDL都能完成設計,根據設計的復雜程序和對某種語言的熟悉程序來選擇工具。

3. 創建Vivado工程

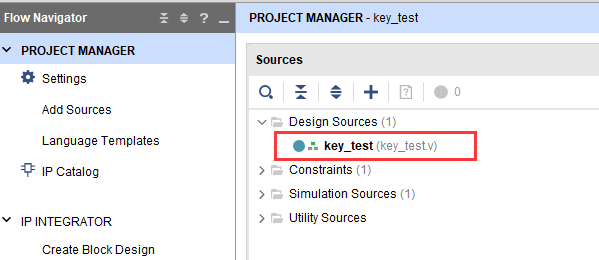

3.1 首先建立按鍵的測試工程,添加verilog測試代碼,完成編譯分配管腳等流程。

`timescale1ns/1ps

module key_test

(

input clk,//system clock 25Mhz on board

input[3:0] key,//input four key signal,when the keydown,the value is 0

output[3:0] led //LED display ,when the siganl low,LED lighten

);

reg[3:0] led_r;//define the first stage register , generate four D Flip-flop

reg[3:0] led_r1;//define the second stage register ,generate four D Flip-flop

always@(posedge clk)

begin

led_r <= key;//first stage latched data

end

always@(posedge clk)

begin

led_r1 <= led_r;//second stage latched data

end

assign led = led_r1;

endmodule<

3.2 我們可以使用RTL ANALYSIS工具查看設計

3.3 分析RTL圖,可以看出兩級D觸發器,和預期設計一致。

4. 板上驗證

Bit文件下載到開發板以后,開發板上的"PL LED"處于亮狀態,按鍵“PL KEY1”按下“PL LED1”滅。

審核編輯:何安

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604340

發布評論請先 登錄

相關推薦

FPGA編程語言的入門教程

PLC編程語言和C語言的區別

FPGA基礎知識學習

FPGA學習資料分享

fpga是用c語言還是verilog

fpga語言是什么?fpga語言與c語言的區別

fpga三種編程語言

VHDL語言快速入門指南

硬件描述語言和FPGA的具體關系

硬件描述語言和FPGA的具體關系

評論