導讀:芯片產業已經意識到,依循摩爾定律的工藝微縮速度已經趨緩,而產業界似乎不愿意面對芯片設計即將發生的巨變──從工藝到封裝技術的轉變

消費類電子產品和移動通信設備的一個重要趨勢是朝著更緊湊、更便攜的方向發展。今天的用戶要求更多功能、更高性能、更高速度和更小尺寸的解決方案;而軟件系統和數以十億計的聯網設備正在迅速形成一個巨大的物聯網(IoT)。 所有這些力量都在推動半導體公司開發新的先進集成電路(IC)封裝技術,以便以日益小型化的封裝提供更高的硅集成度。過去十年,新型封裝技術不斷涌現,如扇出式晶圓級封裝(FOWLP)、堆疊式IC封裝和復雜系統級封裝(system in package,SiP),以及封裝基板、倒裝芯片互連和硅通孔等,技術進步明顯。 所有這些進步使得IC封裝密度顯著提高,并為電子產品的研發打開了新的機會。讓我們來看看IC封裝行業的最新技術和市場趨勢,以及最先進的封裝和解決方案對于開發尖端產品和保持技術領先有什么重要意義。

封裝與摩爾定律息息相關

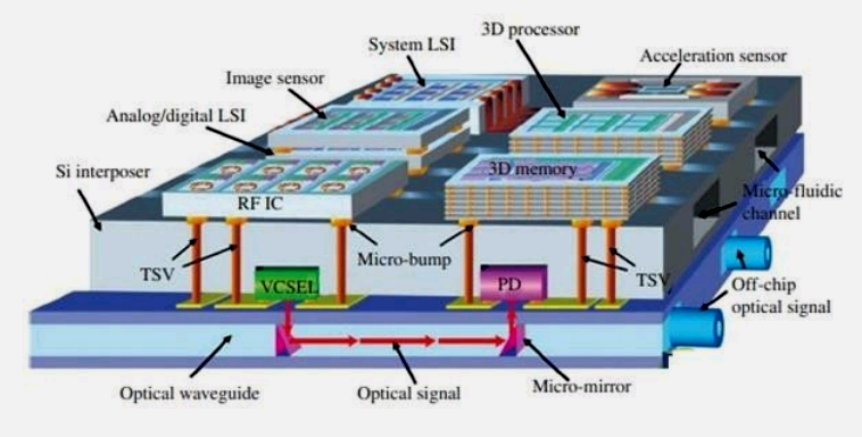

摩爾定律是一種成功的經驗預測,無非是讓IC中晶體管的密度每兩年翻一番。主要由于柵極長度收縮的減緩,晶體管的集成密度在2D處受到了限制,那么,人們就開始用3D繼續推進集成密度。作為3D芯片的堆疊式存儲器就是一個例子,相同技術的多層堆疊在一起,進一步增加了集成密度。 為什么芯片制造一直在追求先進IC封裝?一個突出目的是為了“超越摩爾定律(Moore than Moore)”。當芯片擴展在每個節點變得越來越困難和昂貴的時候,工程師們只能將多個芯片放入先進封裝中,作為芯片擴展的替代方案。 幾十年來,半導體加工技術穩步地將特征尺寸從幾十微米降到幾納米,有效地使每18個月組件密度翻了一番。然而,與此同時,設計和制造成本上升,臨界利潤率收窄,許多其他挑戰似乎阻礙了進一步的進展。此外,單個芯片中晶體管密度的增加在將芯片連接在一起時產生了問題,例如限制了I/O引腳數和芯片到芯片互連的速度。 事實證明,這些限制在人工智能(AI)邊緣和云系統等需要大量高帶寬內存的應用中問題尤其明顯。為了解決這些問題并繼續提高組件密度,行業開發了幾種先進封裝技術,將多個芯片在一個緊湊、高性能的封裝中互連,而封裝則作為單個組件在板上運行。

市場需要先進IC封裝

對于許多應用來說,摩爾定律已不再具有成本效益,尤其是對于異構函數的集成。“超越摩爾”,如多芯片模塊(MCM)和SiP已經成為將大量邏輯和存儲器、模擬、MEMS等集成到(子)系統解決方案中的替代方案。然而,這些方法過去和現在都是針對特定客戶的,且需要花費大量的開發時間和成本。 所謂“超越摩爾”指的是功能密度的增加,即將多種技術集成到一個復合器件中。這可能包括芯片和/或封裝的堆疊;使用多種半導體材料和各種電子布線技術,如球柵陣列(BGA)、硅通孔(TSV)、中間層和引線鍵合。一個超越摩爾的器件可以通過異構集成將來自不同前道制造節點的邏輯、內存、傳感器和天線集成到一個單獨的封裝中。 利用先進IC封裝“超越摩爾”的方法有很多,這里介紹幾個主要的技術。

SiP的普及確保IoT增長

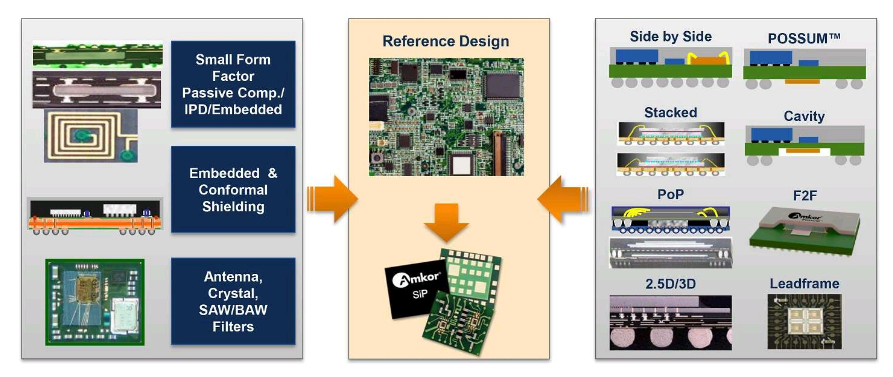

許多人認為IoT是第三波技術浪潮,80年代末90年代初的個人電腦熱潮是第一波,手機是第二波。在第三波中,工程師們在前兩次浪潮的經驗和基礎上,使日常瑣事更加緊密相連。 市場調研機構Strategy Analytics估算,到2023年,以智能家居為代表的全球IoT市場規模將達1570億美元,半導體增量機會明顯,封裝技術將在未來系統開發中起到推波助瀾的作用。 Amkor Technology高級產品營銷和業務開發高級總監Vik Chaudhry認為,IoT的爆發推動了SiP封裝的普及,使之成為集成IoT解決方案的流行方式,因為它為制造商提供了機會,可以非常快速地組合不同技術,并通過使用“現成”組件來降低成本。IoT解決方案的尺寸也可以通過集成封裝而減小,從而進一步降低成本。

他解釋說:“IoT封裝要求低成本、良好的功耗(低功耗的硅部分)并支持多種RF標準(如BTLE、Wi-Fi或ZigBee),而且封裝具有良好RF屏蔽。當使用傳感器時,基于腔的解決方案很受歡迎,特別是當有感知傳遞要求時,例如麥克風。IoT封裝還必須生產就緒,因為上市時間的限制,等待新的定制封裝通常是不可行的。最后,不管解決方案是分立的還是集成的,占用空間必須很小。” 對IoT應用來說,SiP是將傳感器、嵌入式處理器和RF連接集成到一個小尺寸的完美方式,即傳感器融合,而且,這也給制造商提供了一個很快將不同技術結合起來的機會,而無需花費大量資金購買新的掩模組。除了快速上市外,SiP方法還允許制造商使用現成組件來構建解決方案,因為所有構建塊都已經以產品形式存在,所以對工程師來說,重新排列組合就可以輕松獲得天線位置、功耗等方面的最佳性能;還可以利用封裝集成將IoT解決方案的尺寸減少40%。 SiP技術的優勢在于:

融合多種技術

能夠在一個封裝中集成多種技術和組件,例如組合MEMS和CMOS。這種組合對于傳統IC是不可能的。雖然MEMS和CMOS器件有許多相似之處,但也有一些關鍵區別。首先是需要一種方法將感知傳遞給MEMS器件,因為它們必須與環境相互作用;其次,MEMS器件的擴展方式與CMOS不同工藝的擴展方式不同。

采用多種工藝

SiP技術提供的集成對可穿戴設備、智能燈或智能家居等應用特別有價值,因為這些產品的空間和尺寸非常重要。從實際應用看,SiP設計方案融合了晶圓級封裝(WLP)、2.5D或3D結構、倒裝芯片(flip-chip)、引線鍵合、封裝體疊層(package-on-package)等工藝;還可以嵌入無源器件、共形屏蔽、濾波器和天線。

典型IoT方案的幾種SiP封裝

融合MEMS傳感器

MEMS傳感器需要與環境交互以進行聲音、光或氣體檢測。使用MEMS封裝通常要從QFN封裝遷移到基于層壓板的封裝。層壓板設計可以采用腔基封裝或混合腔封裝,其中封裝的一半是模壓的,另一半是為MEMS器件提供一個空腔。這種模壓器件更能承受惡劣的環境。

幾種腔基MEMS封裝

實現IoT標準化封裝

目前,MEMS、傳感器及IoT器件的封裝設計還很零散。設計人員希望多個項目重用相同的封裝,即使這些封裝并不總是與特定應用兼容。MEMS、傳感器封裝的標準化將有助于降低成本和加快MEMS的采用,增強制造商將新產品推向市場的信心。

FOWLP實現極致性能

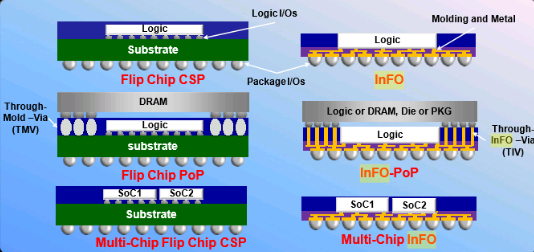

摩爾定律在工藝技術上似乎已走到了盡頭,所以先進封裝技術正在接棒,如扇出晶圓級封裝(FOWLP)就可以提高組件密度和性能,有助于解決芯片I/O限制。不過,成功的關鍵是從芯片設計開始。 現在,FOWLP已經在移動設備的批量生產中使用。其封裝過程包括將單個芯片安裝在稱為重分布層(RDL)的中間層基板上,該層提供芯片之間的互連以及與I/O焊盤的連接,所有這些芯片都封裝在一個模壓成型中。 所謂扇出封裝,是將連接件扇出到芯片表面,以便實現更多外部I/O,使用環氧模壓化合物完全嵌入片芯(die),因此不需要晶圓植球、熔劑、倒裝芯片組裝、清洗、底填料注入和固化等工藝流程。這反過來又消除了中間層,并使異構集成的實現更加簡單。 扇出技術可以提供比其他封裝類型更多I/O的小尺寸封裝。早在2016年,蘋果就憑借臺積電(TSMC)的集成扇出(integrated fan-out,InFO)晶圓級封裝技術,將其16nm A10應用處理器與移動DRAM集成到iPhone 7內部的一個封裝中,為應用處理器提供更好的熱管理。TSMC的InFO使蘋果實現了非常薄的封裝體疊層(PoP,Package-on-Package)。

TSMC的InFO技術

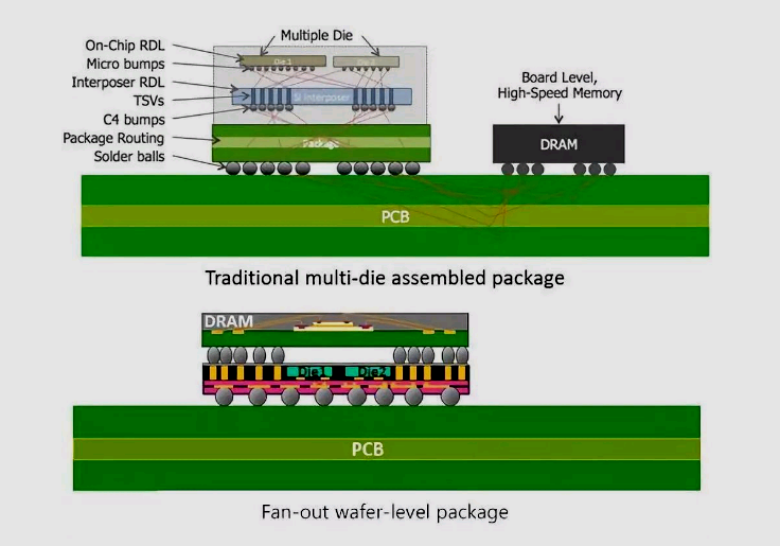

InFO平臺的再分布層技術將硅片直接連接到PCB層,而無需另一層基板。臺積電設計的互連通孔(TIV)可以提供支柱,使用混合垂直和水平互連技術連接不同的硅片或組件。InFO體現了其短垂直和長水平連接之間的連接,加速了信息的傳播。 作為對WLP的改進,FOWLP技術可以提供更多與硅片芯的外部接點。它將芯片嵌入環氧模壓料中,然后在晶圓表面制造高密度RDL和錫球,形成一個重組晶圓。 通常,它首先將前道處理過的晶圓切成單獨的片芯,然后將片芯在載體結構上隔開,其空隙被填滿形成一個重組晶圓。FOWLP在封裝和應用板之間提供了大量的連接。此外,基板基本上比片芯大,因此片芯間距更為寬松。

傳統多片芯封裝與FOWLP

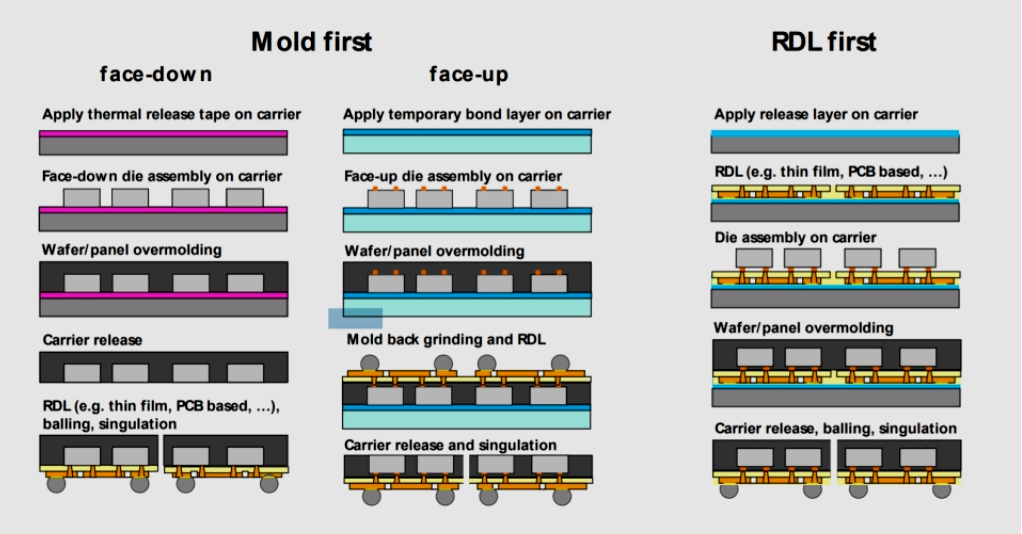

FOWLP有幾種變體,每種都使用稍有不同的制造步驟。FOWLP組件可以使用模壓優先(mold-first)流程創建,片芯面朝下或面朝上安裝,或者使用RDL優先(RDL-first)組件。

模壓優先方法

片芯使用臨時粘合層或熱釋放層連接到載體上,然后將其模制到封裝中。如果片芯面朝下安裝,接下來的步驟是釋放臨時層,連接RDL,形成完成封裝的焊球。如果片芯面朝上安裝,則需要一些附加步驟。 首先,單個片芯I/O連接必須通過在其上添加銅柱來擴展,然后再進行二次成型。成型后,嵌條的背面必須接地,在連接RDL和形成焊球之前露出支柱。

RDL優先方法

RDL使用臨時釋放層連接載體,而片芯連接到RDL。然后是組裝成型、載體釋放、焊錫球成型。這兩種方法的最后一步都是將組件分開,使這些組件整體形成單獨的器件。

FOWLP技術的兩種方法

這些方法具有不同的成本和性能權衡。在成本方面,模壓優先面朝下方法避免了制作銅柱和研磨,因此制造成本較低;最適合低I/O數的應用;但是,存在著片芯移位、晶圓翹曲等問題,限制了在復雜多芯片封裝中的應用。 面朝上的方法減少了這些問題,并在熱管理方面有優勢,因為芯片背面完全暴露,有利于散熱。 在性能方面,與其他兩種方法相比,面朝下的方法的連接路徑更短。這兩種方法都有銅柱,可以將連接延伸到RDL,同時在芯片下有一層材料,增加了連接之間的寄生電容,從而影響了其高頻性能。

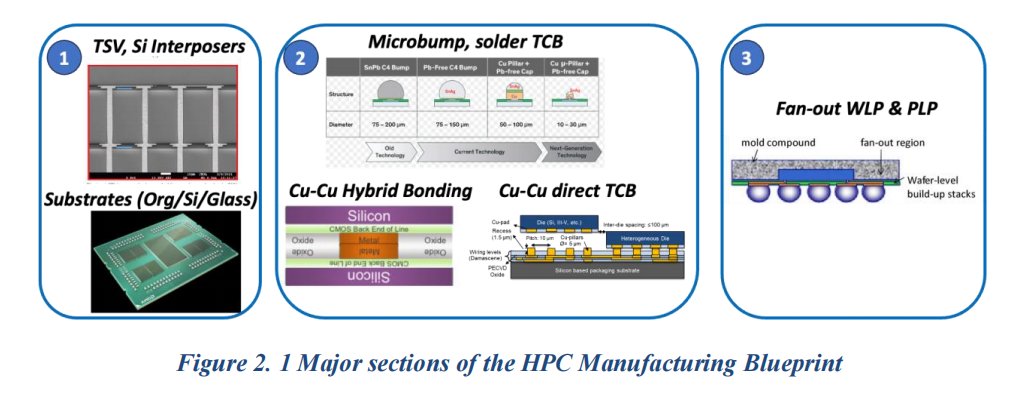

2.5D到3D IC封裝的關鍵是TSV

在2.5D封裝中,片芯采用堆疊或并排放置在基于硅通孔(TSV)的中間層頂部。底部的中間層提供芯片之間的連接。2.5D封裝技術是傳統2D IC封裝技術的一個進步,它使跡線和空間更加精細。 2.5D封裝通常用于高端ASIC、FPGA、GPU和內存。2008年,Xilinx將其大型FPGA分成了四個更小、良率更高的芯片,并將這些芯片連接到一個硅中間層上,從而誕生了2.5D封裝,最終成為流行的高帶寬內存(HBM)處理器集成。

TSV連接的功能完整的3D封裝

在3D IC封裝中,邏輯片芯堆疊在一起,通過銅TSV在硅芯片之間實現垂直互連,并使用有源中間層連接片芯。與通過導電凸點或TSV將元件堆疊在中間層上的2.5D不同,3D IC封裝采用多層硅晶圓并通過TSV將元件堆疊在一起。 TSV是2.5D和3D封裝解決方案中的一項關鍵技術,它提供了一種穿過片芯硅晶圓的垂直互連。這種封裝是以晶圓形式制造的,里面填充了銅。TSV是一種穿過芯片整個厚度或基板延伸的長通孔電氣連接,它創建了從芯片一側到另一側的最短路徑。然而,TSV除了自身顯著的電氣特性外,還對其附近的器件和互連的電氣行為產生間接影響。 為了精確地模擬一個2.5D/3D異構系統,設計者需要從這些2.5D/3D元素的物理結構中提取精確電參數的工具,然后將這些參數輸入行為仿真器。利用完整組件裝配的3D數字孿生模型,設計者可以準確地提取出2.5D和3D模型中的寄生性,以分析性能和適當的協議遵從性。 值得注意的是,2.5D和3D堆疊都會產生各種偶然的物理應力,例如在安裝過程中基板翹曲和碰撞引起的應力。設計人員必須能夠分析這種芯片封裝交互作用引起的應力及其對器件性能的影響。一旦封裝接近完成,需要導出精確的3D封裝熱模型,以便在詳細的PCB和全系統熱分析中使用,進而對系統外殼進行最終調整,并優化自然和/或強制冷卻。

3D IC封裝的熱仿真

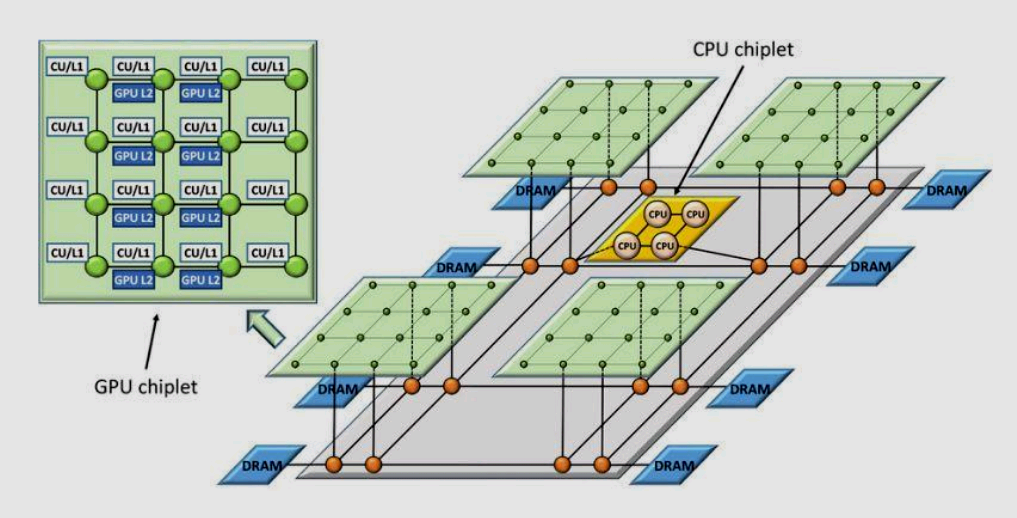

芯粒為3D IC封裝錦上添花

還有一種使用芯粒(chiplet)的3D IC封裝,是由AMD發明的,臺積電、英特爾、華為海思都在研究。它可以實現CMOS器件與非CMOS器件的異構集成,或許有助于讓摩爾定律繼續下去。這個想法是將一個大的SoC分解成更小的芯粒,以提高良率和降低成本,同時提高客戶的可重用性。芯粒模式允許設計人員像搭積木一樣制造芯片,利用各種IP而不考慮它們是在哪個節點或用什么技術制造的;它們可以構建在各種材料上,包括硅、玻璃和層壓板。

芯粒有望延續摩爾定律

下一代IC設計人才必須懂封裝

美國喬治亞理工學院(Georgia Tech)教授、超大規模集成電路(VLSI)數字暨混合信號設計專家Arijit Raychowdhury表示,先進IC設計的新疆域在于封裝。

他說:“封裝是一個設計工程師必須了解的。”先進IC設計的重點已經從工藝技術轉向封裝技術,但問題在于“業界對于這種轉移將如何進展的了解不夠。”他認為臺積電是一家在這方面表現得比較好的公司。 他指出:“芯片產業已經意識到,依循摩爾定律的工藝微縮速度已經趨緩,而產業界似乎不愿意面對芯片設計即將發生的巨變──從工藝到封裝技術的轉變。” 現在,晶體管微縮已經接近極限,但從技術上來看,也許微縮演進的速度不如我們想的那么快。以內存制造技術或后道工藝晶體管技術為例,他認為還會有很多新的東西出現,產業界應該在這個特定領域快速行動起來,去探討這方面的“黑魔法”。 面對封裝的技術演進和挑戰,你準備好了嗎?

原文標題:先進IC封裝到底能不能幫摩爾定律一把?

文章出處:【微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

456文章

51092瀏覽量

425983 -

IC

+關注

關注

36文章

5975瀏覽量

175952 -

封裝

+關注

關注

127文章

7973瀏覽量

143235

原文標題:先進IC封裝到底能不能幫摩爾定律一把?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產工藝

功率模塊封裝全攻略:從基本流程到關鍵工藝

飛凌嵌入式-ELFBOARD 從七種芯片封裝類型,看芯片封裝發展史

臺積電研發芯片封裝新技術:從晶圓級到面板級的革新

芯片設計從工藝到封裝技術的巨變

芯片設計從工藝到封裝技術的巨變

評論