Silicon Labs(亦稱“芯科科技”)近日推出“Clock Talk”時鐘線上系列研討會的第二場隨選即播中文演講主題“為56G/112GSerDes選擇XO/VCXO時鐘參考時的設計考量”,提供了中文及英文演說版本供用戶選擇。 為56G/112G SerDes選擇XO/VCXO時鐘參考時的設計考量

電信、無線基礎設施、光學模塊、廣播視頻、醫學成像和其他工業市場的下一代參考時鐘要求大量采用FPGA、ASIC和SoC,它們使用56G 或112G SerDes 來支持更高的數據速率和帶寬功能。SerDes 帶寬增加和相關參考時鐘的RMS 相位抖動要求之間存在直接的相關性。

隨著SerDes 速度的增加,參考時鐘所需的 RMS 相位抖動性能隨之減少。在本次網絡研討會上,我們概述最新一代FPGA、光學DSP、相干DSP 和網絡處理器的參考時鐘要求,并重點介紹Si54x Ultra Series XO 和 VCXO 產品家族的關鍵功能,這些功能可確保參考時鐘RMS 相位抖動性能保持在最大限度內;從而為系統設計者在其系統抖動預算中增加了更多馀欲。

責任編輯:lq

-

FPGA

+關注

關注

1630文章

21794瀏覽量

605132 -

時鐘

+關注

關注

11文章

1746瀏覽量

131673 -

網絡處理器

+關注

關注

0文章

48瀏覽量

13987

原文標題:Clock Talk中文隨選即播新單元上線-選擇XO/VCXO時鐘參考的設計考量

文章出處:【微信號:SiliconLabs,微信公眾號:Silicon Labs】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AB-x36C系列低G靈敏度的超低相位噪聲

蔡司工業CT設備METROTOM檢測連接器質量

config37中根據DACCLK配置jesd clock,請問下jesd clock大小是跟之前配的serdes pll配置的line rate成40倍關系的嗎?

config108讀取config108寄存器的值時鐘為000f,只是serdes_pll未鎖定,為什么?

內部缺陷瑕疵檢測設備高質量檢測AI服務器連接器

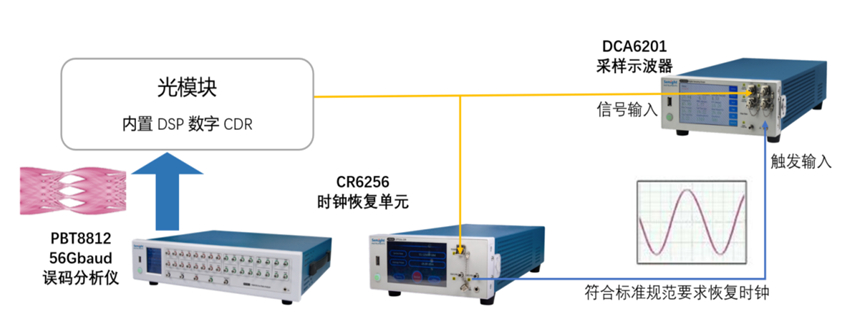

56Gbaud CR6256!400G/800G單多模光模塊及接口的時鐘提取

AD9694輸入時鐘低于337.5MHz時,serdes鎖相環無法鎖定怎么解決?

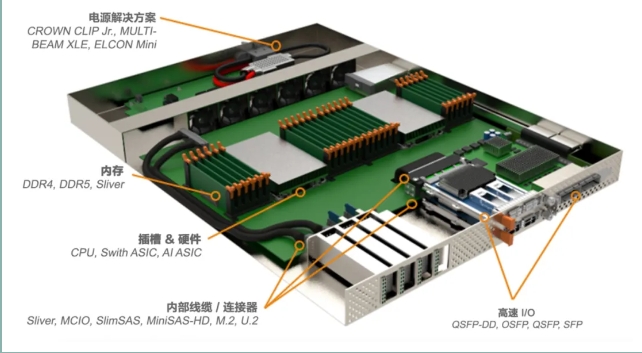

TE 112G 產品解決方案,助力“通關”高速互連挑戰

高速板材為什么貴?單看這一點你們就明白了!

AMD硅芯片設計中112G PAM4串擾優化分析

56G QSFP+ SR4光模塊最新解決方案

為56G/112G SerDes選擇XO/VCXO時鐘參考時的設計考量

為56G/112G SerDes選擇XO/VCXO時鐘參考時的設計考量

評論