線寬要按50或者100歐姆設計,差分線要做等長,電源走線要粗一點,電源地平面最好緊耦合等等這些PCB設計的常規操作相信沒人質疑。那么對于走線包地要打孔,估計你們也不會有什么意見吧……

有些PCB設計的操作,工程師們已經在腦海中形成了定勢的思維,甚至都已經寫進了各種skill或者約束規則里面。無可否認,大部分這些設計都是經過了多次的驗證,說白了就是換誰來做都不會有問題的那種。前面也說了,對于走線包地要打孔這一點,其實看起來也是一個常規的操作,但是卻并不是每個人做都能做得很好的哦。我們最近就收到這樣的一個case,本來想炫一把包地打孔的高手風范,結果還比不上包地不打孔這種我們認為錯誤的做法。

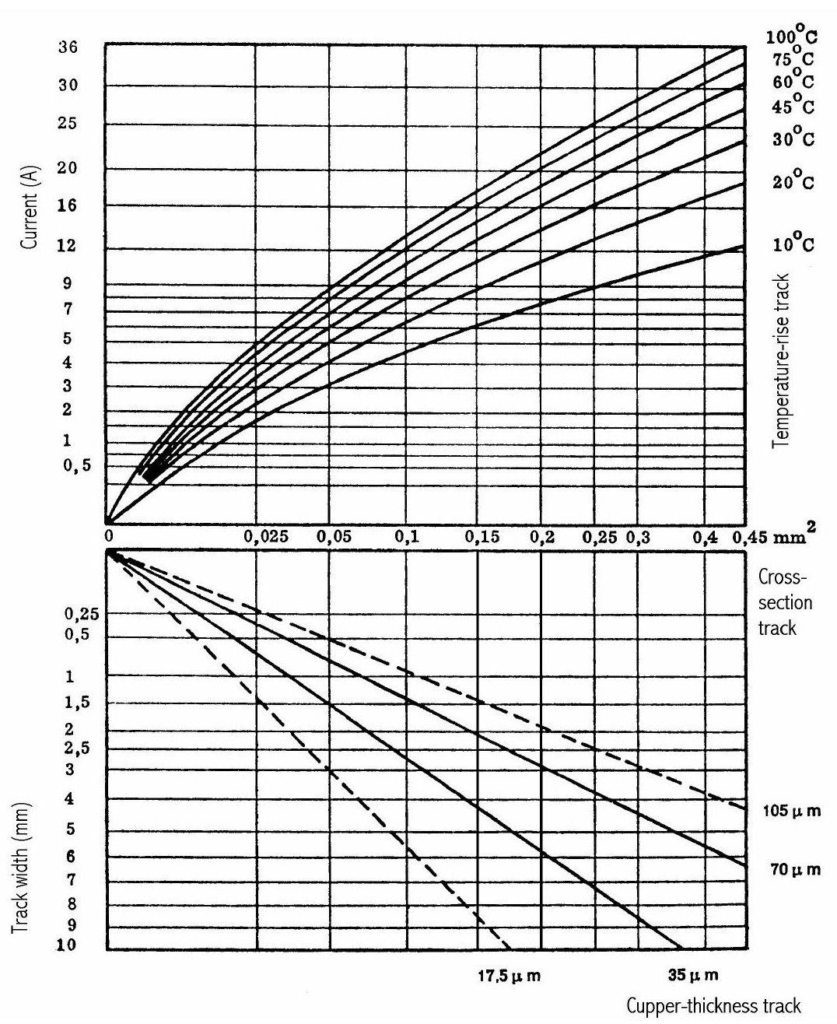

這個板子也是一個比較特殊的板子,首先它只是一塊雙面板,板厚是1mm,其次它居然要走高速線,板內的高速線達到了10Gbps。聽起來是不是很恐怖?當然其實在我們看來,走表層也不是不能走10Gbps的信號,其實我們甚至還走過25Gbps的光模塊信號。由于可以只在表層走完,而且我們知道1mm的板厚如果要控制100歐姆差分阻抗的話,也就只能通過表層共地的方式進行阻抗控制了,下面底層的地基本是影響不了阻抗的了。通過阻抗的精確計算后,我們確定了差分線的線寬,線距,以及信號線兩邊到包地的距離以便控制到阻抗。如下所示:

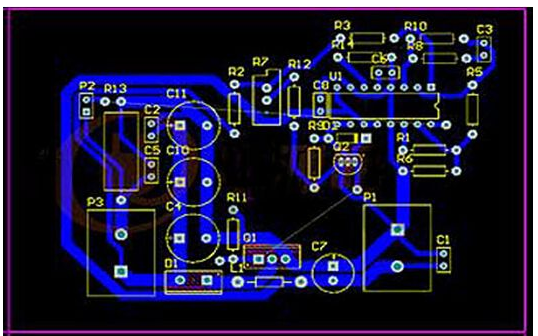

板子很簡單,這些10Gbps的高速線就幾對,因此工程師在我們高速先生還沒反應過來的時候就已經把走線走出來了,幾inch的走線,走線走在表層,底層鋪下地,然后中間打一些地過孔,距離大概500mil左右的地孔,部分PCB走線如下所示:

然后這個那么“簡單”的設計項目,也沒有說要做仿真,后面準備投板了,才象征性的發給我們檢查一下。我們初步看了下就覺得有點問題(這里先賣個關子哈),認為這個設計比較特別,建議做一下仿真。PCB工程師和客戶都覺得會不會夸張了一點,看著我們高速先生堅定的眼神之后,還是同意去看一下。

果然,仿真證實了我們的懷疑,從插損和回損來看,在較低的頻段就會有比較尖峰的諧振點。基本上肯定會影響到10Gbps的信號了,下文會有眼圖的情況哈。

正好這類10Gbps的走線不止一對,另外有一對由于底層需要鋪其他的電源和走線,因此不能像上面這對走線一樣,很幸福的擁有一個下面完整的參考層,因此另外一對走線只能完全通過表層的包地來控制阻抗,因此也就沒必要在沿途打地過孔了。如下所示:

PCB工程師還戰戰兢兢的過來和我們高速先生說,這對走線底層沒辦法鋪地,所以就沒法打地過孔,會不會更差啊。

干脆我們懷著期待的心情又做了一次仿真,結果奇跡……并沒有出現!!!

從插損曲線來看,諧振點變得更靠近而且很密了,間隔不到1個GHz就有一個諧振,看起來也是一個比較差的結果。

但是呢,俗話說得好,沒有對比就沒有傷害。有的東西看起來更差,但是我們一定要有信心,因為不知道什么時候,別人就會比你更差。我們把兩種情況擺在一起看下,就會發現,其實不打孔這種看起來不對的做法,其實反而是兩者較優的一方。

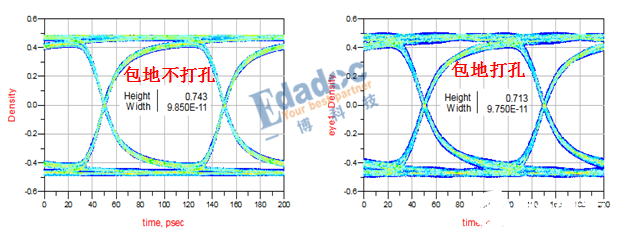

如果看不懂上圖的無源參數也沒關系,我們把眼圖對比一下,你們就清楚了。

同樣在10Gbps情況下,兩者的眼圖結果是這樣的:你會發現眼高和眼寬都會有差異,其中眼高居然差了近30mV,抖動也有一定的差距。

當你千方百計想遵循規則或者一些常規操作去走的時候,可能出來的結果反而還不如一個“懶”的方法。我們經常會認為打地過孔進行包地肯定是只有好處沒有壞處,但是高速設計本身卻并沒有人們想象得那么簡單,很多細微的東西忽略了可能會出現這種反常的結果。

編輯:hfy

-

阻抗

+關注

關注

17文章

958瀏覽量

46047

發布評論請先 登錄

相關推薦

硬件工程師談高速PCB信號走線規則TOP9

PCB設計走線的幾點專家建議

pcb開窗怎么設計_PCB設計怎樣設置走線開窗

高速PCB設計中走線屏蔽的各項規則解析

PCB設計時Layout有什么走線策略

PCB設計:走線包地要打孔有什么建議?

PCB設計:走線包地要打孔有什么建議?

評論