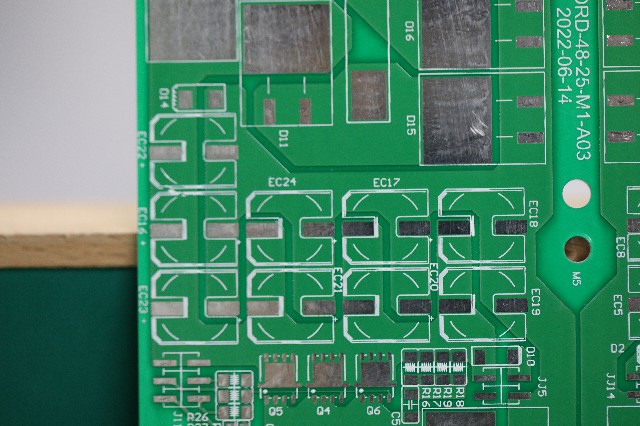

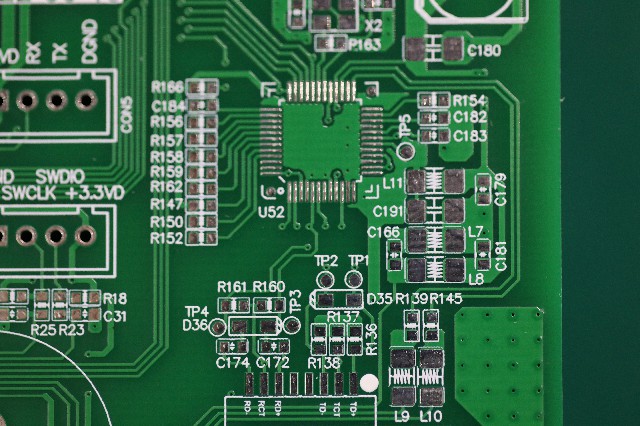

電磁兼容性是全球大多數市場上銷售的電子產品的關鍵要求。大多數EMC設計注意事項都是在PCB設計階段發現的,因此在本文中,我們將介紹一些有助于提高PCB性能的常見技巧和技巧。

什么是EMC?

電磁兼容性(EMC)是一種精心設計電子電路的方法,它能使電子電路對其他電子產品的影響最小化,并能抵抗其他電路的影響。盡管大多數電路都能正常工作,但全世界大多數國家的產品法律和法規都要求商業產品遵守嚴格的EMC要求。要了解如何降低電磁兼容,重要的是要知道電磁輻射到底是什么。

電磁兼容輻射是由交流/開關電流產生的雜散無線電波,任何帶有交流電的導體都充當天線。因此,設計人員的工作就是讓產品中的所有導體都不能發射強無線電波。

初步設計考慮

由于電磁輻射是無線電波,電磁兼容問題的常見來源包括大多數高速開關設備、數據總線和無線電電路。由開關模式電源引起電磁兼容性問題以及將開關噪聲注入電源軌而臭名昭著,而Wi-Fi模塊也可能存在嚴重問題。高速數據總線(如SPI、PCIe和內存通道)也可能是干擾源,必須小心地對這些軌跡進行路由,以將干擾降至最低。

在PCB上布線之前,必須仔細考慮PCB的設計和布局。很多信息都可以在網上免費獲得,但總的來說,遵循以下規則是至關重要的。

模擬功能等應基于數字元件分組

如果可能的話,連接器應該放在PCB的一側。

連接部件之間的距離應最小化

高速連接器應分組,并與模擬連接器分開

PCB布線技巧

布線PCB軌跡是確定元件和連接器應放置在何處的同樣重要的設計步驟。與初始設計階段一樣,在路由跟蹤時,設計可以考慮許多不同的因素。

PCB層

雖然兩層PCB通常是最便宜的選擇,但它們有一個缺點,即不允許使用功率面。任何具有兩層以上的PCB都有機會使用電源平面,其中整個層專用于電源軌(如5V)或接地。在四層PCB中,最好使用兩個內層作為功率平面,因為這將使兩層之間的電容最大化,并為電流回路和發射的發射提供最小的返回路徑。

微分對

差分對,如在USB中找到的差分對,應始終相鄰進行路由,中間沒有任何跡線或平面。同樣重要的是,這些跡線的長度相同,因為這有助于阻抗匹配。如果兩個跡線間隔過大,或阻抗不相等,不僅會影響差分對的性能(即噪聲和速度),還會導致電流回路,從而導致無線電發射。

保護跡線

保護跡線是一種特殊布線的地面跡線,它圍繞著一條跡線的任意一側,可以用來抵抗對外部源的干擾,也可以防止跡線的雜散發射逸出(保護跡線充當環繞該跡線的簡單法拉第籠)。

縫合孔

縫合通孔是一種通孔,通常連接到地面,并環繞特別嘈雜的區域。它們通常存在于多氯聯苯上,就像保護痕跡一樣,起到法拉第籠的作用,幫助吸收散失的電磁輻射。縫合孔之間的間距一般應小于λ/20,其中λ代表防護的最大頻率。例如,如果2.4GHz電路被保護,則通孔之間的最小距離應為15cm/20=7.5mm。然而,這樣的小距離可能并不總是可能的,并且包含過孔通常可以提高性能。通常情況下,縫合通孔的尺寸不是問題,但使用PCB提供的最小鉆孔,且不產生額外成本是最理想的。

縮短跡線長度

當減少電磁輻射時,重要的是盡量縮短跡線長度,因為這會使它們成為一個糟糕的天線。然而,還必須確保跡線的長度不是該跡線中將出現的信號預期標稱頻率波長的倍數。例如,如果一個2.4GHz的信號將出現在一個跡線中,并且它不是一個無線鏈路(即標準數據總線通道),那么該跡線的長度不應是波長15cm的倍數甚至是一個分數。因此,應避免使用15厘米、7.5厘米和5厘米的痕跡長度,甚至不應使用超過15厘米的痕跡。

結論

本文中概述的方法只是減少EMC的一些方法,通過免費在線資源的進一步探索將揭示EMC的設計是多么復雜。然而,降低電磁兼容性的最佳方法是在嘗試使用通過捕捉雜散發射(即法拉第籠)來降低電磁兼容性的方法之前,先了解是什么導致了電磁兼容性,并消除了這些來源。

責任編輯:tzh

-

pcb

+關注

關注

4324文章

23157瀏覽量

399244 -

無線

+關注

關注

31文章

5469瀏覽量

173676 -

電磁

+關注

關注

15文章

1138瀏覽量

51903 -

emc

+關注

關注

170文章

3946瀏覽量

183559

發布評論請先 登錄

相關推薦

電源 PCB 布局中的常見錯誤及避免方式

五種常見的PCB表面處理技術

提高網絡性能的阻抗優化技巧

常見的PCB元件封裝類型

PCB線路板常見缺陷原因分析:解鎖電路板制造的隱秘挑戰

PCB電路板的層數對性能的影響

pcb板設計中的常見錯誤

如何提高產品的EMC性能

pcb板密度,影響性能的重要因素

PCB線路板制造中常見的錯誤有哪些,如何避免?

你的電子設備為何能抵御潮濕?PCB耐CAF性能的秘密

PCB設計工作中常見的錯誤有哪些?

提高PCB性能的常見技巧介紹

提高PCB性能的常見技巧介紹

評論