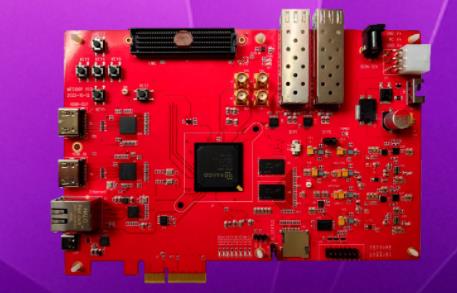

本實(shí)驗(yàn)基于ECE-CV K7-75T FPGA開發(fā)板實(shí)現(xiàn)。

軟件使用Vivado 2018.1。

1 HDMI概述

HDMI高清多媒體界面(英語:High Definition Multimedia Interface)是一種全數(shù)字化視頻和聲音發(fā)送接口,可以發(fā)送未壓縮的音頻及視頻信號(hào)。HDMI可用于機(jī)頂盒、DVD播放機(jī)、個(gè)人計(jì)算機(jī)、電視游樂器、綜合擴(kuò)大機(jī)、數(shù)字音響與電視機(jī)等設(shè)備。HDMI可以同時(shí)發(fā)送音頻和視頻信號(hào),由于音頻和視頻信號(hào)采用同一條線材,大大簡化系統(tǒng)線路的安裝難度。

圖1 HDMI硬件實(shí)物

如圖1,紅框?yàn)镋CE-CV板的HDMI輸入輸出接口,最高支持到1080P@60HZ的圖像輸入和輸出功能。

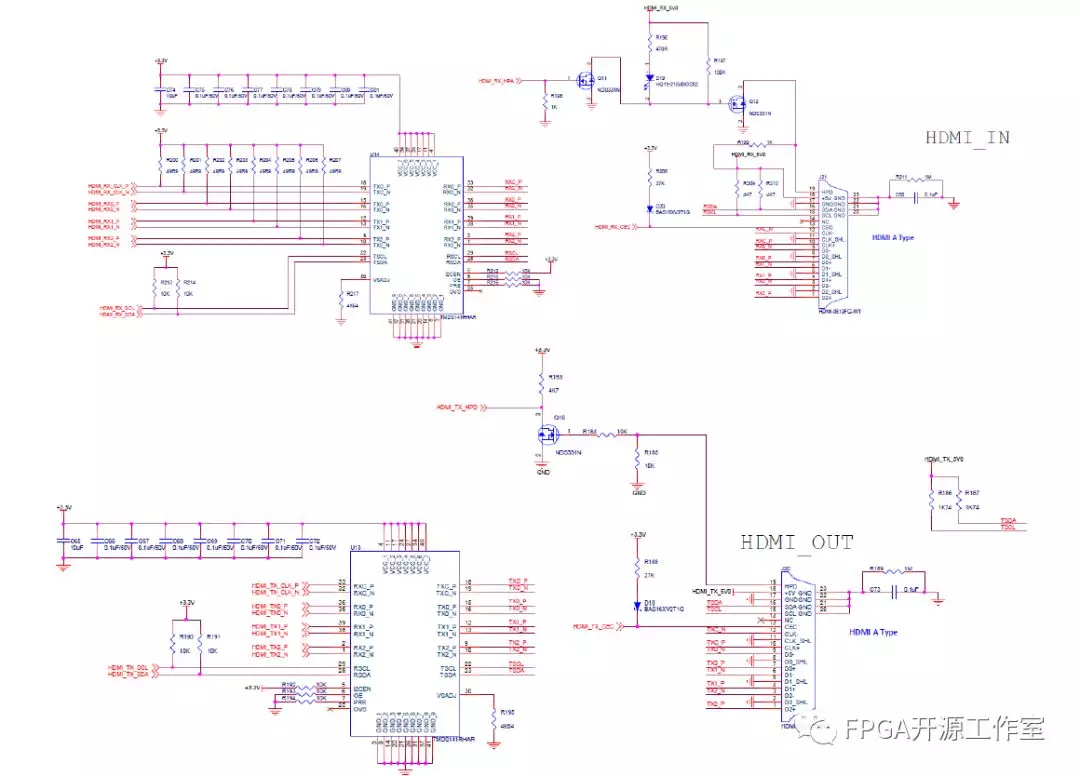

圖2 HDMI_IN 和HDMI_OUT原理圖

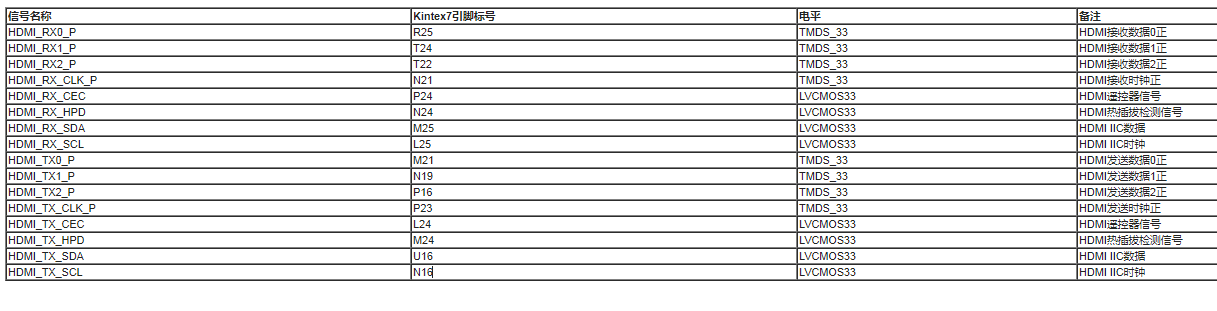

如圖2所示為ECE底板的HDMI_IN和HDMI_OUT的原理圖,下面對(duì)ECE-EDA和ECE-CV的HDMI接口的引腳介紹如表1所示:表1ECE-CV板HDMI接口引腳介紹

2 HDMI IP介紹

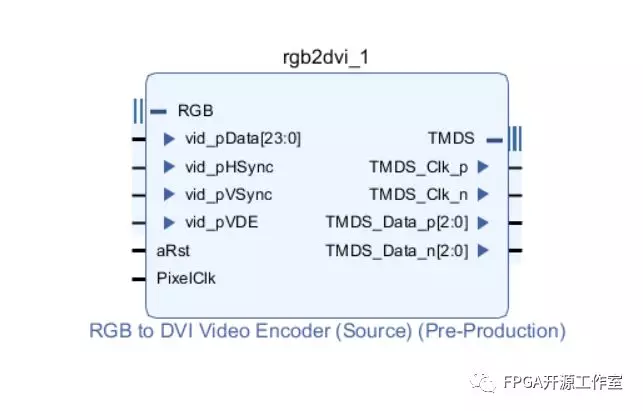

如圖3所示,rgb2dvi IP 實(shí)現(xiàn)RGB并行圖像數(shù)據(jù)信號(hào)轉(zhuǎn)換成串行差分信號(hào)輸出。1920*1080P@60HZ的像素時(shí)鐘為148.5MHZ。

圖3 rgb2dvi IP

圖4 rgb2dvi IP設(shè)置

如圖4所示,其他項(xiàng)均默認(rèn),TMDS clock range 選擇大于120MHZ。

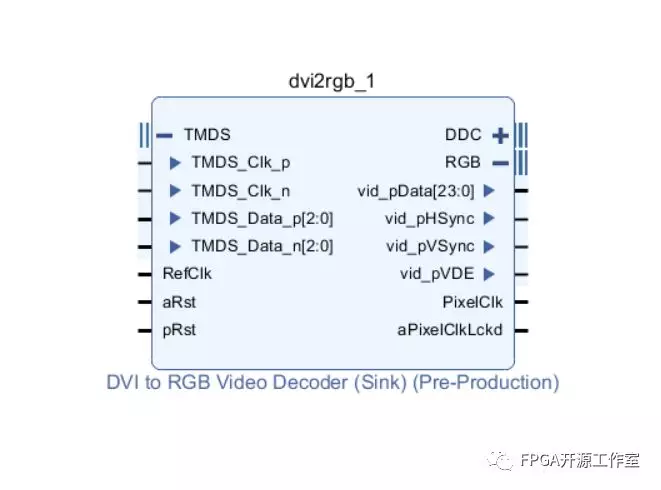

如圖5 Dvi2rgb IP實(shí)現(xiàn)串行視頻差分信號(hào)轉(zhuǎn)RGB并行圖像數(shù)據(jù)。參考時(shí)鐘為200MHZ。

圖5 dvi2rgb IP

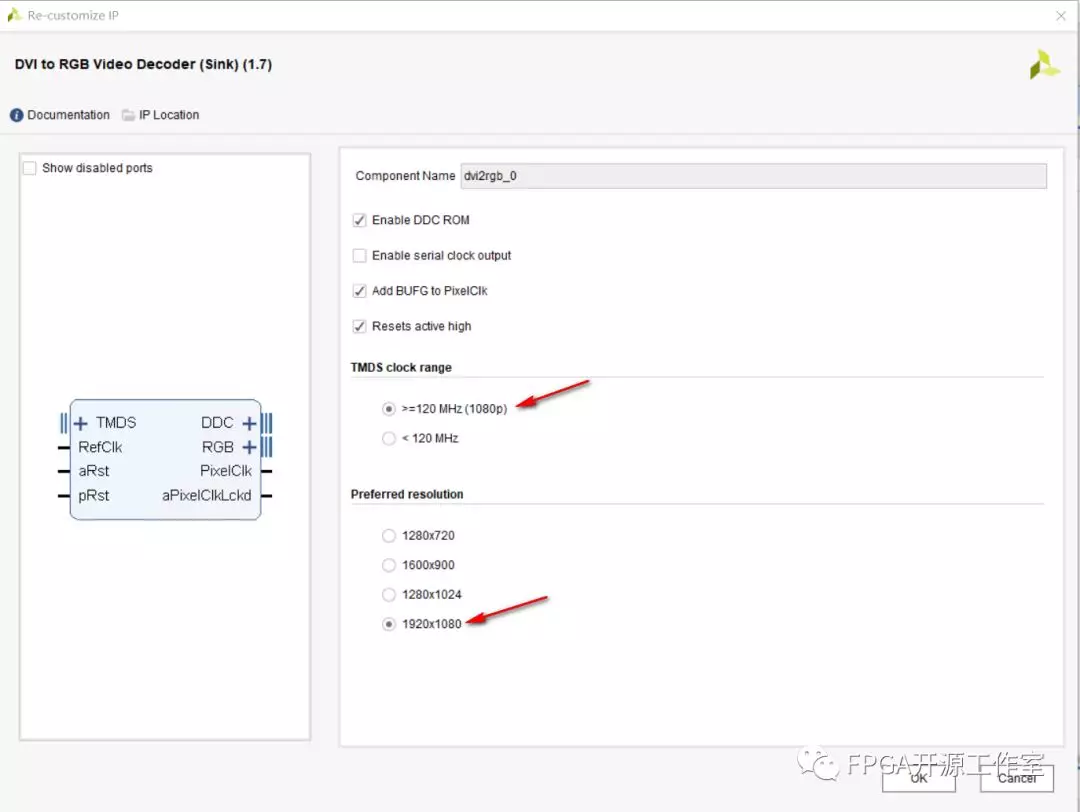

圖6 dvi2rgb IP設(shè)置

如圖6所示,TMDS clock range 選擇大于120MHZ,Preferred resolution選擇1920*1080。

3 HDMI輸入輸出實(shí)驗(yàn)系統(tǒng)搭建

筆記本電腦的HDMI輸出1080P@60HZ的視頻ECE-CV平臺(tái),經(jīng)過HDMI_IN到核心板再到HDMI_OUT再到顯示屏,顯示屏正常輸出視頻。整個(gè)硬件平臺(tái)如圖7所示。

圖7 ECE-CV數(shù)字圖像處理硬件平臺(tái)

如圖8,為HDMI_IN_OUT最終系統(tǒng)連接圖。

HDMI_IN_OUT系統(tǒng)由外部OSC輸入100MHZ時(shí)鐘,經(jīng)過Clock Wizard IP的倍頻輸出200MHZ時(shí)鐘到Dvi2rgb IP作為參考時(shí)鐘,同時(shí)輸出reset_n(locked )信號(hào)為全局復(fù)位信號(hào)。復(fù)位信號(hào)(reset_n)經(jīng)過Utility Vector Logic IP取反輸出‘1’復(fù)位‘0’有效rst信號(hào)。Dvi2rgb IP的參考時(shí)鐘(Refclk)為200MHZ,差分?jǐn)?shù)據(jù)信號(hào)輸入為TMDS_IN,經(jīng)過Dvi2rgb IP轉(zhuǎn)換為RBG888的VGA時(shí)序信號(hào)以及輸出像素時(shí)鐘(Pixelclk)。Rgb2dvi IP接收RBG888的VGA時(shí)序信號(hào)輸出TMDS_OUT的差分?jǐn)?shù)據(jù)信號(hào)。xlconstant IP為HDMI的輸入和輸出提供熱插拔信號(hào)輸出為‘1’。

圖8 HDMI輸入輸出實(shí)驗(yàn)系統(tǒng)連接圖

編輯:hfyI

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605197 -

HDMI

+關(guān)注

關(guān)注

32文章

1734瀏覽量

152226

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

紫光同創(chuàng)PGL22G開發(fā)板|盤古22K開發(fā)板,國產(chǎn)FPGA開發(fā)板,接口豐富,高性價(jià)比

盤古22K開發(fā)板

【米爾-Xilinx XC7A100T FPGA開發(fā)板試用】測(cè)試一

【Combat FPGA開發(fā)板】基于FPGA的接口轉(zhuǎn)換——MIPI轉(zhuǎn)HDMI

紫光同創(chuàng)PGL22G開發(fā)板|盤古22K開發(fā)板,國產(chǎn)FPGA開發(fā)板

紫光同創(chuàng)PGL22G開發(fā)板|盤古22K開發(fā)板,國產(chǎn)FPGA開發(fā)板,接口豐富,高性價(jià)比

圖像傳感器HDMI輸入輸出FMC模塊解決方案

6 FPGA LX75T FPGA開發(fā)方案

『 RJIBI 』- ECE-CV機(jī)器視覺教學(xué)方案

MP5610圖像處理開發(fā)板用戶手冊(cè)

小眼睛FPGA盤古100K開發(fā)板概述

基于ECE-CV K7-75T FPGA開發(fā)板的HDMI視頻流輸入輸出實(shí)現(xiàn)方案

基于ECE-CV K7-75T FPGA開發(fā)板的HDMI視頻流輸入輸出實(shí)現(xiàn)方案

評(píng)論