在這篇文章中,我們將介紹如何調(diào)用 Hyperlynx?、如何設(shè)置簡(jiǎn)單的原理圖以及如何運(yùn)行一些基本的仿真操作。Hyperlynx? 可支持下列兩種仿真工作流程。

LineSim:

用來(lái)預(yù)布局仿真,是設(shè)計(jì)周期中的早期仿真工具,主要用來(lái)評(píng)估假設(shè)情景并幫助定義電路板參數(shù)和布線指南。通過創(chuàng)建 I/O 緩存器、走線,終端以及連接器/電纜組件的示意圖,在“Schematic GUI”中完成 LineSim 中的仿真。

BoardSim:

用于布局后仿真以對(duì) PCB 設(shè)計(jì)進(jìn)行分析。PCB 中所需的網(wǎng)絡(luò)從布局文件中選出,然后在像 LineSim 這樣的工具中進(jìn)行仿真。由于它使用的是含布線約束、相鄰網(wǎng)絡(luò)布線以及距離等信息的布局文件,仿真是高度準(zhǔn)確的。 可以在 LineSim 中查找任何違規(guī)操作或所需的更改,并在最終 PCB 上簽發(fā)制造之前將其反饋到布局中。

在本系列中,可以使用 LineSim 和 Boardsim(如需要),具體取決于所討論的主題。

現(xiàn)在我們通過一個(gè)簡(jiǎn)單的仿真操作來(lái)了解一下這個(gè)工具。調(diào)用 Hyperlynx? 并選擇“New -> New SI Schematic”,如果調(diào)用的是“Waveform Viewer”,選擇“Both”或“Oscilloscope”

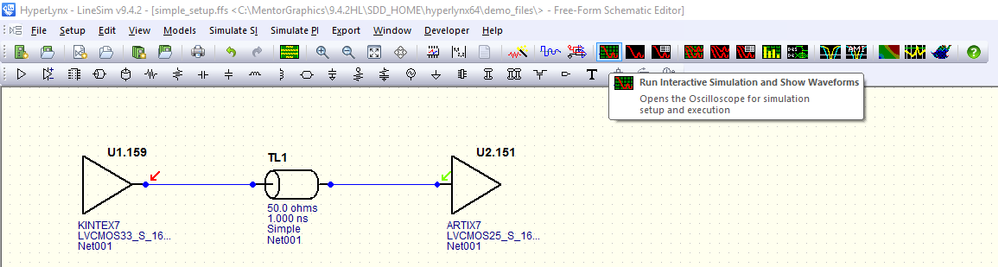

Hyperlynx? 支持 SI 仿真所需的基本元素,如下面的屏幕截圖所示:

發(fā)射器和接收器(IBIS 模型)

傳輸線

“Simple”、“Microstrip”、“Stripline”、“Wire”、“Cable”、“Connector”

疊加線和耦合線

通孔

S 參數(shù)/Spice 模型

電壓和接地

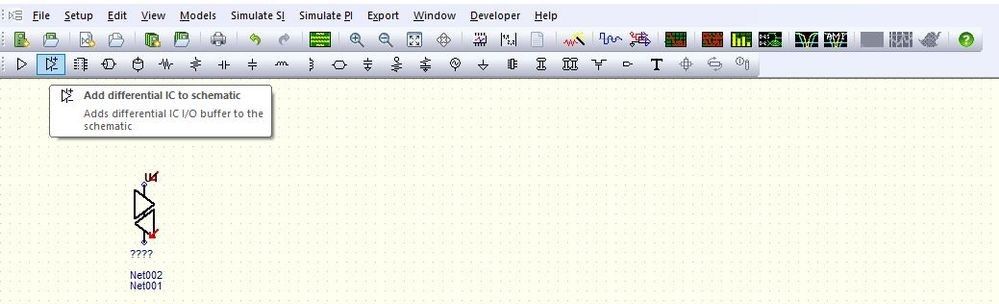

要?jiǎng)?chuàng)建原理圖,請(qǐng)針對(duì)單端 I/O 標(biāo)準(zhǔn)選擇“Add IC to Schematic”或針對(duì)差分 I/O 標(biāo)準(zhǔn)選擇“Add differential IC to Schematic”。

單端建立:

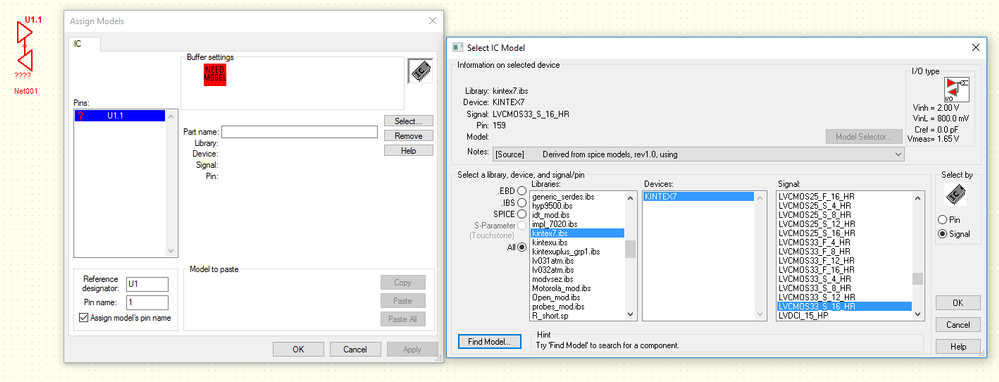

雙擊 IC 打開“Assign Models”窗口。我們將使用單端 I/O 標(biāo)準(zhǔn) LVCMOS33。

注意:您需要將 IBIS 文件 (.ibs) 保存在 Hyperlynx? 的“Libs”文件夾 (C:/MentorGraphics/9.4.2HL/SDD_HOME/hyperlynx64/Libs) of Hyperlynx? 中,才能在默認(rèn)庫(kù)中查看它。 您可以選擇在“Setup -> Options ->Directories”下的“Model-Library”文件路徑中添加更多文件夾。要包含設(shè)計(jì)文件夾中的所有文件夾,務(wù)必選中“Add design folder”和“Add design folder subfolders”。

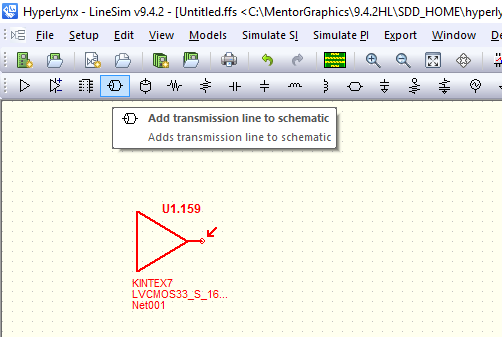

選擇必要的模型設(shè)置(在此示例中為變送器,因此應(yīng)選擇輸出),然后單擊“OK”

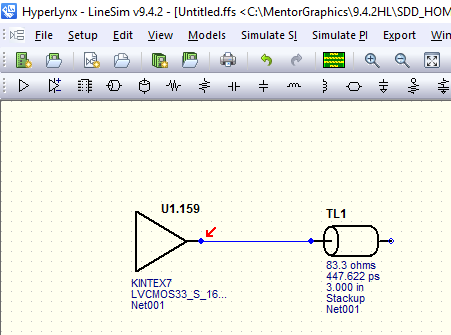

單擊“Add transmission line to schematic”

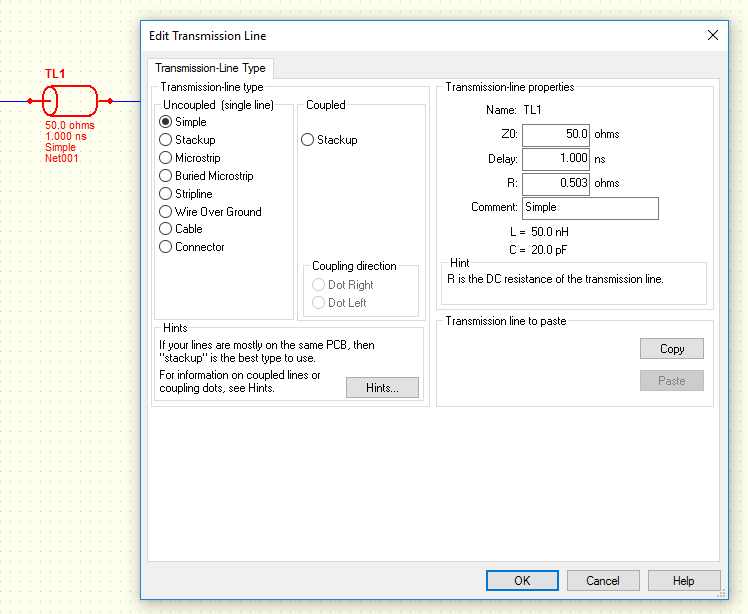

雙擊 TL1 設(shè)置傳輸線并選擇“Simple”非耦合類型,然后將“Z0“設(shè)置為 50 ohms、將“Delay”設(shè)置為 1.000 ns

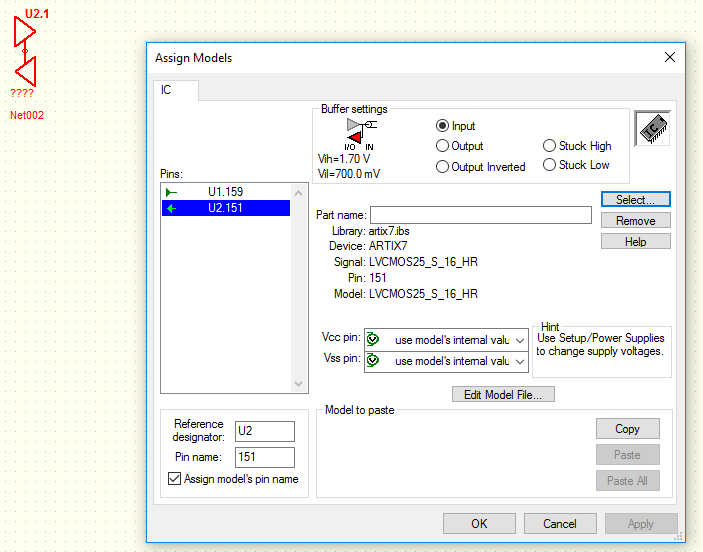

通過選擇必要的“Receiver IBIS Model”并將“Buffer”設(shè)置為“Input”來(lái)設(shè)置“接收器”并完成原理圖。保存原理圖設(shè)置。

運(yùn)行仿真,選擇“Run Interactive Simulations and Show Waveforms”按鈕(該按鈕會(huì)打開“Digital Oscilloscope”窗口)。

在“Oscilloscope”窗口中設(shè)置以下設(shè)置,然后單擊“Start Simulation

Operation -> Standard

Stimulus -> Global,

Oscillator -> 100 MHz, 50% Duty

IC modeling -> Typical

Thresholds for -> U2.151

Horizontal Scale -> 5 ns/div”

藍(lán)線顯示 U2 的 Vinh、Vinl 閾值。在確定接收器波形是否如預(yù)期那樣超過這些閾值時(shí),上述步驟非常有用,讓接收器可以確定所需的邏輯是“Low”還是“High”。 RX 波形 (綠色)和 TX 波形 (紅色)的轉(zhuǎn)換不清晰,我們會(huì)在本系列后面的主題中詳細(xì)討論。

差分建立:

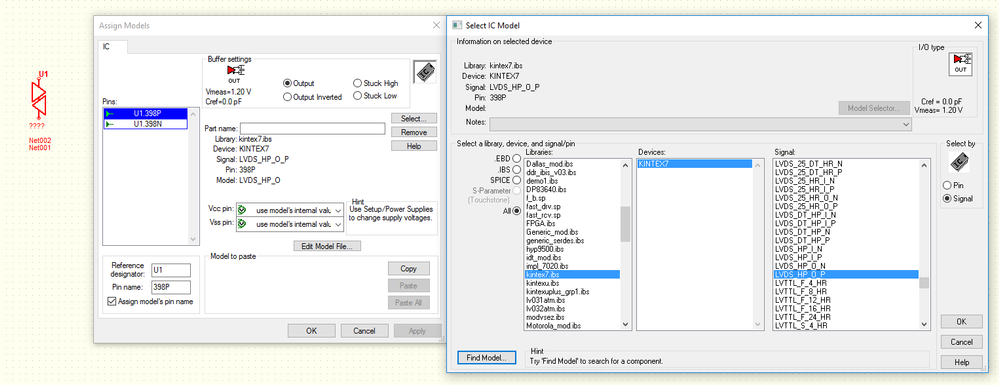

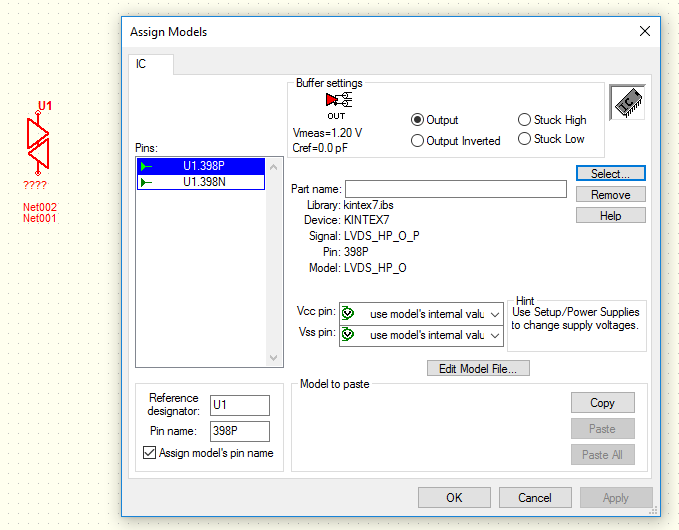

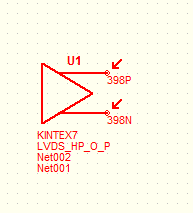

“Add differential IC to Schematic”后雙擊 IC,打開“Assign Models”窗口。我們將通過差分 I/O 標(biāo)準(zhǔn) LVDS 來(lái)進(jìn)行此建立,因?yàn)樗亲畛S玫牟罘?I/O 標(biāo)準(zhǔn)之一。

選擇必要的模型設(shè)置。在這個(gè)示例中用的是一個(gè)發(fā)射器,因此“P”后綴被選為輸出,而且“N”會(huì)自動(dòng)變?yōu)椤癘utput Inverted”,因?yàn)檫@是一個(gè)差分緩存器。單擊“OK”。

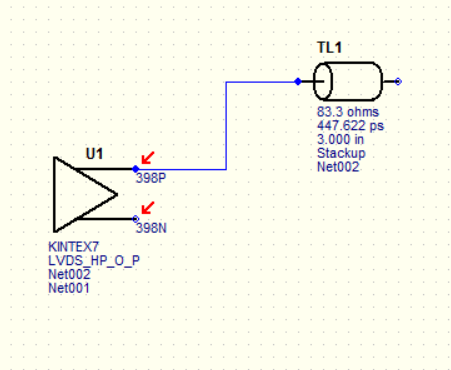

單擊“Add transmission line to schematic”。

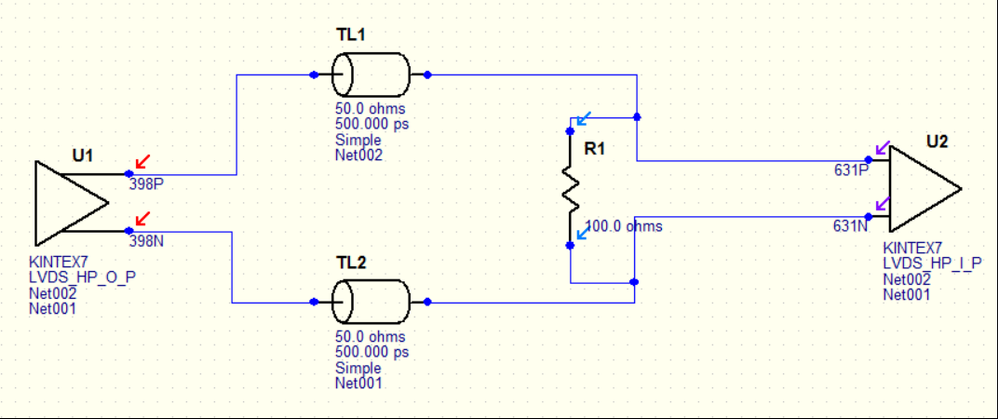

雙擊 TL1 設(shè)置傳輸線。如果是非耦合類型,選擇“Simple”,然后將“Z0”設(shè)置為 50 歐姆;將“Delay”設(shè)置為 0.5 ns,并選擇“Copy”以重復(fù)使用“N”傳輸線。

添加 TL2,雙擊“Edit”,然后選擇“Paste”將 TL1 的屬性復(fù)制到 TL2。

通過選擇必要的“Receiver IBIS Model”并將“Buffer”設(shè)置為“Input”來(lái)設(shè)置“Receiver”。這樣原理圖就完成了。

保存原理圖設(shè)置。

添加 LVDS 所需的 100 歐姆終端電阻,并通過雙擊“R”符號(hào)將值設(shè)置為 100 歐姆。

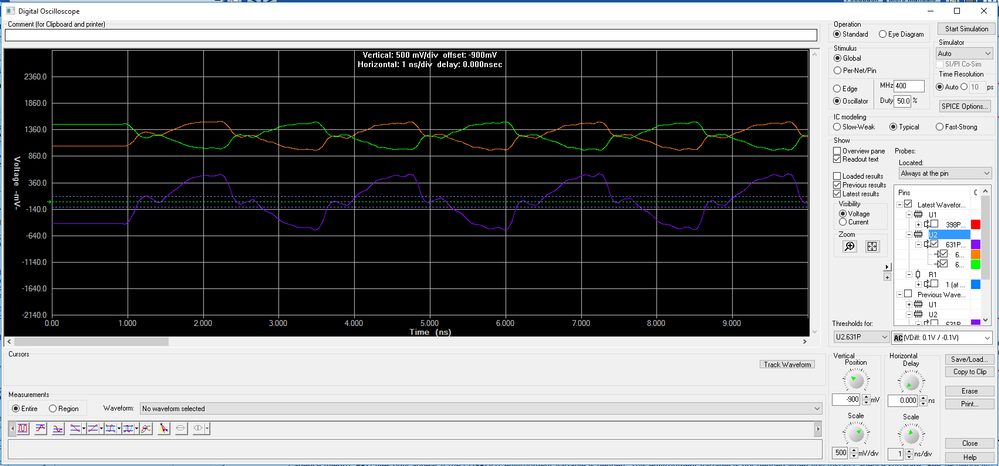

通過選擇“Run Interactive Simulations and Show Waveforms”按鈕。(該按鈕隨即會(huì)打開“Digital Oscilloscope”窗口)來(lái)運(yùn)行仿真。在“Oscilloscope”窗口中輸入以下設(shè)置,然后單擊“Start Simulation”:

Operation -> Standard

Stimulus -> Global,

Oscillator -> 400 MHz, 50% Duty

IC modeling -> Typical

Thresholds for -> U2.631P

Horizontal Scale -> 1ns/div

Horizontal Scale -> 1ns/div

Vertical Position -> -900 mv/div

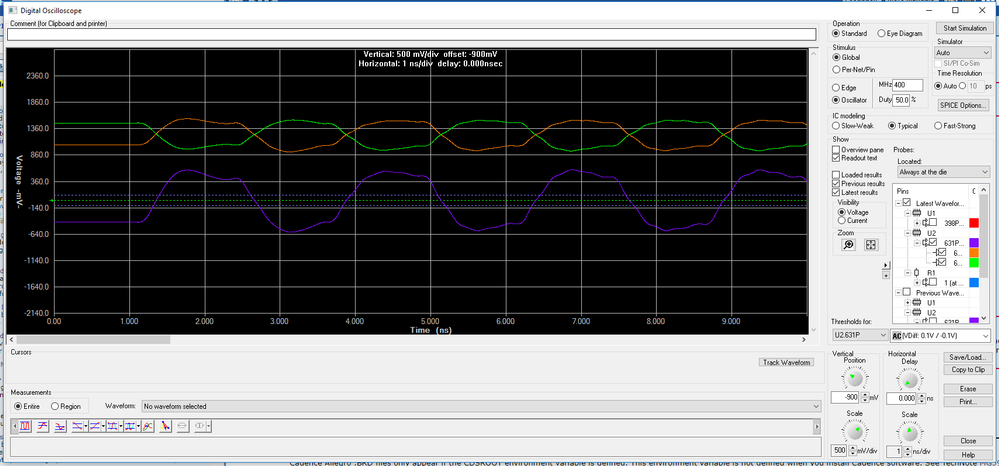

信號(hào)探測(cè)可以在“At the Pin”或“At the die”處完成。

在引腳處探測(cè):

如果您在電路板上的引腳上進(jìn)行物理探測(cè),此操作指的是將仿真探頭置于引腳上,從而展示您在實(shí)驗(yàn)室示波器中會(huì)看到的結(jié)果。“Purple”是差分探頭的波形。

在裸片處探測(cè):

指的是將仿真探頭放置在裸片內(nèi)從而展示裸片所看到的、無(wú)法在電路板上探測(cè)到結(jié)果。

有關(guān)如何對(duì)內(nèi)部和外部終端進(jìn)行探測(cè)的詳情,請(qǐng)參閱(Xilinx Answer 57566)。

定義 Stackup

PCB 的疊層需要針對(duì)介電材料、金屬類型、信號(hào)以及平面層在電路板中其他項(xiàng)目的布置來(lái)進(jìn)行定義。在運(yùn)行仿真之前進(jìn)行此設(shè)置有助于模擬 PCB 及各種特性(例如走線阻抗、走線分離及其他參數(shù)等)。

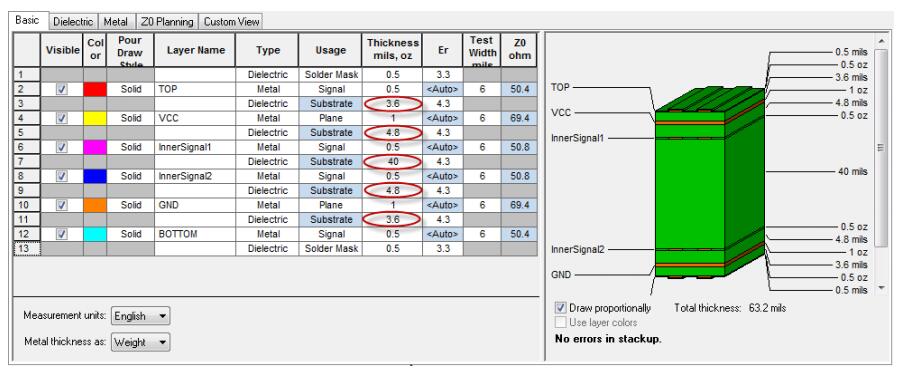

Hyperlynx? 提供了一個(gè)含基于電子數(shù)據(jù)表視圖的 Stackup Editor(您可以在該視圖中輸入值和圖像面板以使疊加結(jié)果可視化)。編輯器可以通過選擇“Setup -> Stackup Edit”或“Edit Stackup”按鈕來(lái)訪問,如下所示:

如上圖所示,編輯器有各種標(biāo)簽及其快捷說(shuō)明。

基要:通過添加/刪除層、設(shè)置測(cè)量單位(英制/公制)和金屬厚度(厚度/重量)來(lái)定義疊層信息。

介電:定義疊層的介電特性,如技術(shù)、損耗角正切和導(dǎo)熱系數(shù)。可以選擇根據(jù)周圍的介電層來(lái)計(jì)算金屬層的介電常數(shù)。

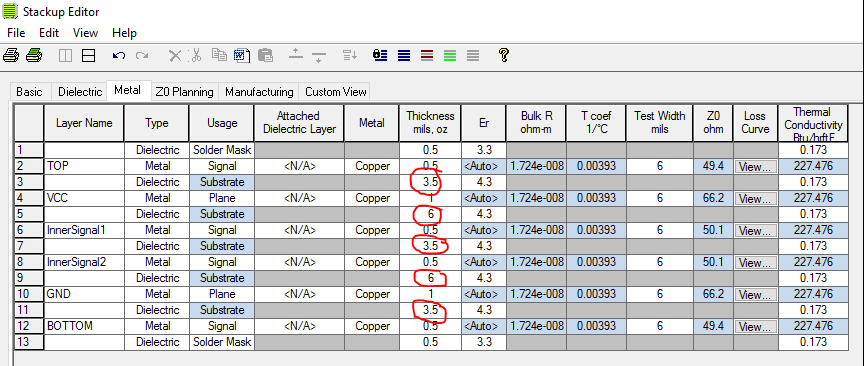

金屬:定義金屬特性,如金屬類型(銅/鋁/錫等)、厚度和金屬的其他屬性。

Z0 規(guī)劃:定義疊層的特征阻抗。此計(jì)劃編制標(biāo)簽是最有用的標(biāo)簽之一,因?yàn)樗屇軌蛟谟?jì)算單跡和差分對(duì)走線的特定目標(biāo)阻抗時(shí)得出最佳數(shù)據(jù)。

制造:定義金屬表面的粗糙度和痕量蝕刻參數(shù)。

定制視圖:用來(lái)設(shè)置從其他標(biāo)簽派生的電子數(shù)據(jù)表信息的自定義視圖,并可根據(jù)用戶偏愛進(jìn)行調(diào)整。

有關(guān)這些標(biāo)簽的高級(jí)詳細(xì)信息,請(qǐng)參閱“Hyperlynx”用戶指南。

現(xiàn)在我們來(lái)設(shè)置一個(gè)“Z0”為 50 歐姆的疊層,因?yàn)檫@是最常用的值。走線阻抗由走線的“Width”、參考平面上方的“Height”或“Dielectric thickness”以及“Dielectric constant”來(lái)決定。有多種方法來(lái)可設(shè)置疊層編輯器中的阻抗,然而我們將使用“Metal”標(biāo)簽來(lái)快速設(shè)置所需的阻抗。

打開“Stackup Editor”,然后單擊“View -> Calculate Z0”(如果未啟用,則啟用它)。這樣工具就可以基于疊加來(lái)自動(dòng)計(jì)算特征阻抗了。

如下所示,選擇“Metal”標(biāo)簽,然后設(shè)置“電介質(zhì)厚度”,并將信號(hào)層標(biāo)記為“Z0”。

確保在您修改參數(shù)后,“Picture”面板中顯示“No errors found in stackup”的消息。

通過“Z0 Planning”標(biāo)簽來(lái)檢查單跡和差分對(duì)的目標(biāo)阻抗所需的走線寬度和間距。這個(gè)步驟很有用,由于接口/協(xié)議具有不同的阻抗要求,因此此標(biāo)簽有助于理解要滿足這些規(guī)格所需的寬度或間距。

1. 適用于單跡:從“Plan for”下拉列表中選擇“單跡”,并在信號(hào)層的“Target Z0”值列中輸入 50、60、40、50,然后按“Enter”鍵。實(shí)現(xiàn)這些阻抗所需的“Trace”寬度隨即會(huì)被更新。

2. 適用于差分對(duì):從“Plan for”下拉列表中選擇“差分對(duì)”,在“Strategy”中選擇“Solve for width”,然后在信號(hào)層的“Target Z0”值列中輸入 100、90、80、100。現(xiàn)在按“Enter”鍵。實(shí)現(xiàn)這些阻抗所需的“Trace”寬度隨即會(huì)顯示。也可以按照差分走線分離策略,通過選擇“Solve for Separation”的方法來(lái)滿足“Target Z0”的需要。此策略還包括使用兩者(即“Solve for width”和“Solve for Separation”)的選項(xiàng),并在“Z0 Curve”列中顯示結(jié)果。

堆棧現(xiàn)已創(chuàng)建,可將其導(dǎo)出以便在將來(lái)進(jìn)行設(shè)計(jì)和仿真時(shí)重用,從而節(jié)省時(shí)間。單擊“File -> Export -> save as .stk file”

單擊“OK”關(guān)閉編輯器。

注意:PCB 設(shè)計(jì)的疊層創(chuàng)建是設(shè)計(jì)進(jìn)程中最重要和最關(guān)鍵的步驟之一,需要根據(jù)復(fù)雜性投入所需的時(shí)間和精力。“What If”分析可以在編輯器中根據(jù)設(shè)計(jì)和制造要求使用,以實(shí)現(xiàn)最終的疊加。但是,上述步驟旨在深入了解編輯器,并僅針對(duì)本系列中提及的未來(lái)設(shè)計(jì)和仿真提供疊加。這些步驟不基于任何設(shè)計(jì)參數(shù)。

接下來(lái)你們可以通過我們上面討論的步驟來(lái)熟悉這些工具和接口。

在下一篇文章中,我們將介紹 Hyperlynx? 的其他一些功能,為您提供如何使用該工具的基礎(chǔ)知識(shí)。

在那之前,好好熟悉一下這個(gè)工具及各種設(shè)置,我們下次再見。

編輯:hfy

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4697瀏覽量

86107 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1416瀏覽量

95574

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

HYPERLYNX 仿真工具使用指南

[推薦]信號(hào)完整性仿真應(yīng)用技術(shù)高級(jí)研修會(huì)

信號(hào)完整性仿真應(yīng)用

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

Hyperlynx對(duì)PCB信號(hào)完整性仿真

高速電路信號(hào)完整性分析與設(shè)計(jì)—信號(hào)完整性仿真

基于HyperLynx的高速DSP信號(hào)完整性仿真

信號(hào)完整性與電源完整性仿真分析

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

信號(hào)完整性與電源完整性的仿真

信號(hào)完整性仿真實(shí)驗(yàn):Hyperlynx?調(diào)用及兩種仿真工作流程

信號(hào)完整性仿真實(shí)驗(yàn):Hyperlynx?調(diào)用及兩種仿真工作流程

評(píng)論