簡介與視頻示例設計概覽

許多視頻 IP 核都附帶有示例設計。這些設計用于 IP 演示,并提供示例以供您在自己的設計中使用 IP 核時作為參考。

這些 IP 示例設計的介紹請參閱 IP《產品指南》第 5 章。

在IP主頁上,Document Navigator 或視頻設計中心內可找到《產品指南》。

HDMI VCU118 示例設計簡介

賽靈思 HDMI IP 核分為兩種:源端 (Source) IP 核 (HDMI 1.4/2.0 TX Subsystem) 和 Sink IP 核 (HDMI 1.4/2.0 RX Subsystem)。

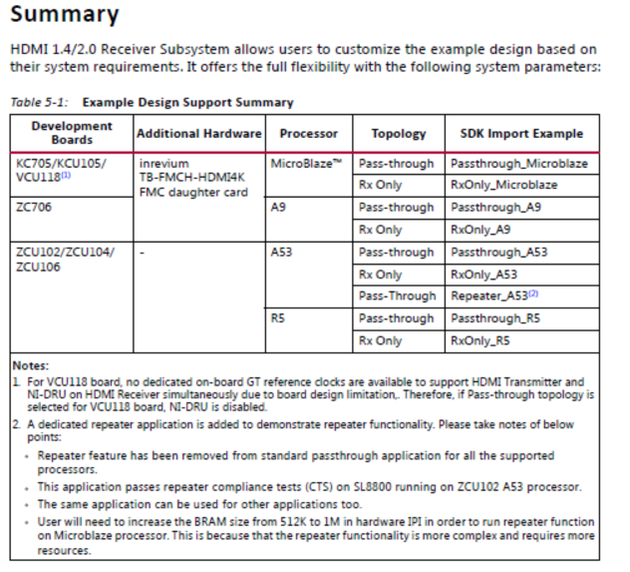

這些 IP 核的介紹請參閱 (PG235) 和 (PG236)。《產品指南》第 5 章中包含HDMI 1.4/2.0 示例設計的表格。

通過該表可以看到,其中包含 VCU118 示例設計,但不含 VCU128 示例設計。

注意:如該表所示,傳遞模式下無 DRU 時鐘可用,因為并無任何振蕩器引腳信號輸出至 HDMI 核附近 bank 中的 gtrefclk。

以下是我將 HDMI VCU118 設計移植到 VCU128 開發板時所使用的步驟。這些步驟僅作為示例以供參考,并非唯一方法。

1. 移植設計的第一步是確保已構建新硬件平臺用于為設計提供支持。

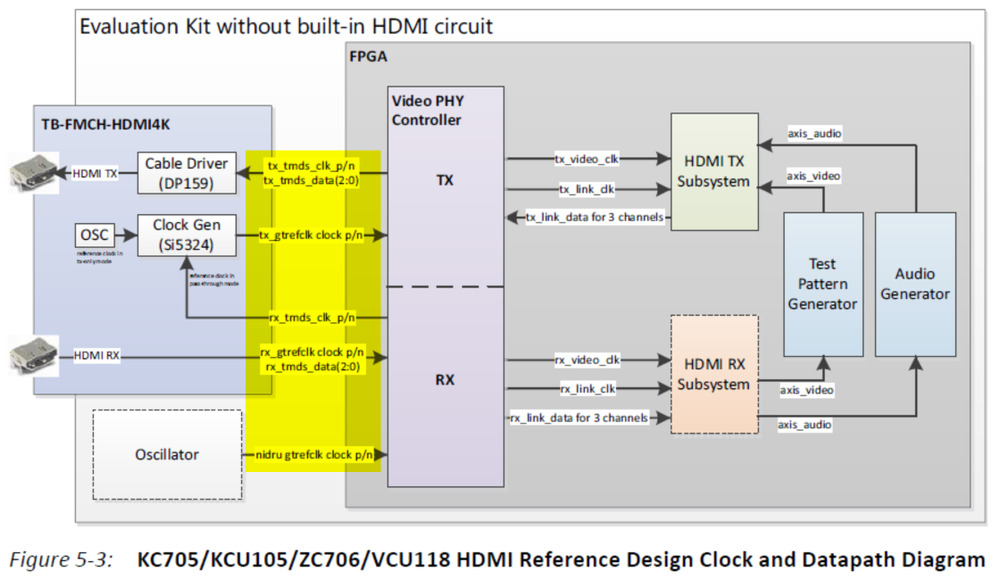

最好首先羅列出 HDMI 設計要求。通過使用《產品指南》中的圖 5-3 并聚焦高亮的 I/O,設計要求一目了然。

注意:VCU118 與 VCU128 開發板都不具有 nidru gtrefclk。

設計要求列表:

TMDS 時鐘引腳信號已輸出至 FMC

已通過 3 個 GT 引腳將發射器數據引腳信號輸出至 FMC

發射器參考時鐘引腳信號已從 FMC 輸入

接收器參考時鐘引腳信號已輸出至 FMC

接收器參考時鐘引腳信號已從 FMC 輸入

已通過 3 個 GT 引腳將接收器數據引腳信號輸出至 FMC

**請核實周圍各 bank 以確認是否存在可編程 NI-DRU 時鐘源

2. 已知設計要求情況下即可檢查 VCU128 以確認是否已滿足這些要求。

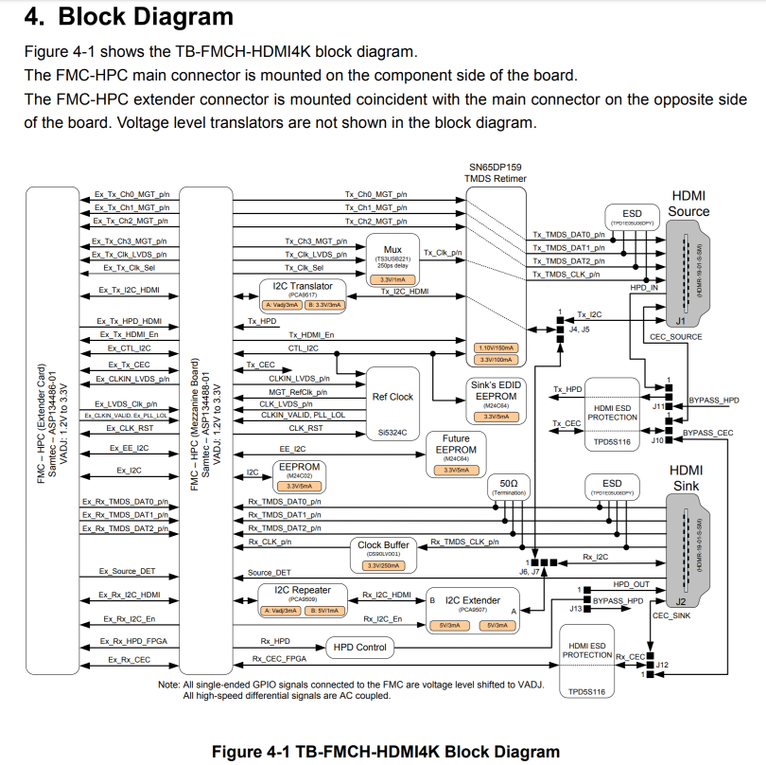

為此,我們可以查閱 VCU128 原理圖、VCU128 開發板用戶指南以及wikipinout.xml 并對比FMC 文檔(如下圖所示)

通過使用上述文檔即可將列表轉換為引腳名稱。

M2C -> 夾層卡到載卡(FMC -> 開發板)

C2M -> 載卡到夾層卡(開發板 -> FMC)

TMDS 時鐘引腳信號已輸出至 FMC -> LA27_P

已通過 3 個 GT 引腳將發射器數據引腳信號輸出至 FMC -> DP0_C2M_P 至 DP2_C2M_P

發射器參考時鐘引腳信號已從 FMC 輸入 -> GBTCLK1_M2C_P

接收器參考時鐘引腳信號已輸出至 FMC -> LA00_CC_P

接收器參考時鐘引腳信號已從 FMC 輸入 -> GBTCLK0_M2C_P

已通過 3 個 GT 引腳將接收器數據引腳信號輸出至 FMC -> DP0_M2C_P 至 DP2_M2C_P

**請核實周圍各 bank 以確認是否存在可編程 NI-DRU 時鐘源

bank124 周圍無可用時鐘

通過查看設計可以發現,在圖 5-3 中并未顯示全部引腳。

Si5324 RST

FMC_IIC_SCL

FMC_IIC_SDA

rs232_uart_rxd ->UART0_RXD

rs232_uart_txd ->UART0_TXD

reset -> CPU_Reset

RX_DDC_OUT_scl_io ->LA16_P

RX_DDC_OUT_sda_io ->LA16_N

TX_DDC_OUT_scl_io->29_P

TX_DDC_OUT_sda_io->29_N

TX_EN_OUT ->LA26_P

TX_CLK_SEL_FPGA -> LA18_CC_P

用于選擇是否使用第 4 個 GT 或 LVDS 引腳作為 HDMI TMDS 時鐘。

RX_HPD_OUT -> LA20_N

RX_I2C_EN_N_OUT -> LA22_P

RX_DET_IN -> LA03_P

SI5324_LOL_IN ->LA02_N

TX_HPD_IN -> LA31_N

3. 鑒于已知 I/O 引腳存在并且已正常連接到 FMC,下一步即可構建 VCU118 示例設計。

注意:該過程的介紹請參閱《產品指南》第 5 章。

4. 完成設計構建后,需要更新所有 VCU118 特定參數。這樣在更改部件號時,連接將保持斷開狀態。

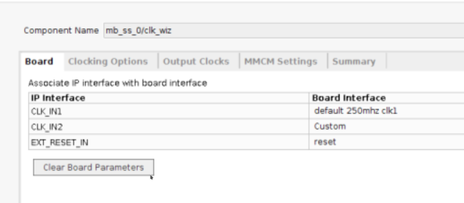

在此設計中,MMCM 是直接以 VCU118 為目標的唯一 IP。

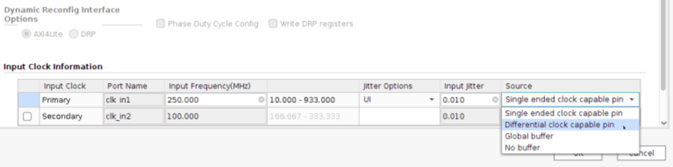

4.1. 打開 mb_ss_0 塊并打開時鐘向導 (clk_wiz)。

4.2. 單擊“Clear board parameters”以清空開發板參數。這將刪除 VCU 特定參數。

4.3. 將“Source”更新為“Differential clock capable pin”,然后保存塊設計

5. 設置新項目目標 -> VCU128 (XCVU37P-L2FSVH2892E)

6. 將 IP 更新到新項目

打開 IP 集成器、選擇報告 IP 狀態,然后升級所有 IP。

驗證其中不存在任何錯誤。

注意:不保證這對所有設計或移植都有效。如果此步驟無效,請使用先前的設計作為示例并手動構建新項目.

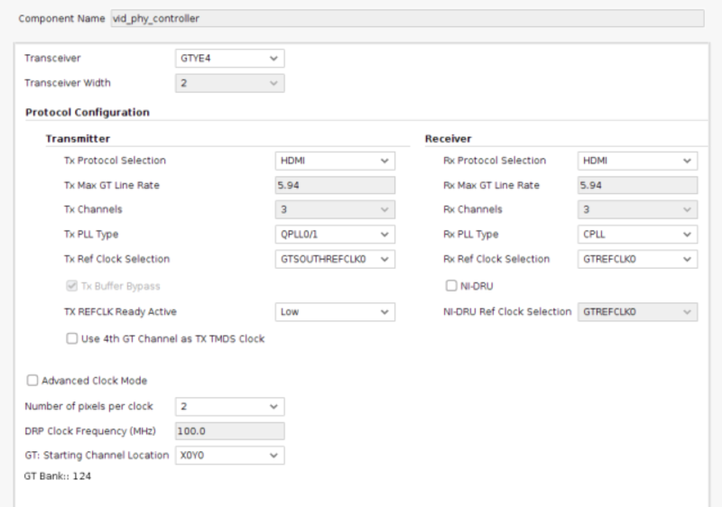

7. 鑒于當前項目目標為 VCU128 并且 IP 已升級,我們需要編輯 VPHY,設置正確的 bank 目標并使用正確的時鐘。

通過 VCU128 文檔可知,所使用的 GT 位于 bank 124 中。Bank 124 為 X0Y0。

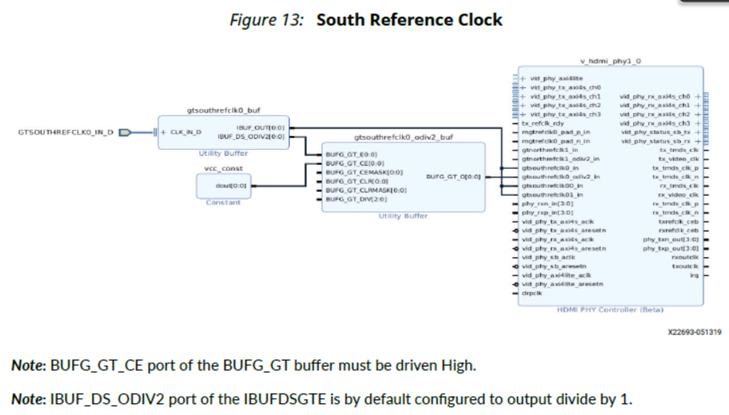

由于 GT 位于 bank 124 中,但當前使用的 TX reference0 時鐘來自 bank 125,因此需要將參考時鐘設置為 southrefclk0。

由于當前使用的是 North/South refclk,因此需根據 (PG230) 《Vivado PHY 控制器產品指南》中所述更新管腳。

8. 請核實連接狀態,確保所有引腳均已連接,然后驗證設計并運行綜合。

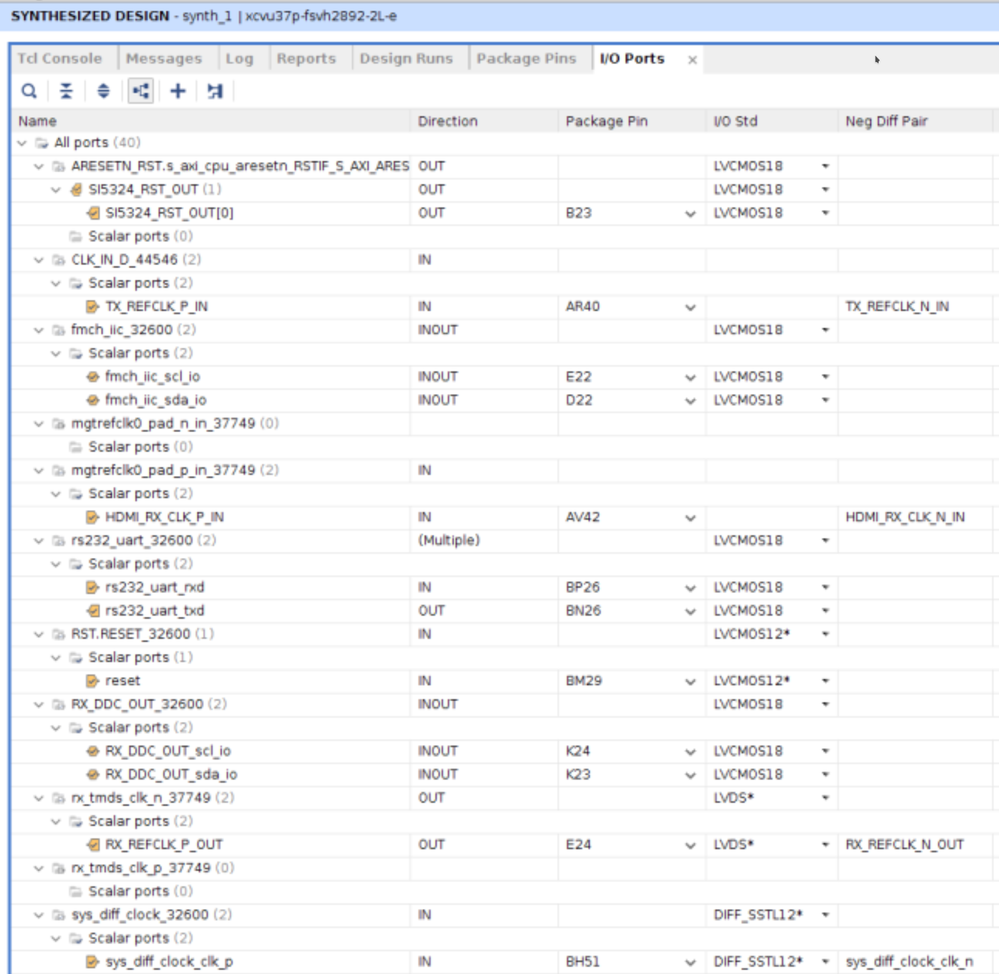

9. 完成綜合后,即可更新約束。

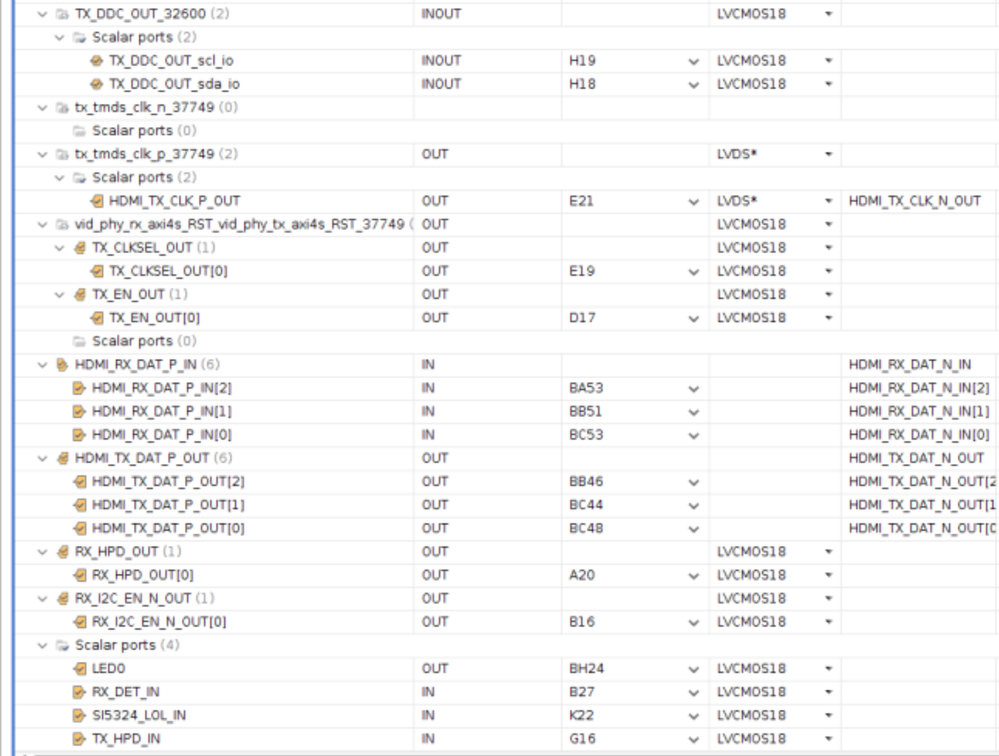

打開 Synthesized Design,依次單擊“layout -> I/O planning”。

在此視圖中,選擇 I/O 端口,然后使用新管腳對其進行更新。(GT TX/RX 引腳將已填充完成)

完成操作后,請保存以便更新約束文件 (.xdc)。

10. 約束更新完成后,請運行實現并生成比特流。

11. 導出硬件用于 SDK。

單擊“File -> Export Hardware

12. 最后,針對 VCU118 使用相同流程來構建應用示例設計。

打開 SDK

新建 BSP (File -> New SDK)

單擊 MSS 標簽,選中 HDMI 1.4/2.0 RX Subsystem 驅動程序,然后單擊“Import Examples”。

在打開的標簽中,單擊“Passthrough MicroBlaze”。

這將生成軟件項目。對其執行構建,這樣即可創建 ELF。

13. 大功告成!在硬件中執行測試以驗證移植的示例設計是否正常運行

編輯:hfy

-

HDMI

+關注

關注

32文章

1734瀏覽量

152277 -

振蕩器

+關注

關注

28文章

3847瀏覽量

139310 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131459

發布評論請先 登錄

相關推薦

新能源汽車VCU電控開發——能量回收模塊

福田汽車VCU推動智慧運輸邁向新高度

ADS54J64EVM開發板可以配套使用哪些Xilinx FPGA開發板呢?

VCU驅動行駛功能策略

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

整車控制器VCU應用層算法開發流程

新能源汽車之整車控制器VCU到底有什么用?

從0到1實現VCU:新能源汽車整車控制器

ELF 1技術貼|如何將Python3.6.9移植到開發板上

HDMI VCU118設計移植到VCU128開發板的步驟解析

HDMI VCU118設計移植到VCU128開發板的步驟解析

評論