這次我們將演示 RF Data Converter IP 設計仿真測試激勵文件示例。

本篇博文旨在演示其構建方式及其用于實踐 IP 的機制。我覺得這部分內容值得講一講,因為只要您能夠充分理解測試激勵文件,就可以將其作為有效的模板來用于將 RF Data Converter IP 構建到自己的仿真設置中。

我并不會細講這里的所有內容,只是為了演示一下仿真的機制。當然,您也可以自行深入分析測試激勵文件 RTL。

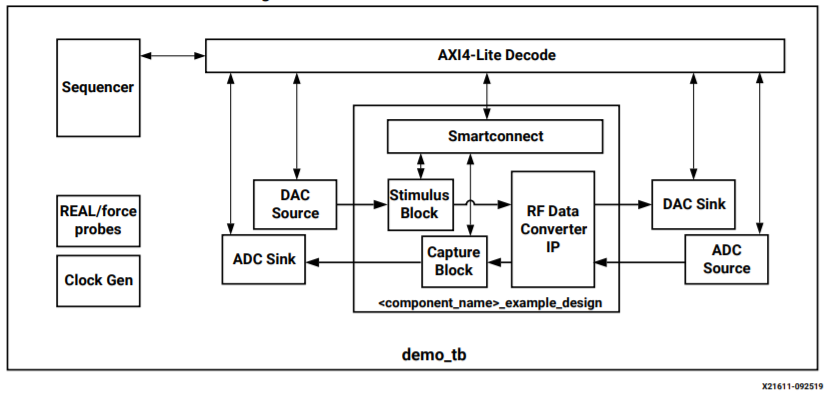

您可能已經知道,IP 設計示例隨附有完整的測試激勵文件。此測試激勵文件可在仿真中提供激勵生成和采集,用于 ADC 和 DAC 實踐。仿真具有內置自檢功能,因此它可用于檢驗您的 IP 設置。

讓我們來簡單了解下設計測試激勵文件示例。

從 IP 設計示例層面上來看,不僅有 IP,還有激勵塊和采集塊(均為大型塊 RAM 數組)。

此外還有 1 個 SmartConnect 塊用于連接到 IP 的 AXI4-Lite 端口。

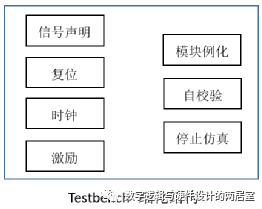

因此,測試激勵文件需提供的是:

時鐘生成,用于設計中的所有時鐘。ADC 和 DAC Tile 的輸入、AXI 流傳輸接口和 1 個 AXI4-Lite 接口。

加載激勵塊或源代碼塊的方法。

將“實數”信號應用于模擬輸入的方法,以及將實數信號從 DAC 轉換為數字總線以便檢查的方法。

最重要的是,需要 1 個定序器 (sequencer) 用于管理仿真。

檢驗采集塊或接收端 (sink) 塊的方法。

讓我們來看看測試激勵文件。測試激勵文件的所有源文件都包含在設計工程示例中的導入 (imports) 目錄中。

頂層測試激勵文件包含在 demo_tb.sv SystemVerilog 文件中。我們不會逐行詳細分析其中所有內容。在此級別只需連接各主要塊即可。讓我們來看下仿真功能的最重要的部分。

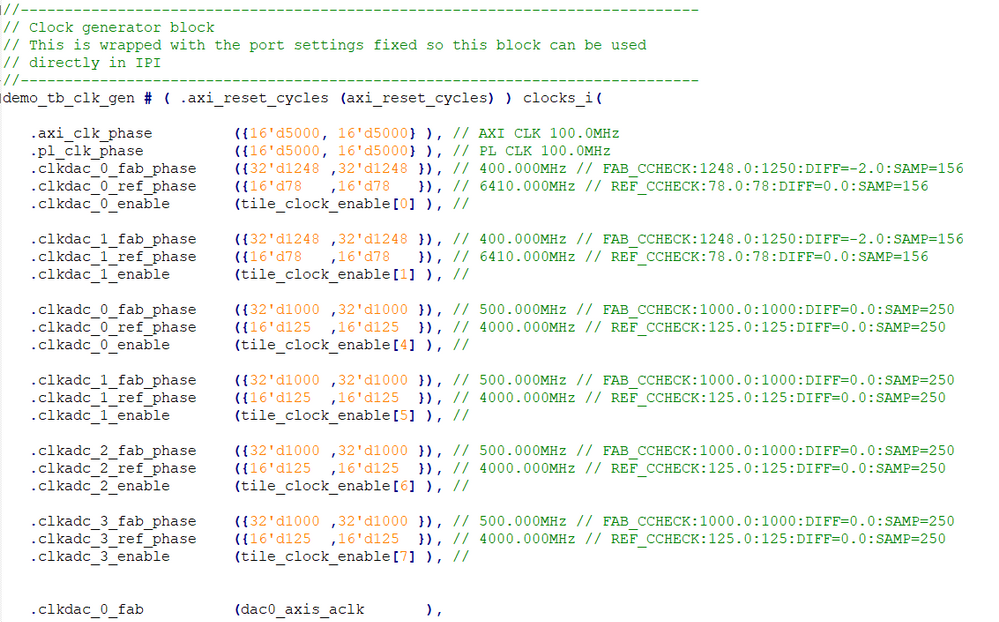

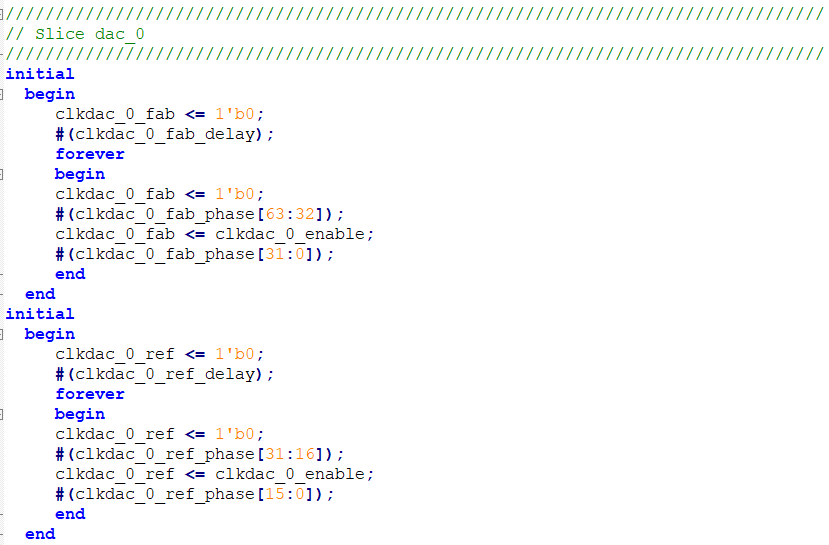

時鐘生成

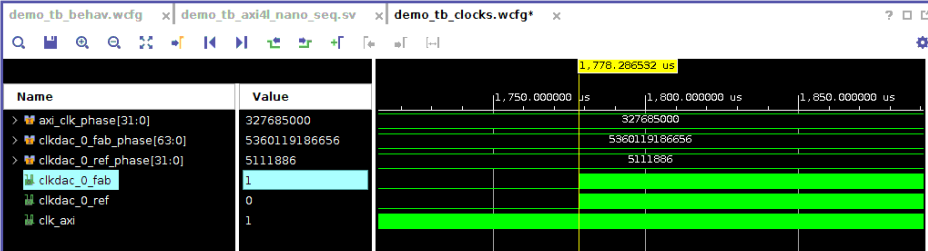

有一個非常簡單的模塊可用于在仿真中創建所有必要的時鐘信號。其中的輸入帶有_phase后綴,支持用戶為時鐘設置高低時間。它用于為每個 Tile 和 AXI Stream 時鐘創建所期望的頻率。

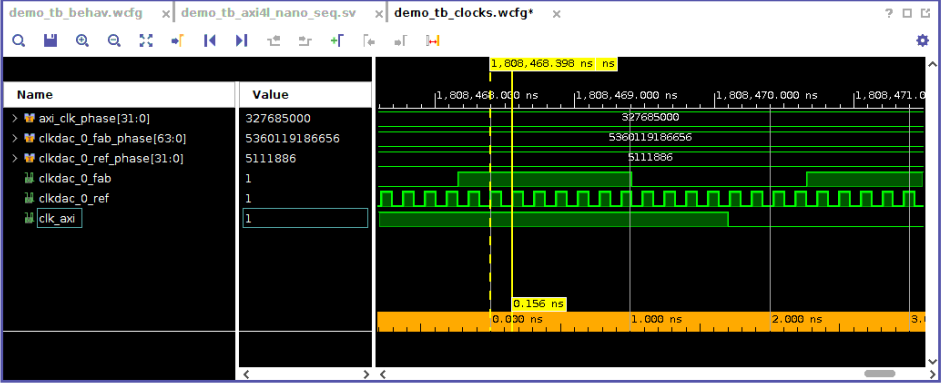

我們可在仿真中對此進行檢查,確保它按我們期望的方式運行。

在此情況下可以看到,DAC 采樣時鐘以 6.4GSPS 運行,而 AXI stream 傳輸時鐘的運行速率為該速率除以 16。

激勵生成

在仿真中,ADC 和 DAC 將分別單獨處理。在此情況下并不執行環回。

DAC 與 ADC 來源相同。

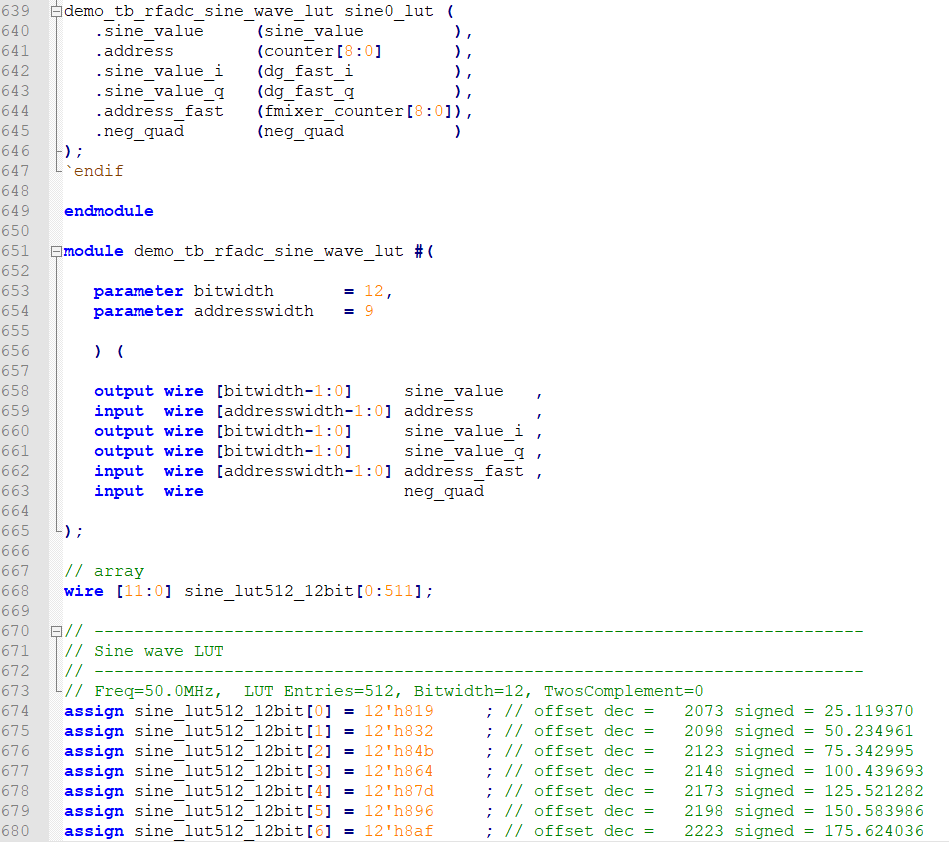

ADC 包含demo_tb_rfadc_data_source.sv,其中包含demo_tb_rfadc_tile_source.sv。在代碼中,我們提供的是正弦查找表 (LUT)。在此情況下,將循環此 LUT 并生成正弦波輸出。

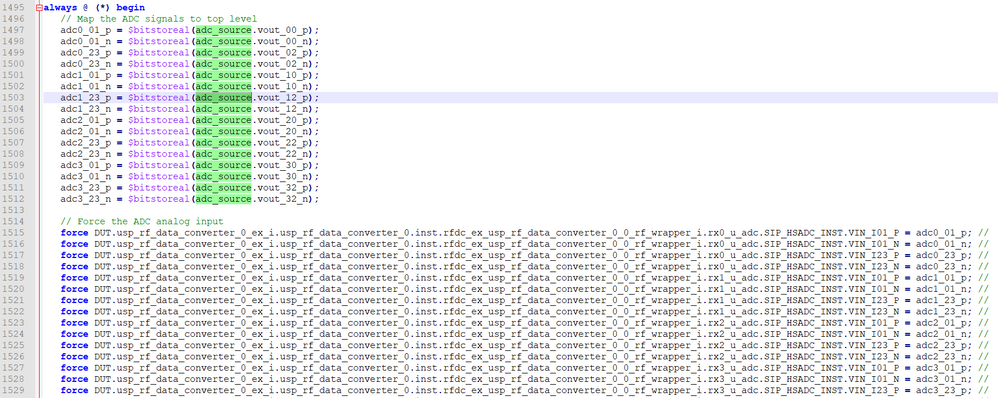

此正弦波將輸出到測試激勵文件的頂層。我們可將其轉換為實數,以便將其強制添加到demo_tb中的 Tile 的 UNISIM 模型層的模擬信號輸入中。

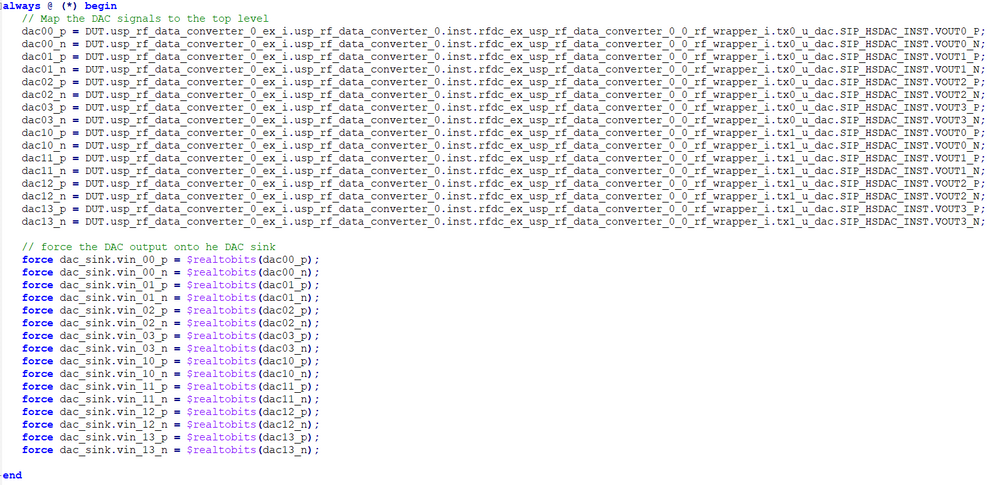

對于 DAC,只需將此數據寫入設計示例中的 DAC 源塊上的 AXI 接口即可。在demo_tb層級上,我們可將 DAC 模擬信號從實數轉換為位數,并將其應用于 DAC 接收端輸入。

測試激勵文件定序器

鑒于時鐘正在運行仿真,并且先前已經講解過數據源相關內容,因此我們可以繼續講解測試激勵文件的主要部分。

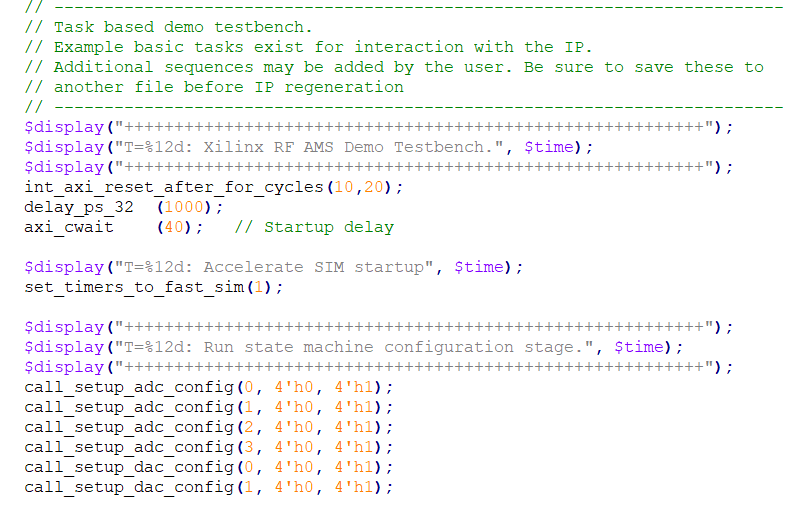

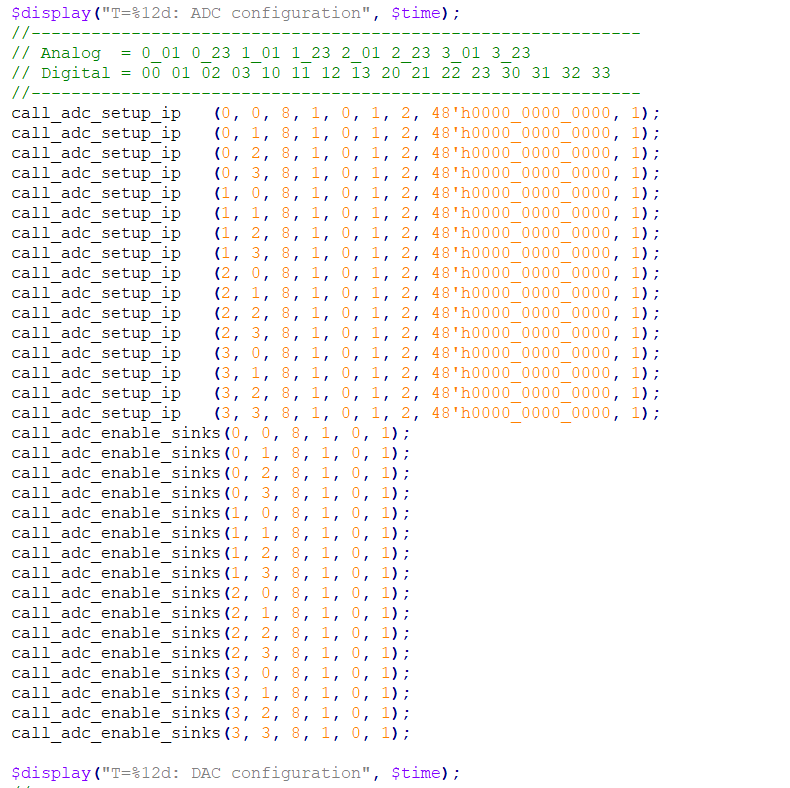

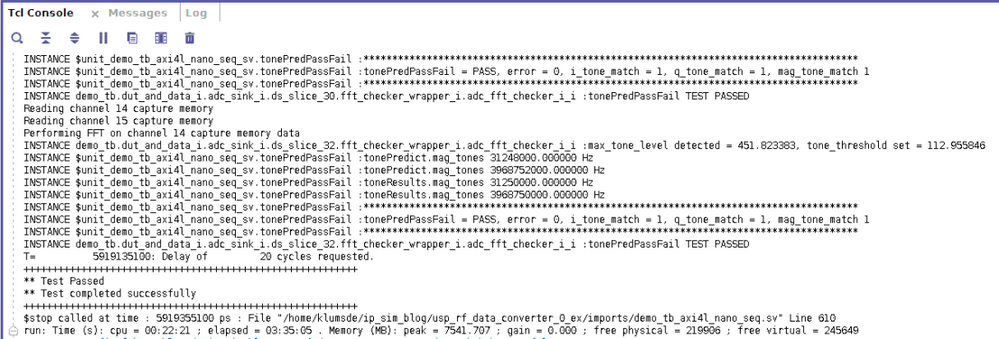

在demo_tb_axi4l_nano_seq.sv文件中可以了解到仿真的設置和控制方式。此文件使用部分 SystemVerilog 任務以便于我們訪問 RF 的 Tile,并對其執行部分設置。此外還有其它任務可用來控制仿真。我們將演示仿真的整個過程,并根據需要來探討這些任務。

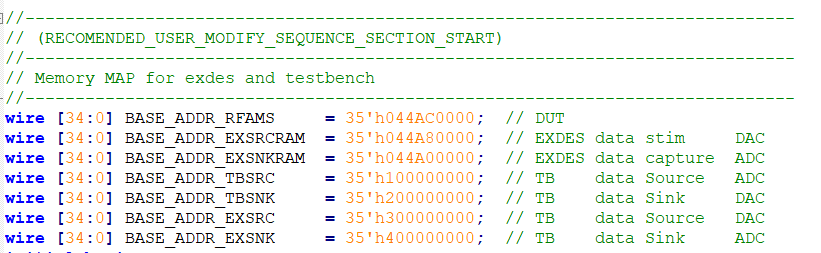

通過觀察此文件可以發現,它使用參數化尋址來允許我們處理測試激勵文件中 AXI4-Lite 上的各個子塊。各項任務將通過這些子塊來控制仿真。

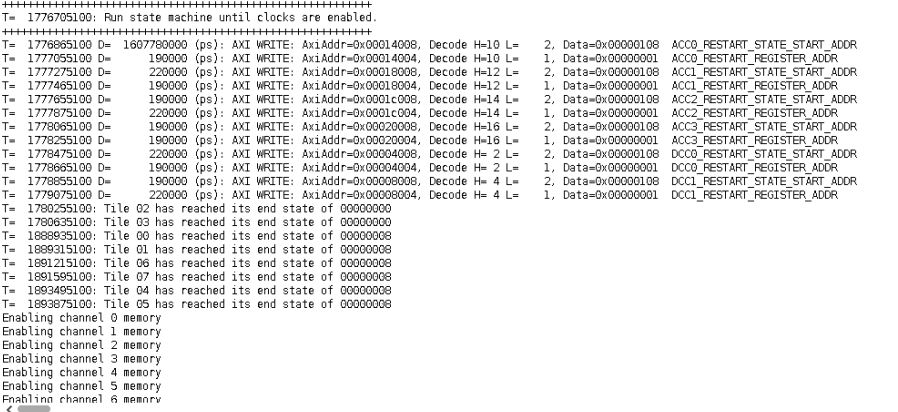

定序器 (Sequencer) 首先會對測試激勵文件中的所有一切都應用復位。然后它會對 Tile 執行寫入以啟用仿真加速。這樣即可縮短 Tile 的啟動時間,因為它可縮短電源微調時間以及 ADC 校準時間。仿真僅允許 Tile 達到 IP 的啟動狀態機的狀態 1。

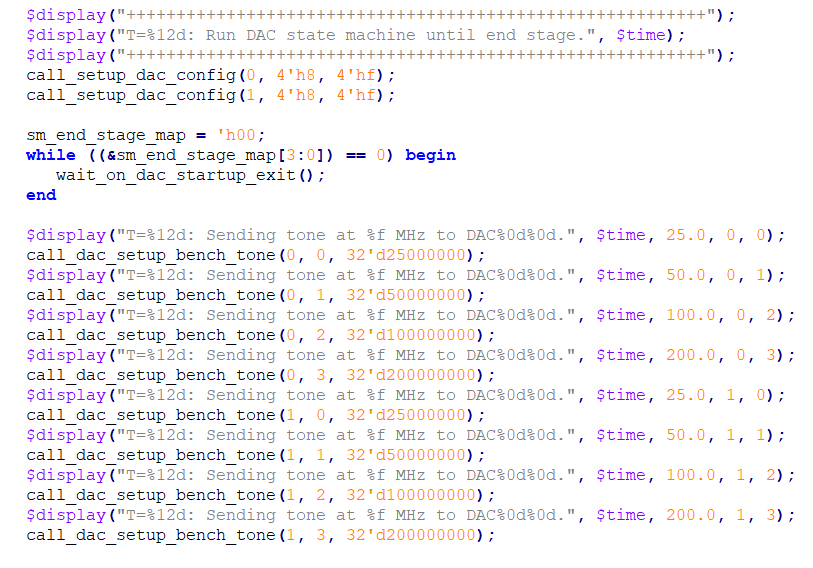

在此步驟后,它會對 Tile 執行某些設置,然后開始在測試激勵文件中開啟源端和接收端。它還會開始加載 DAC 源內存。

最好在執行每個步驟時都打印仿真時間。這樣即可根據需要檢查波形。

可以看到,IP 設置完成后,就會于 169us 附近開始寫入 DAC 激勵數據。DAC 源內存位于基址 0x300000000 處。

下一步,啟動 Tile 時鐘,并運行 ADC 和 DAC 直至時鐘檢測步驟為止。

完成此步驟后,即可啟動 DAC 源并運行 DAC,直至啟動 FSM 結束為止:

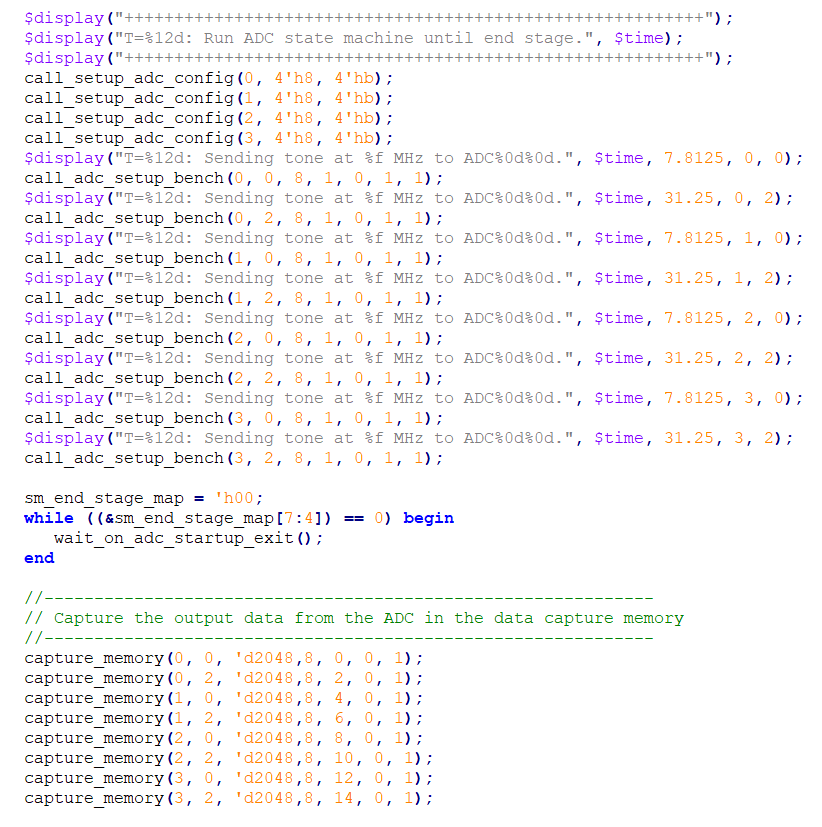

通過觀察波形可知,音調已傳入,而 DAC 輸出總線正在運行。

此處可看到 25Mhz/50Mhz/100Mhz/200Mhz。

然后,針對 ADC 重復此過程:

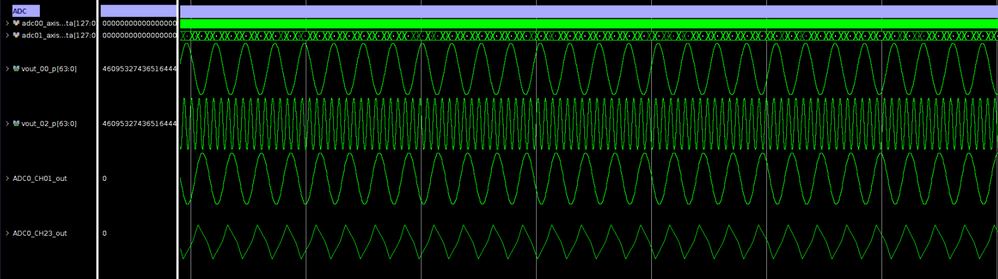

運行后,可在波形中查看結果。在此情況下,vout_00和vout02總線即為仿真中 ADC 源的輸出。

我在此處還附上了 AXI Stream 傳輸的 8 個采樣之一的截屏,以顯示 ADC 能正常轉換單音信號。

數據接收端和檢查器

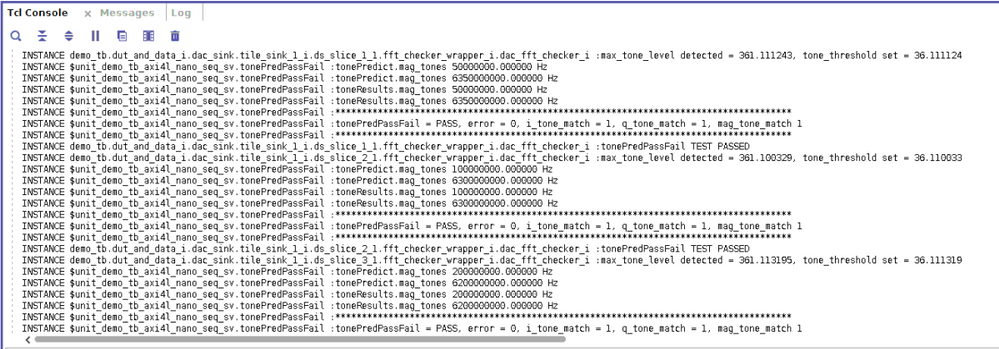

ADC 和 DAC 在demo_tb中具有一組接收端塊。

在這些塊中,將對數據進行縮放,并且將執行 FFT。這樣即可確認信號能以正確方式進行轉換。

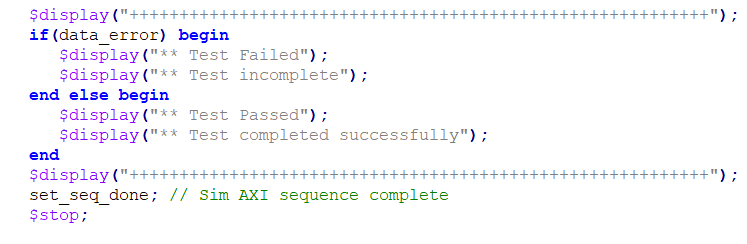

這些塊用于管理錯誤計數器。如果全部正確,那么定序器 (Sequencer) 就會停止仿真。

我希望本篇博文能夠幫助您更進一步了解 IP 仿真示例。此外還有很多內容值得分享,但本文應該能夠為大家提供一個良好的起點,以便大家了解仿真的工作原理,并且您可能還可以將其中部分技巧用于您自己的仿真測試激勵文件。

編輯:hfy

-

adc

+關注

關注

99文章

6531瀏覽量

545392 -

dac

+關注

關注

43文章

2307瀏覽量

191340 -

模擬信號

+關注

關注

8文章

1142瀏覽量

52560

發布評論請先 登錄

相關推薦

Efinity FIFO IP仿真問題 -v1

Modelsim仿真時候的data信號輸入問題

IP驗證增量仿真技術的運用

講解怎樣在VSS中使用LabVIEW RF Toolkit處理LTE激勵信號

加載激勵塊或源代碼塊的方法

FPGA中測試文件編寫中的激勵仿真

測試與驗證復雜的FPGA設計(2)——如何在虹科的IP核中執行面向全局的仿真

MAX17291B: High-Voltage Micropower Boost Converter Data Sheet MAX17291B: High-Voltage Micropower Boost Converter Data Sheet

MAX20471-MAX20472B: Low-Voltage Synchronous Boost Converter Data Sheet MAX20471-MAX20472B: Low-Voltage Synchronous Boost Converter Data Shee

ADRV9002: Dual Narrow/Wideband RF Transceiver Data Sheet ADRV9002: Dual Narrow/Wideband RF Transceiver Data Sheet

RF Data Converter IP設計仿真測試激勵文件原理

RF Data Converter IP設計仿真測試激勵文件原理

評論