在先進工藝和架構的協(xié)同下,芯片的性能在過去幾年獲得了爆發(fā)性的增長,尤其是在最近幾年火熱的人工智能行業(yè),這個取得的成就是有目共睹的。

據(jù)OpenAI在2018年年中發(fā)表的報告,自 2012 年以來,人工智能訓練任務中使用的算力正呈指數(shù)級增長。人們對于算力的需求增長也超過 300,000 倍。作為對比,如果是以摩爾定律的速度,這個數(shù)字只會是12倍的增長。在他們看來,正是這些硬件性能的跨越式突破,才成就了現(xiàn)在的AI產(chǎn)業(yè)。

自2012年以來,AI對算力的要求(source:OpenAI)

Open AI的報告進一步指出,成本考量和物理學特性等因素將會壓制傳統(tǒng)AI硬件性能的上升勢頭。但市場對AI算力的需求仍然處于增長期,為此探索新的硬件方案成為了AI芯片供應商亟待解決的問題。不少廠商也都另辟蹊徑從多個方向解決廣為人知的“馮諾依曼瓶頸”。

在鯤云信息科技有限公司創(chuàng)始人牛昕宇博士(以下簡稱牛博士)看來,一個不同于過往的新架構,是解決當前AI問題的正確之選。他同時也指出,目前的AI芯片行業(yè),需要變革的不僅僅是架構。

亟待變革的AI芯片架構

對AI芯片行業(yè)有所了解的讀者都應該知道,現(xiàn)在統(tǒng)治人工智能芯片市場的廠商主要是英偉達,依靠GPU優(yōu)秀的并行計算能力和CUDA生態(tài),這家本來只是做顯卡的廠商在人工智能時代大放異彩。

除了英偉達之外,擁有龐大部署量的英特爾至強處理器和聲名在外的谷歌TPU和特斯拉FSD也是AI芯片市場一個不可忽略的角色。這些處理器有一個共同特點,那就是他們無一例外采用了指令集架構處理器。

這些架構在實際應用中不能發(fā)揮人工智能芯片的全部算力潛力,為此牛博士指出,在算力需求猛增的AI時代,需要一種新的芯片架構,這主要是由以下兩個原因決定的:

從硬件架構上看,指令集架構芯片中有部分芯片面積用于支持指令控制。更關鍵的問題在于,在指令執(zhí)行過程中,計算單元在多數(shù)時間內(nèi)處于等待的狀態(tài):等待計算所需數(shù)據(jù)的到來。從這個角度看,指令集架構下的算力并沒有被充分發(fā)揮出來給到用戶。

另一方面,如上圖右邊所示,一個標準的五級指令集的每一條指令都要經(jīng)過讀取、解碼、執(zhí)行、讀寫內(nèi)存和把數(shù)據(jù)寫到寄存器里面去這五個步驟。在這些步驟中,只有執(zhí)行這一步驟是在執(zhí)行真正的計算。其他部分都是在做指令的讀取和解碼這樣的功能。雖然可以通過指令流水降低計算單元閑置,不過在實際執(zhí)行過程中,受限于指令間的依賴、以及指令間協(xié)同的時鐘不確定性,指令內(nèi)部的計算單元會出現(xiàn)閑置等挑戰(zhàn)。

牛博士舉例說到,英偉達T4在Batch=128或Batch最高的測試環(huán)境下,按照其官網(wǎng)公布的指標去比對幾個網(wǎng)絡實際的使用算力,得出的結果是峰值算力的7%到30%左右。這意味著產(chǎn)品有很大部分的性能還不能完全發(fā)揮出來。

“如果大家都在類似架構下競爭,在接近的芯片利用率前提下,芯片公司的產(chǎn)品升級最后會變成依賴制程工藝和軟件生態(tài)的比拼。而且,對比P4與T4產(chǎn)品的實測性能可以發(fā)現(xiàn),隨著峰值算力的增加,芯片的實際利用率有所降低”,牛博士補充說。

從目前的市場發(fā)展上看,包括英偉達在內(nèi)的多家AI芯片廠商都在沿著上述技術路線演進,但從當前制程工藝的發(fā)展和材料本身的特性限制看來,繼續(xù)大幅提升峰值算力意味著更高的芯片成本,而隨著峰值算力降低的芯片利用率意味著給到用戶的實測算力并不會等比例線性提升。這與當前AI應用客戶更高算力性價比的需求是相背而行的。換而言之,尋找一個新的AI芯片架構迫在眉睫。

“數(shù)據(jù)流架構或許會是一個不錯的選擇”,牛博士說。

根據(jù)他的觀點,所有的計算架構需要保證一個核心需求:加減乘除等計算操作能夠按照編程需求按特定次序完成對特定數(shù)據(jù)的計算。與傳統(tǒng)的馮·諾依曼架構或控制流體系結構進行對比,數(shù)據(jù)流架構并沒有指令相關的指令控制與執(zhí)行單元。數(shù)據(jù)流架構依靠數(shù)據(jù)流動次序,而不是指令執(zhí)行次序保證計算執(zhí)行順序,從而將計算與數(shù)據(jù)搬運重疊,以實現(xiàn)更高的吞吐量和更低的延遲。

“在指令集架構中,由于指令協(xié)同的不確定性,計算與數(shù)據(jù)讀寫無法深度重疊,部分時間計算單元處于等待數(shù)據(jù)狀態(tài),從而導致閑置計算單元和芯片利用率的下降。而數(shù)據(jù)流架構中每個時鐘下所有計算單元的狀態(tài)是確定的,計算單元無需等待其它單元的計算,從而消除計算資源閑置。”牛博士表示。“這就像一個交響樂團,當樂團中每個人都按照統(tǒng)一的拍子進行演奏時,而且每個人在每個拍子下的動作是確定的,樂團中的樂器之間并不需要相互等待,可以按照自己的節(jié)拍并行的演奏,就會協(xié)作完成一首曲子。這就像數(shù)據(jù)流架構中計算單元間的協(xié)作關系:通過精確的時鐘進行協(xié)作,而并不存在先后依賴關系,所以無需等待。”牛博士補充說。據(jù)介紹,數(shù)據(jù)流架構支持時鐘級的精確計算,讓每個數(shù)據(jù)流動及計算在每個時鐘都可精確預計,從而支持將數(shù)據(jù)流動與計算深度重疊,消除計算單元閑置;于此同時,數(shù)據(jù)流架構中沒有指令,從而破除了指令集架構的控制冗余以及等待指令讀取譯碼帶來的計算單元閑置問題,進一步提升芯片利用率。此外,數(shù)據(jù)流架構中一個數(shù)據(jù)流流水線中可深度整合大量計算單元,從而打破指令集架構中峰值算力提升與芯片利用率的沖突問題:通過不斷加深數(shù)據(jù)流流水線,可以在提升峰值算力同時,不降低流水線中計算單元閑置時間。”

正是因為數(shù)據(jù)流架構擁有如此多的優(yōu)勢,包括Wave Computing、SambaNova和Groq在內(nèi)的多家公司投入了這個領域的研發(fā),值得一提的是Groq的初創(chuàng)團隊還是由谷歌TPU的核心成員創(chuàng)立,由此可以看到數(shù)據(jù)流架構的前景。

當然,鯤云科技創(chuàng)始團隊自1994年就開始探索數(shù)據(jù)流架構在各個垂直領域的開發(fā)和落地,在數(shù)據(jù)流技術上具有深厚的積累,自然是這個架構的積極支持者。也正是在這個背景下,團隊創(chuàng)立了鯤云科技,從零開始探索針對深度學習的數(shù)據(jù)流架構,也就是CAISA。

AI芯片能力≠芯片峰值算力

在架構類似的情況下,峰值算力是一個可以簡單快速估算芯片實測性能的指標,也是在AI芯片設計中重點關注的指標。然而近幾年,提升峰值算力的發(fā)展方向?qū)⑷斯ぶ悄苄酒陌l(fā)展推向了另一個極端:峰值算力(或每瓦的峰值算力)已經(jīng)成為評價一顆AI芯片性能的單一指標,導致大量AI芯片研發(fā)資源投入到如何把峰值算力推高。

然而對于用戶來說,峰值算力其實并不是他們的本質(zhì)需求。

“用戶真正關心的是AI芯片的實測算力,而不完全是峰值算力。峰值算力并不能直接釋放給用戶,真正釋放給用戶的要乘上一個系數(shù),叫做芯片利用率”,牛博士說。“峰值算力指標假設每個芯片內(nèi)部計算單元每個時鐘都處于計算狀態(tài),而現(xiàn)有指令集架構在運算執(zhí)行中計算單元存在閑置”,牛博士強調(diào)。

以英偉達T4加速卡為例,常用的識別、檢測和分割的算法ResNet50、SSD-ResNet50和U-Net Industrial,在Batch=128或者最高性能的情況下,可以分別獲得32.1%、7.5%、11.9%的芯片利用率,這意味著在實際應用中,只有7%到32%的峰值算力轉換為實測性能釋放給用戶,當中帶來的芯片性能浪費是顯而易見的。

“為了讓用戶獲得更高的性能,除了持續(xù)提高峰值性能以外,芯片利用率的提升會是一個更好的方案,因為這會在不增加芯片成本的情況下,大幅提升芯片的實測性能。這也是鯤云科技新推出的CAISA 芯片正在努力的方向”,牛博士說。

這是一款采用28nm工藝打造的芯片,搭載了四個CAISA 3.0引擎,具有超過1.6萬個MAC(乘累加)單元,峰值性能可達10.9TOPs。而通過PCIe 3.0×4接口與主處理器通信,同時具有雙DDR通道,可為每個CAISA芯片提供超過340Gbps的帶寬。

作為一款面向邊緣和數(shù)據(jù)中心推理的人工智能芯片,CAISA芯片可實現(xiàn)最高95.4%的芯片利用率。這就讓他們在既滿足客戶在價格和功耗方面需求的同時,還能為客戶提供更強的算力,提高了性價比。而之所以能做到如此高的芯片利用率,與鯤云科技的CAISA 3.0數(shù)據(jù)流架構有莫大的關系。

在文章前面我們提到,鯤云科技首席科學家Wayne Luk陸永青院士從1994年就開始將數(shù)據(jù)流架構應用到各個垂直領域。經(jīng)歷了前十幾年的發(fā)展積累,到鯤云科技于2016年成立并在FPGA上實現(xiàn)交付,與客戶的交流迭代之后,完成了此次全新的架構升級。

來到CAISA3.0中,數(shù)據(jù)計算與數(shù)據(jù)流動的重疊,壓縮計算資源的每一個空閑時鐘;通過算力資源的動態(tài)平衡,消除流水線的性能瓶頸;通過數(shù)據(jù)流的時空映射,最大化復用芯片內(nèi)的數(shù)據(jù)流帶寬,減少對外部存儲帶寬的需求。上述設計使CNN算法的計算數(shù)據(jù)在CAISA3.0內(nèi)可以實現(xiàn)不間斷的持續(xù)運算,最高可實現(xiàn)95.4%的芯片利用率,在同等峰值算力條件下,可獲得相對于GPU 3倍以上的實測算力,從而為用戶提供更高的算力性價比。

相比旗艦款Xavier加速卡,搭載CAISA芯片的星空加速卡X3可以最高提供4.12倍實測性能提升;而與T4相比,鯤云科技也能提供最高3.91倍實測性能提升。這都是超高的芯片利用率提升所帶來的。得益于這個利用率,過往通過提升峰值性獲得更高性能而帶來的高成本問題,也迎刃而解。

也許很多人并沒有理解這個3.91倍背后的意義,讓我們舉個現(xiàn)有的例子來對比說明一下。

AI從業(yè)人員都知道,英偉達為了展現(xiàn)其T4的實力,在其官方網(wǎng)站上公布了這個加速卡跑在不同網(wǎng)絡模型下的性能指標。作為AI芯片行業(yè)的風向標,任何一款芯片想要說明自己的實力,只需要跑和T4一樣的網(wǎng)絡,然后公布相關的Benchmark就可以如愿以償。早前被英特爾收購的Habana就是這樣做的。根據(jù)Habana所公布benchmark性能,相比于T4官網(wǎng)指標(最新官網(wǎng)指標為5415FPS),通過更高的峰值算力,Habana的產(chǎn)品提供了2.85倍實測性能提升。正是因為在實測性能上取得的領先,最終獲得Intel的青睞,讓他們以20億美元的估值被收購。

通過這個例子,我們也可以看到鯤云科技這個數(shù)字的真正價值。

在這個高性能芯片的支持下,鯤云科技打造了高算力性價比的AI計算平臺星空加速卡系列,并推出了X3和X9兩款產(chǎn)品。

其中星空X3加速卡是搭載單顆CAISA 芯片的數(shù)據(jù)流架構深度學習推斷計算平臺,為工業(yè)級半高半長單槽規(guī)格的PCIe板卡。得益于其輕量化的規(guī)格特點,X3加速卡可以與不同類型的計算機設備進行適配,包括個人電腦、工業(yè)計算機、網(wǎng)絡視頻錄像機、工作站、服務器等,滿足邊緣和高性能場景中的AI計算需求。相較于英偉達邊緣端旗艦產(chǎn)品Xavier,X3可實現(xiàn)1.48-4.12倍的實測性能提升。

X9加速卡為搭載4顆CAISA 芯片的深度學習推斷板卡,峰值性能43.6TOPS,主要滿足高性能場景下的AI計算需求。同英偉達旗艦產(chǎn)品T4相對,X9在ResNet-50, YOLO v3等模型上的芯片利用率提升2.84-11.64倍。在實測性能方面,X9在ResNet50可達5240FPS,與T4性能接近,在YOLO v3、UNet Industrial等檢測分割網(wǎng)絡,實測性能相較T4有1.83-3.91倍性能提升。在達到最優(yōu)實測性能下,X9處理延時相比于T4降低1.83-32倍。實測性能以及處理延時的大幅領先,讓數(shù)據(jù)流架構為AI芯片的發(fā)展提供了提升峰值性能之外的另一條技術路線。

據(jù)了解,目前星空X3加速卡已經(jīng)推出市場,而星空X9加速卡將于今年8月推出市場。

全球首個數(shù)據(jù)流AI芯片背后

從行業(yè)的現(xiàn)狀看來,鯤云科技是全球首家推出數(shù)據(jù)流AI芯片,并且提供第三方實測benchmark的中國芯片企業(yè)。這是前文說到的Wave Computing、SambaNova和Groq等國外明星初創(chuàng)企業(yè)所不能達到的成就。而通過數(shù)據(jù)流網(wǎng)絡中算子的不同配置和組合,鯤云科技的CAISA芯片更可支持到絕大多數(shù)的CNN算法,并能讓開發(fā)者輕易地將模型遷移到這個平臺上。。

能做到這樣,是其架構和軟件相互協(xié)同獲得的成果。

CAISA3.0架構可以通過流水線動態(tài)重組實現(xiàn)對不同深度學習算法的高性能支持。通過CAISA架構層的數(shù)據(jù)流引擎、全局數(shù)據(jù)流網(wǎng)、全局數(shù)據(jù)流緩存,以及數(shù)據(jù)流引擎內(nèi)部的人工智能算子模塊、局部數(shù)據(jù)流網(wǎng)、局部數(shù)據(jù)流緩存的分層設計,在數(shù)據(jù)流配置器控制下,CAISA架構中的數(shù)據(jù)流連接關系和運行狀態(tài)都可以被自動化動態(tài)配置,從而生成面向不同AI算法的高性能定制化流水線。在保證高性能的前提下,支持用戶使用基于CAISA3.0架構的計算平臺實現(xiàn)如目標檢測、分類及語義分割等廣泛的人工智能算法應用。

“專為CAISA3.0架構配備的RainBuilder編譯工具鏈支持從算法到芯片的端到端自動化部署”,牛博士強調(diào)。而在RainBuilder編譯工具鏈的支持下,用戶和開發(fā)者無需了解架構的底層硬件配置,簡單兩步即可實現(xiàn)算法快速遷移和部署。

據(jù)透露,RainBuilder編譯器可自動提取主流AI開發(fā)框架(TensorFlow,Caffe,Pytorch,ONNX等)中開發(fā)的深度學習算法的網(wǎng)絡結構和參數(shù)信息,并面向CAISA結構進行優(yōu)化;工具鏈中的運行時(Runtime)和驅(qū)動(Driver)模塊負責硬件管理并為用戶提供標準的API接口,運行時可以基于精確的CAISA性能模型,實現(xiàn)算法向CAISA架構的自動化映射,同時提供可以被高級語言直接調(diào)用的API接口;最底層的驅(qū)動可以實現(xiàn)對用戶透明的硬件控制。RainBuilder工具鏈使用簡單,部署方便,通用性強,可以讓用戶快速和低成本的部署和遷移已有算法到CAISA硬件平臺上。

回顧計算行業(yè)的發(fā)展,不同的應用催生了不同的處理器架構。早期PC的出現(xiàn),讓X86架構和Intel名揚天下;近十年移動設備的出現(xiàn),又推動了Arm架構和高通的蓬勃發(fā)展。

現(xiàn)在,我們進入了AI時代,也許一個屬于數(shù)據(jù)流處理器和鯤云科技的時代,從這刻開始正式上演。

責任編輯:tzh

-

處理器

+關注

關注

68文章

19404瀏覽量

230832 -

芯片

+關注

關注

456文章

51155瀏覽量

426371 -

AI

+關注

關注

87文章

31490瀏覽量

269931 -

人工智能

+關注

關注

1795文章

47642瀏覽量

239735

發(fā)布評論請先 登錄

相關推薦

適用于Oracle的SSIS數(shù)據(jù)流組件:提供快速導入及導出功能

Devart SSIS數(shù)據(jù)流組件

阿里國際推出全球首個B2B AI搜索引擎Accio

理解ECU數(shù)據(jù)流的分析方法

全球首個開源AI標準正式發(fā)布

請問TLV320AIC3254EVM-K怎么讀取音頻數(shù)據(jù)流?

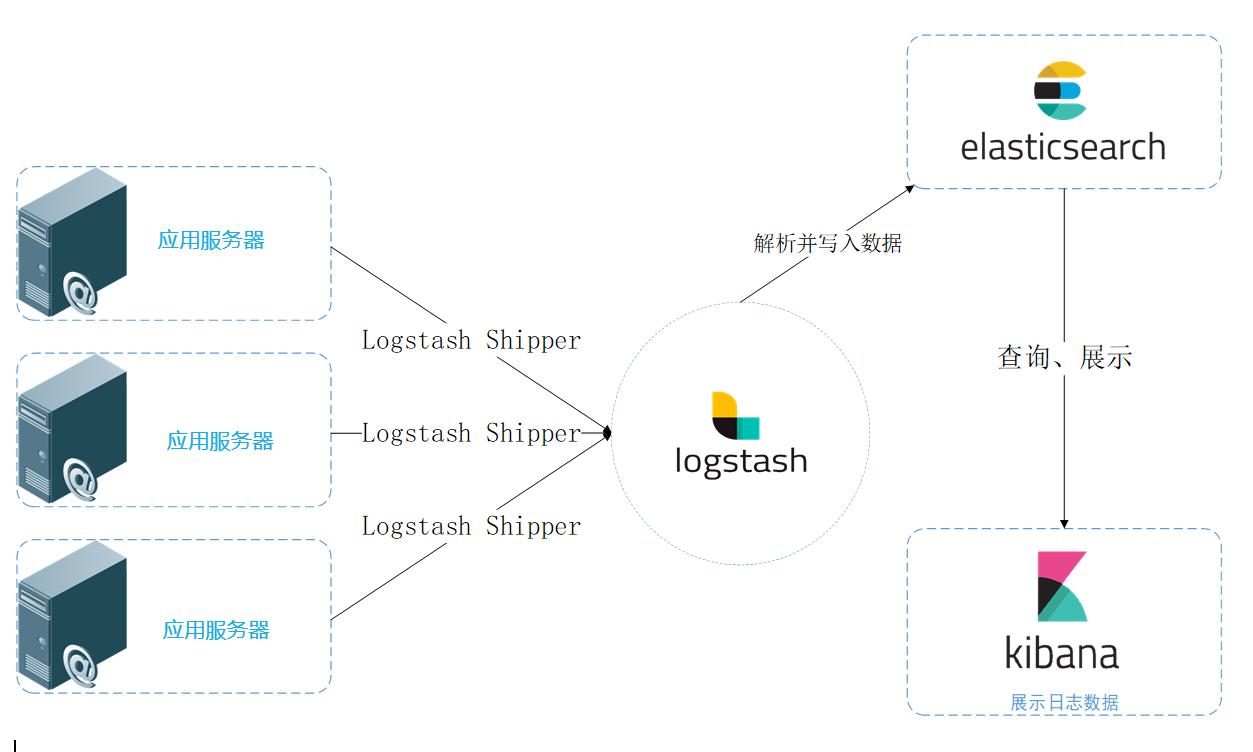

統(tǒng)一日志數(shù)據(jù)流圖

昆侖萬維發(fā)布全球首個AI流媒體音樂平臺Melodio

使用CYUSB3014實現(xiàn)USB3VISION,不能成功發(fā)送DSI數(shù)據(jù)流是怎么回事?

ESP32如何在不漏數(shù)據(jù)的情況下采集數(shù)據(jù)流?

全球AI芯片市場收入預計持續(xù)增長

探討全球首個數(shù)據(jù)流AI芯片的背后

探討全球首個數(shù)據(jù)流AI芯片的背后

評論