我們在對FPGA項目進行約束的時候,常常看到這樣的電平標準,例如LVCOM18,LVCOS25,LVDS,LVDS25等等,其實這些都是一系列的電平標準,為了更加深刻地理解電平標準,下面摘選自《FPGA之道》這本書對于電平標準的講解來理解。

所謂的雙閾值標準,是針對數字電路而言,數字電路表示電平的只有1和0兩個狀態,在實際的電路中,需要約定什么樣的電壓為1,什么樣的電壓為0。數字電路中的雙閾值是這樣定義的,例如TTL接口電平標準:

對于輸出端,狀態1的電壓要求為大于等于2.4V,狀態0的電壓要求為小于等于0.5V;

對于輸入端,狀態1的判定要求為大于等于2.0V,狀態0的判定要求為小于等于0.8V;

也就是需要大于某一個閾值表示電平1,小于某一個閾值表示電平0.

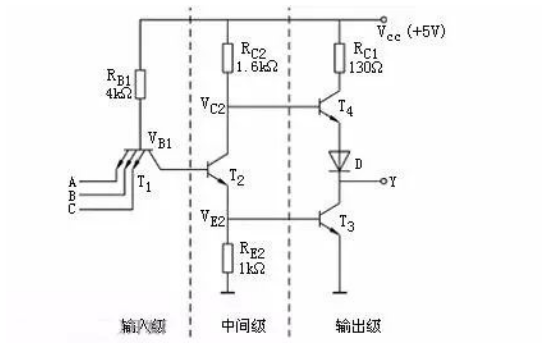

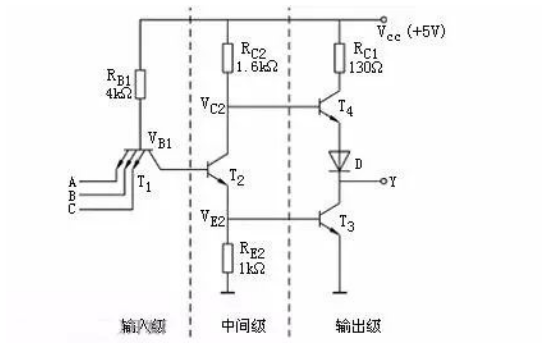

TTL是Transistor-Transistor Logic的英文縮寫,從其命名就可以看出,這種接口電平標準的初衷是用于基于三極管結構的數字系統之間的。

工作于TTL接口標準下的數字電路,其內部有源器件的標準電源供給應為5V,輸出、輸入情況如下:

對于輸出端,狀態1的電壓要求為大于等于2.4V,狀態0的電壓要求為小于等于0.5V;

對于輸入端,狀態1的判定要求為大于等于2.0V,狀態0的判定要求為小于等于0.8V;

對比輸出、輸入端的電壓要求,可以看出輸出端的電壓輸出要求要比輸入端的雙閥值判定標準更加嚴格,這樣做主要是考慮到噪聲的干擾以及電信號在輸出與輸入間的傳遞速度,從而讓雙閥值判定標準更加的可靠。

由于2.4V與5V之間還有很大空間,這對改善噪聲干擾并沒有什么明顯的好處,而且還會增加系統的功耗,并且由于數字狀態1、0之間電平相差較大,還會影響到數字電路的響應速度。因此后來就把TTL的電壓范圍進行了一些壓縮,從而形成了LVTTL——Low Voltage Transistor-Transistor Logic,也即低壓TTL電平標準。以下介紹兩種目前常用的LVTTL標準:

LVTTL3V3的意思,即其內部有源器件的標準電源供給為3.3V,輸出、輸入情況如下:

對于輸出端,狀態1的電壓要求為大于等于2.4V,狀態0的電壓要求為小于等于0.4V;

對于輸入端,狀態1的判定要求為大于等于2.0V,狀態0的判定要求為小于等于0.8V;

對比輸出、輸入端的電壓要求可知,為了保證雙閥值判定的穩定性和抗噪性,輸出端的電壓要求仍比輸入端的雙閥值判定標準要嚴格,這點對于所有的數字系統接口標準是一樣的,以后不再贅述。

LVTTL2V5的意思,即其內部有源器件的標準電源供給為2.5V,輸出、輸入情況如下:

對于輸出端,狀態1的電壓要求為大于等于2.0V,狀態0的電壓要求為小于等于0.2V;

對于輸入端,狀態1的判定要求為大于等于1.7V,狀態0的判定要求為小于等于0.7V。

CMOS是Complementary Metal Oxide Semiconductor的英文縮寫,從其命名就可以看出,這種接口電平標準的初衷是用于基于NMOS、PMOS組成的MOS管結構的數字系統之間的。

工作于CMOS接口標準下的數字電路,其內部有源器件的標準電源供給為5V,輸出、輸入情況如下:

對于輸出端,狀態1的電壓要求為大于等于4.45V,狀態0的電壓要求為小于等于0.5V;

對于輸入端,狀態1的判定要求為大于等于3.5V,狀態0的判定要求為小于等于1.5V。

CMOS與TTL接口相比,有了更大的噪聲容限,并且其輸入阻抗也遠大于TTL輸入阻抗。

同TTL一樣,鑒于功耗和響應速度的考慮,CMOS也同樣衍生出了LVCMOS接口標準,并且由于MOS管相對于三極管的導通門限更加低,因此LVCMOS比LVTTL更容易使用較低的電壓進行通信。以下介紹幾種目前常用的LVTTL標準:

LVCMOS3V3的意思,即其內部有源器件的標準電源供給為3.3V,輸出、輸入情況如下:

對于輸出端,狀態1的電壓要求為大于等于3.2V,狀態0的電壓要求為小于等于0.4V;

對于輸入端,狀態1的判定要求為大于等于2.0V,狀態0的判定要求為小于等于0.7V。

LVCMOS2V5的意思,即其內部有源器件的標準電源供給為2.5V,輸出、輸入情況如下:

對于輸出端,狀態1的電壓要求為大于等于2.0V,狀態0的電壓要求為小于等于0.4V;

對于輸入端,狀態1的判定要求為大于等于1.7V,狀態0的判定要求為小于等于0.7V。

LVCMOS1V8的意思,即其內部有源器件的標準電源供給為VCC=1.8V,當然這是有一定容忍度的,不過與之前介紹的電平標準不同,這個容忍度會影響它的輸出、輸入情況,介紹如下:

對于輸出端,狀態1的電壓要求為大于等于VCC-0.45V(若VCC精確等于1.8V,則為1.35V),狀態0的電壓要求為小于等于0.45V;

對于輸入端,狀態1的判定要求為大于等于0.65倍的VCC(若VCC精確等于1.8V,則為1.17V),狀態0的判定要求為小于等于0.35倍的VCC(若VCC精確等于1.8V,則為0.63V)。

LVCMOS1V5的意思,即其內部有源器件的標準電源供給為VCC=1.5V,它的容忍度也會影響到其輸出、輸入情況,介紹如下:

對于輸出端,LVCMOS1V5沒有明確的要求,但是肯定是狀態1越接近VCC越好,狀態0越接近0V越好;

對于輸入端,狀態1的判定要求為大于等于0.65倍的VCC(若VCC精確等于1.5V,則為0.975V),狀態0的判定要求為小于等于0.35倍的VCC(若VCC精確等于1.5V,則為0.525V)。

LVCMOS1V2的意思,即其內部有源器件的標準電源供給為VCC=1.2V,它的容忍度也會影響到其輸出、輸入情況,介紹如下:

對于輸出端,LVCMOS1V2也沒有明確的要求,但是肯定是狀態1越接近VCC越好,狀態0越接近0V越好;

對于輸入端,狀態1的判定要求為大于等于0.65倍的VCC(若VCC精確等于1.2V,則為0.78V),狀態0的判定要求為小于等于0.35倍的VCC(若VCC精確等于1.2V,則為0.42V)。

LVDS是Low Voltage Differential Signaling的縮寫,即低壓差分信號,其輸入、輸出與之前所介紹的接口電平都不同,它需要通過兩根線來完成通信。其工作原理如下圖所示:

上圖左部為LVDS輸出端,其內部有一個恒流源IS,大約恒定輸出3.5-4mA的電流值。最右邊的Vout接入LVDS的輸入端,而在靠近輸入端的地方并聯接入一個阻值為100歐的匹配電阻R。通過改變上圖雙刀雙擲開關的位置,而改變差分線上電流的方向,以此來表示數字狀態0和1,因此,接收端的差分線上將會由于電流方向的不同而表現出來±350mV的差分電平,并依次作為數字狀態的判定依據。上圖右側還有一個直流偏置電壓源VS,這主要是用來說明Vout的兩端其實一般都是正電壓的,實際電路中并沒有該項。

由于LVDS的電壓擺幅僅有350mV左右,電流也僅有3.5mA左右,而且又是差分傳輸,因此具有高速、超低功耗、低噪聲和低成本等優良特性。

RS232是美國電子工業協會EIA(全稱為Electronic Industry Association)制定的一種串行物理接口標準。RS是Recommended Standard的縮寫,中文意思為推薦標準,232為標識號。RS232總線標準共設有25條信號線,這里我們僅討論其數字電平接口判定標準。

RS232的標準電源供給為±12V或±15V,狀態1的電壓要求為-15V到-3V之間,狀態0的電壓要求為3V到15V之間。

RS485相當于RS232的升級版,與LVDS類似,RS485也是采用差分的形式來傳遞信息(不過RS485是真的傳了兩路電壓信號過去),因此抗干擾性要優于RS232。這里,我們同樣僅關心其數字電平接口判定標準。

RS485的狀態1,其兩線之間的電壓差要求為2V到6V之間;狀態0,其兩線之間的電壓差要求為-6V到-2V之間。

上面介紹了多種數字系統之間的接口電平標準,通常在使用的時候,還是強烈建議大家為數字系統接口的雙方選擇一致的標準。不過有時候受限于兩方的一些配置情況,可能并不能找出統一的電平標準來進行通信,那么此時,是不是除了設計接口轉換電路板以外就沒有別的方法了呢?并不是的,其實,有些不同的接口電平標準是可以兼容的。

首先單端和差分是不可能兼容的,因為從物理連線上它們就不一樣。但是對于同種類的接口,如果A電平標準的輸出符合B電平標準的輸入,那么就稱A的輸出可驅動B的輸入,如果反之亦然,那么稱A、B兩種電平標準可相互驅動。

例如,CMOS的輸出是可以驅動TTL輸入的,但是反之則不行,因為TTL的狀態1輸出僅為大于等于2.4V,并不能達到CMOS判決狀態1所需要的大于等于3.5V;但是LVTTL3V3和LVCMOS3V3卻可以相互驅動,因為它們的輸出都能滿足彼此的輸入判定要求。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:數字系統之間的接口電平標準

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

相關推薦

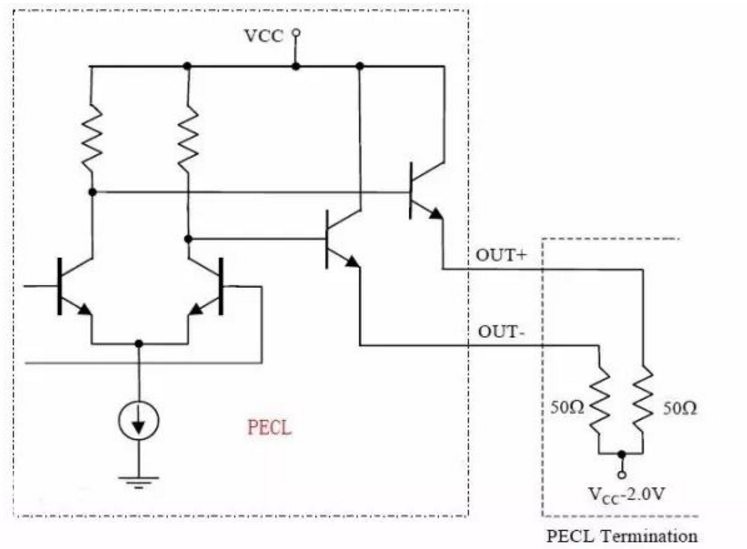

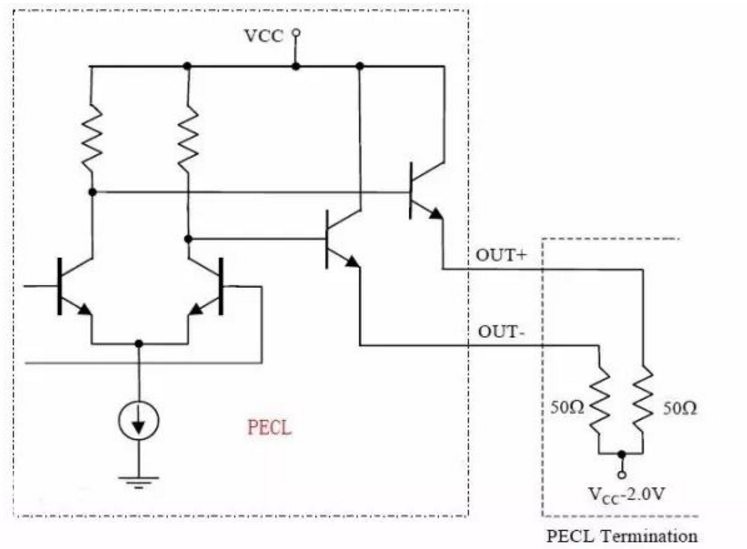

在高速電路中如何實現高速驅動輸出呢?要么增大驅動電流,要么降低電平標準,或者提高晶體管工作速度。顯然前者會帶來非常大的功耗,因此改變電平標準和改進晶體管設計成為選擇,雖然低

![的頭像]() 發表于

發表于 12-17 07:38

?1.3w次閱讀

你好,請問DAC的DACCLK用LVPECL電平標準的接口,為什么DATACLK用的是LVDS電平標準的

發表于 01-21 07:56

幾種串行通信接口標準詳解在數據通信、計算機網絡以及分布式工業控制系統中,經常采用串行通信來交換數據和信息。1969年,美國電子工業協會(EIA)公布了RS-232C作為串行通信接口的電

發表于 09-21 09:54

/ 數字)轉換器,將模擬信號轉變為數字信號。在經過D/A 和A/D 兩次轉換后,不可避免地造成了一些圖像細節的損失。 在DVI 之前也存在一些數字接口標準,但都未能成為工業

發表于 08-11 09:47

數字視頻界面DisplayPort 兼容測試詳解:DisplayPort是VESA栛會(Video Electronics Standards Association)所制定一個新的數字影音接

發表于 02-27 08:27

?36次下載

數字波形詳解

數字波形是邏輯電平對時間的圖形表示。通常,我們將只有兩個離散值的波形稱之為脈沖波形,在這一點上脈沖波形與數字

發表于 04-06 23:38

?1.9w次閱讀

SDI數字分量串行接口詳解。

發表于 05-18 14:26

?19次下載

幾種串行通信接口標準詳解

發表于 01-03 11:34

?0次下載

數字測量系統的標準接口

發表于 10-25 15:37

?8次下載

隨著電信數據傳輸業務、視頻監控與工業控制需求的增加,光模塊的應用也越來越多,光通信系統工程師往往苦惱于如何正確處理不同接口電平 IC 與高速光模塊之間的連接,本篇文章正是為解決這一問題

發表于 11-06 16:50

?100次下載

在通信系統中,各種協議和接口經常讓剛接觸不久的同學迷糊半天。不同領域涉及的通訊類型和應用設計又有定的差異,因此有必要盡可能詳細的做一下相關知識點的梳理和總結。關于電平標準的由來:在以高

發表于 01-08 16:14

?11次下載

本案例主要描述AGV小車和控制系統之間的通信過程,通過VDA 5050標準接口、MQTT通信協議和虹科HiveMQ實現AGV小車和控制系統之間

![的頭像]() 發表于

發表于 05-13 11:11

?8071次閱讀

在數字電子領域,TTL電平標準是一種非常重要的邏輯電平標準,它定義了數字信號的高低

![的頭像]() 發表于

發表于 01-16 09:46

?152次閱讀

電平是一種雙極型晶體管邏輯電平,它由兩個晶體管構成,一個是輸入晶體管,另一個是輸出晶體管。TTL電平的標準電壓定義如下: 低電平(邏輯0):

![的頭像]() 發表于

發表于 01-16 09:56

?199次閱讀

在電子通信領域,電信號的傳輸和處理是至關重要的。TTL電平(Transistor-Transistor Logic)和RS-232接口是兩種常見的電信號標準,它們在不同的應用場景中發

![的頭像]() 發表于

發表于 01-16 10:13

?96次閱讀

數字系統之間的接口電平標準詳解!

數字系統之間的接口電平標準詳解!

評論