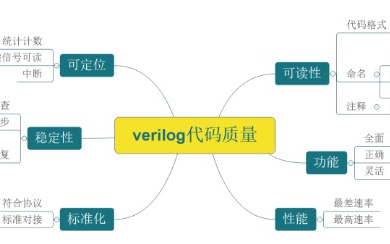

1.Verilog HDL描述可綜合電路Verilog HDL語言是對已知硬件電路的文本描述。所以編寫前:

對所需實現的硬件電路“胸有成竹”;牢記可綜合Verilog HDL與電路結構一一對應的關系;確認電路指標是什么:性能?面積?硬件思維方式,代碼不再是一行行的代碼而是一塊一塊的硬件模塊;

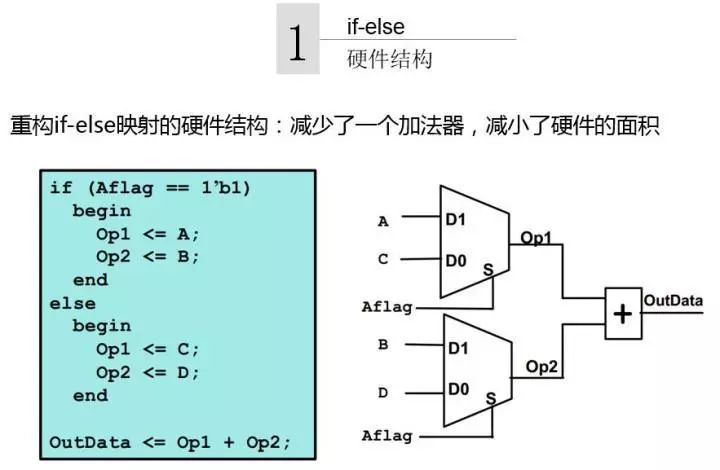

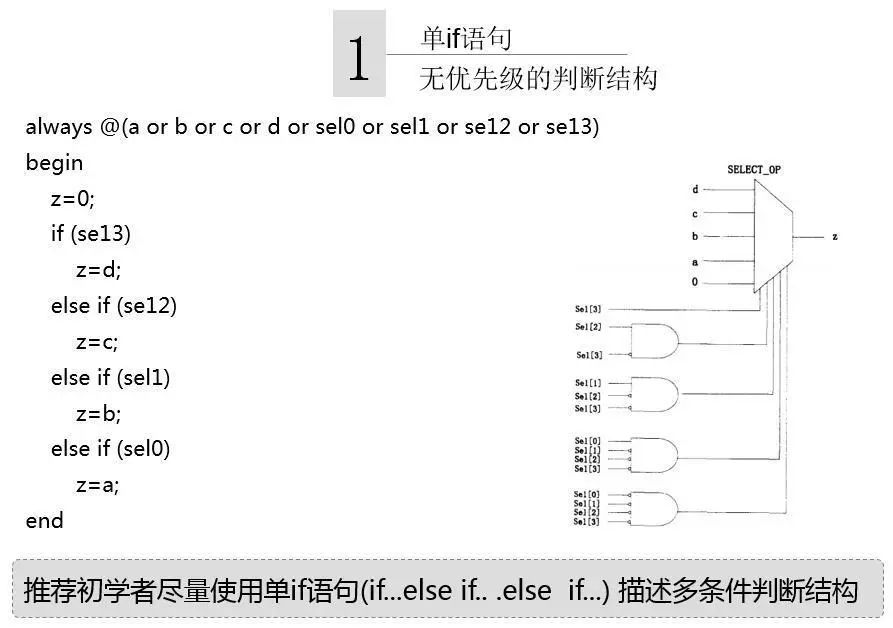

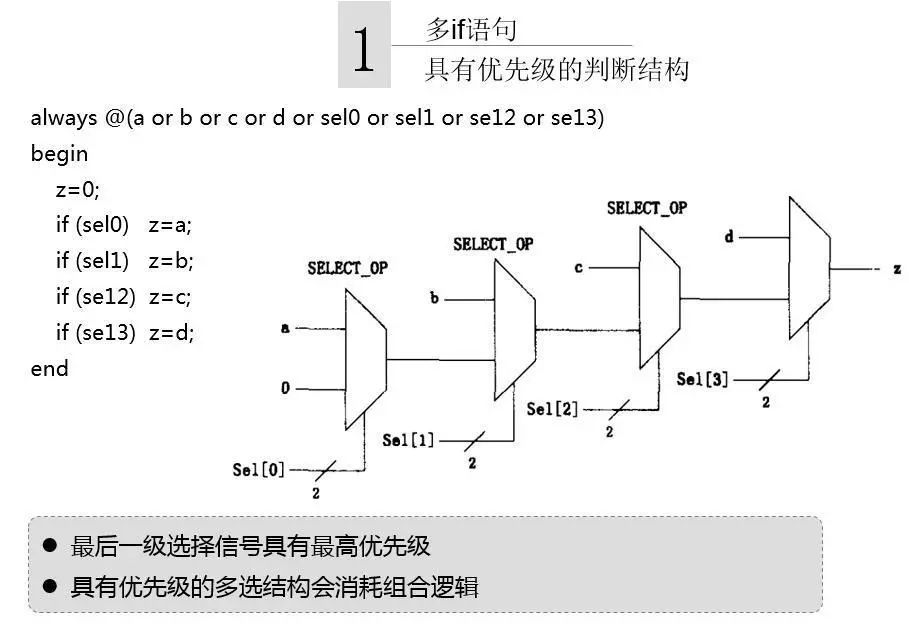

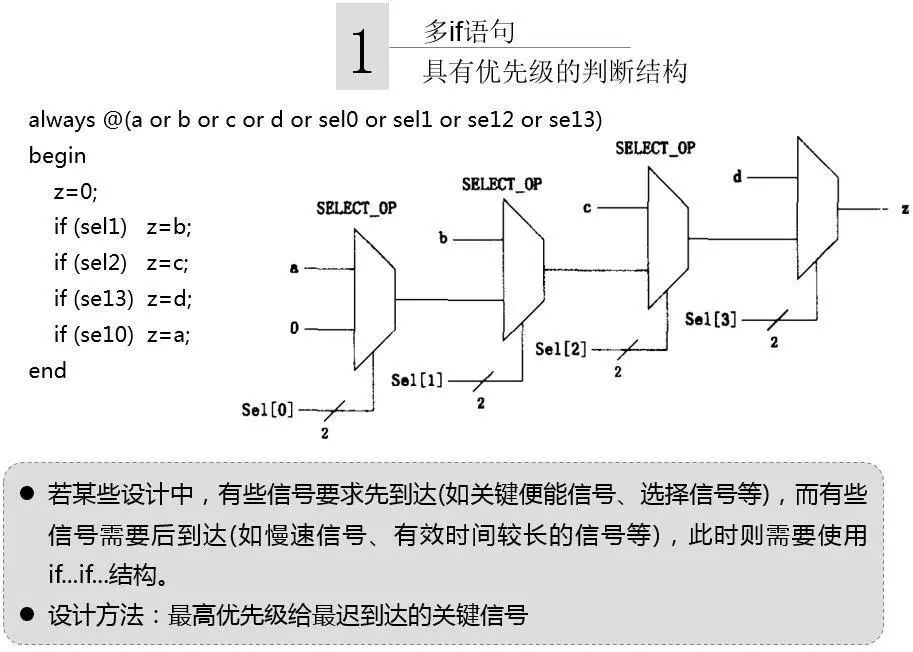

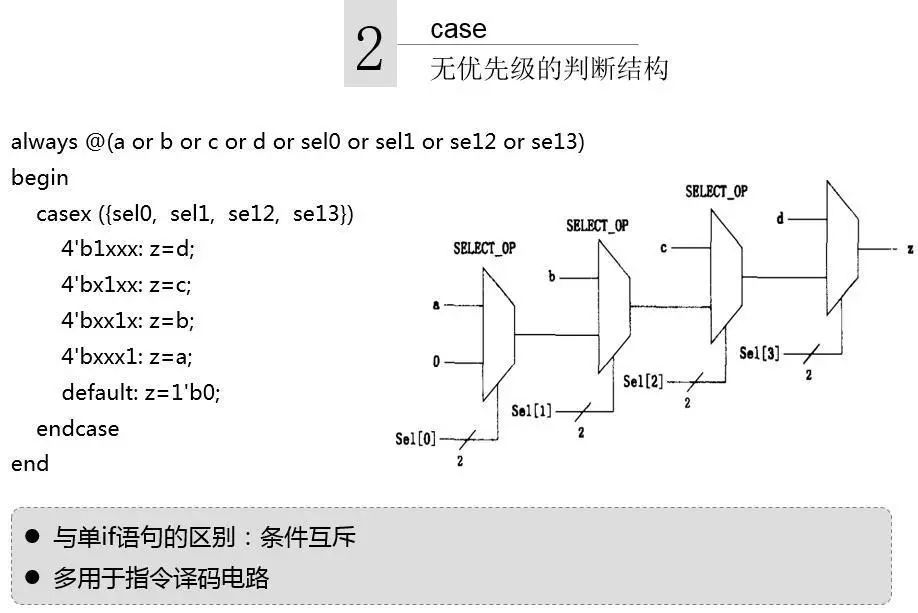

達到以上幾點,就可以寫出行云流水般的高質量代碼。關于代碼與硬件電路的對應關系,參見如下圖片,引用自Synopsys官方文檔和幾本參考書:

2、自動化生成代碼如果一定要有奇淫技巧的話,那么代碼自動化生成技術就一定可以配得上這個稱號。

近十年來,數字集成電路規模和復雜度飛速提高。這給數字集成電路工程師帶來了不僅是腦力上的勞動的增加,更多是體力重復性工作的增多。傳統的手工代碼的編寫存在很多弊端。

首先對于模塊的代碼工程師,要面對許多設計文件。而這些文件之間可能相互不一致,給代碼的編寫帶來了很多的困擾。

其次,代碼工程師需要將這些文件中的很多設計信息體現在代碼中,其中一些信息是重復性的謄寫。這不僅帶來了很多枯燥復雜的工作量而且人工參與過多也容易引入很多粗心帶來的錯誤。

再次,由于各個模塊連接信號之多導致信號文件的手寫工作量很大。每個信號文件小則幾千行大則上萬行信息。而且一旦有信號連接的變動需要相應修改多個模塊的信號文件。

最后,如果設計文件改動相應的設計文件很容易出現哪幾處忘記改動的問題。

而Perl腳本語言又有著強大的處理文本的能力。將腳本語言應用于數字電路設計中,作為設計文檔和EDA工具的黏合劑,能夠大大增加設計的速度。

具體方法為:使用腳本語言從設計文檔中提取有用的信息來生成想要的Verilog HDL代碼,從而大大減少了IC設計者的工作量,并提高了代碼的質量。其好處有:

(1)很好的設計一致性:保證了設計概念一旦變動即設計文檔稍加修改,對應的Verilog HDL代碼就會相應的改變,不需要工程師手動改變代碼。

(2)兼容性強:該自動生成代碼工具中設置了一個配置文件,供設計工程師的配置修改。對于不同的項目,通過修改配置該文件可以直接是代碼相應變化,有一定的靈活性。此外,該自動生成代碼工具已經應用于兩個以上項目中,實踐證明有很好的兼容性。

(3)代碼維護方便:對于設計代碼的更新或升級,只需要重新運行下該工具即可,不需要一點點該寫代碼。

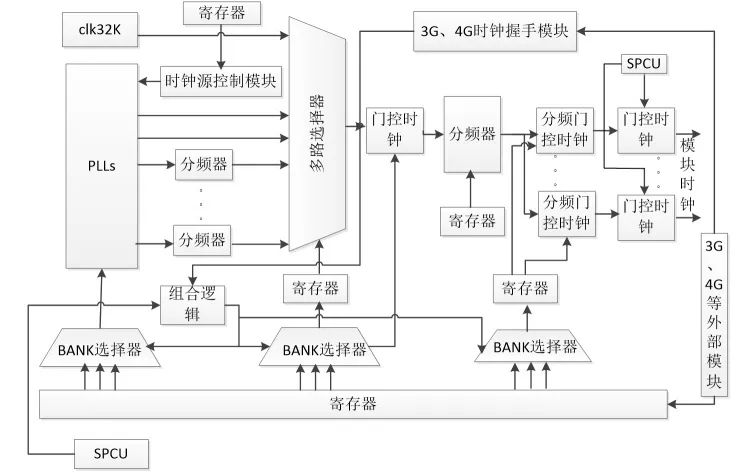

(4)使用簡單:將很多腳本集成在一起,使用工具時只需要運行一條命令即可。本文將舉一個Perl語言在代碼自動生成中的應用實例,下圖為一SoC芯片中全芯片的時鐘控制電路框圖:

時鐘控制模塊實現配置PLL參數、選擇輸出時鐘源、時鐘分頻、時鐘門控、bank切換、輸出時鐘等功能。3G、4G是系統通訊單元,向時鐘控制單元申請時鐘。PLLs是時鐘源,是時鐘控制單元的輸入。

時鐘控制單元有七大主要模塊,分別為時鐘源控制模塊、bank切換模塊、分頻模塊、時鐘門控模塊、多路選擇器模塊、寄存器、3G4G時鐘握手模塊。時鐘源控制模塊控制時鐘源的大小、開關。bank切換模塊使時鐘控制單元能正常工作在不同的電壓下。

時鐘控制單元的的工作機理如下:首先,外部模塊向時鐘控制單元請求時鐘,并修改并寫寄存器狀態;時鐘源控制單元根據寄存器中的內容配置時鐘源Plls,并提供了所有的時鐘源。然后,分頻器完成這些時鐘源預分頻的操作,并將其作為多路選擇器的時鐘源。而多路選擇器則從輸入的時鐘源中選擇輸出主時鐘。

主時鐘通過分頻模塊產生所有的分頻使能信號,這個過程中,需根據寄存器所配置的分頻數來輸出不同的頻率的時鐘。同時,根據系統的實時需求,通過由SPCU控制的bank選擇器完成門控時鐘的實現,降低系統的功耗。

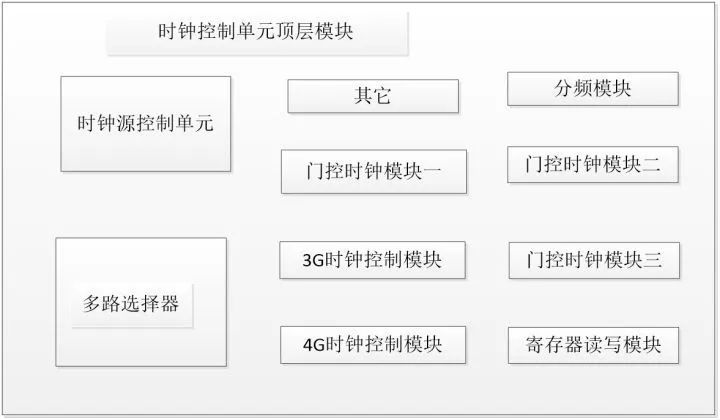

以上是時鐘控制模塊的功能分析,那么如何通過代碼自動生成技術來實現呢?(1)首先,我們把這些模塊梳理下,形成一個自頂向下的層次結構,如下圖。如圖中所示,頂層模塊完成對底層模塊的連接,底層模塊實現時鐘控制單元的功能。

針對代碼自動生成問題,對于頂層模塊來說,承擔的功能是自動地將底層數十個模塊連接起來。對于底層模塊來說,需要根據不同的功能定制需求,來自動化地生成所有功能性的代碼,然后被頂層調用和連接。這樣的話,就存在兩個問題:[1]自動生成頂層模塊?[2]自動生成底層模塊?

(2)頂層模塊:通常來說,對于一個復雜的SoC芯片,會有萬數量級的信號需要進行匹配和連接。而能夠自動生成的信號文件中的信號連接有兩個特點:一是信號命令規律性強二是信號的連接關系可以從設計文件中體現。滿足了這兩點,便可以實現信號文件的自動化。

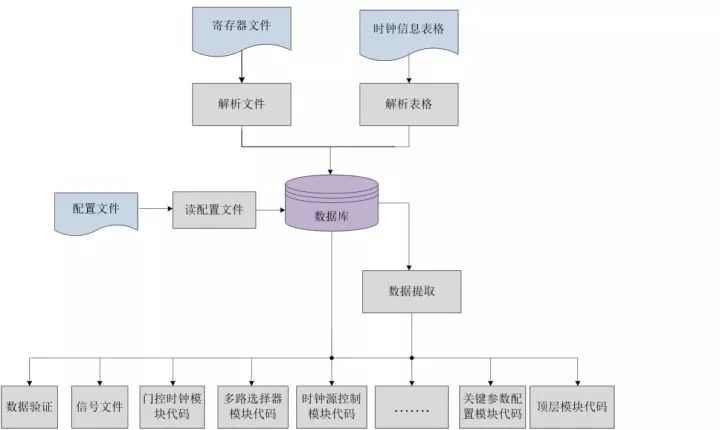

(3)底層模塊此處即可體現Perl腳本強大的數據處理功能,針對該問題,將腳本劃分為三類:提取腳本、生成腳本和集成腳本三種。提取腳本用來從輸入文件中提取有用的設計信息到存儲單元中;生成腳本從存儲單元獲得有用信息來生成各個功能模塊的代碼;集成腳本將所有的腳本集成在一個腳本里,方便統一化使用。以下是代碼生成的腳本流程圖:

如圖所示,輸入的文件都是excel和文本形式,Perl腳本首先讀取技術文檔,從中解析出時鐘模塊所需的連接、頻率、時鐘域等信息,基于此信息建立一個數據庫。然后,根據實際芯片的具體需求,即配置文件,生成相應的自動化控制模式和需求。

最終,依據配置文件和數據庫,完成所有所需verilog代碼的生成。需要注意的是,并不是所有的代碼都可以自動生成,有些結構特殊的電路,只能通過手工編寫來完成。所以,自動編寫通常完成較為規整的、有規律性的代碼,手工書寫作為補充。這樣即可保證得到高質量的代碼。

-

Verilog

+關注

關注

28文章

1351瀏覽量

110288 -

代碼

+關注

關注

30文章

4823瀏覽量

68922 -

Verilog HDL

+關注

關注

17文章

126瀏覽量

50462

原文標題:行云流水般的代碼難寫嗎?那是你還缺一種硬件思維

文章出處:【微信號:EngicoolArabic,微信公眾號:電子工程技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高質量c語言高級教程

如何寫出漂亮的嵌入式C代碼

10個嵌入式小技巧 教你寫出高質量代碼!

如何寫好一篇高質量的引用論文

如何編寫高質量的Javascript代碼

如何寫出行云流水般的高質量代碼

如何寫出行云流水般的高質量代碼

評論