很容易驗證間隙,高速,制造的約束,并通過計算最大的焊盤和可測試性極限。建立、保存和使用驗證方案。只有兩次鼠標點擊,違規行為才能以直觀的形式發生。自動從電子表格中選擇一個沖突,以放大和更正該沖突,并快速重新驗證已修復該沖突。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

計算

+關注

關注

2文章

450瀏覽量

38835 -

PADS

+關注

關注

80文章

808瀏覽量

107839 -

焊盤

+關注

關注

6文章

556瀏覽量

38179

發布評論請先 登錄

相關推薦

PADS邏輯教程

PADSlogic9.6電路圖設計資料手冊(中文教程)為motor Graphics公司軟件提供的原本中文手冊,用于PADSlogic軟件電路圖設計參考使用。PADS Logic用戶界面旨在提高

發表于 12-16 14:33

?0次下載

時序約束一主時鐘與生成時鐘

的輸出,對于Ultrascale和Ultrascale+系列的器件,定時器會自動地接入到GT的輸出。 1.2 約束設置格式 主時鐘約束使用命令create_clock進行創建,進入Timing

常用時序約束使用說明-v1

為了防止約束失敗,我們在Tcl輸入框中驗證,沒有告警或者錯誤說明約束的寫法是正確的set_max_delay 5.00 -from [get_cells key2_detect_inst/state

急!!!!求助大佬。PADS LAYOUT軟件BUG問題

Window11系統,PADS VX2.3版本,

之前PADS軟件是正常的,突然用不了鼠標的放大縮小功能,鍵盤快捷鍵也沒用,并且pads里的功能鍵都進不去,比如點擊pads頁面顯示顏色

發表于 09-23 14:16

兩種SR鎖存器的約束條件

基本約束條件: SR鎖存器是一種基本的數字邏輯電路,用于存儲一位二進制信息。它有兩個輸入端:S(Set)和R(Reset),以及兩個輸出端:Q和Q'(Q的反相)。以下是SR鎖存器的基本約束

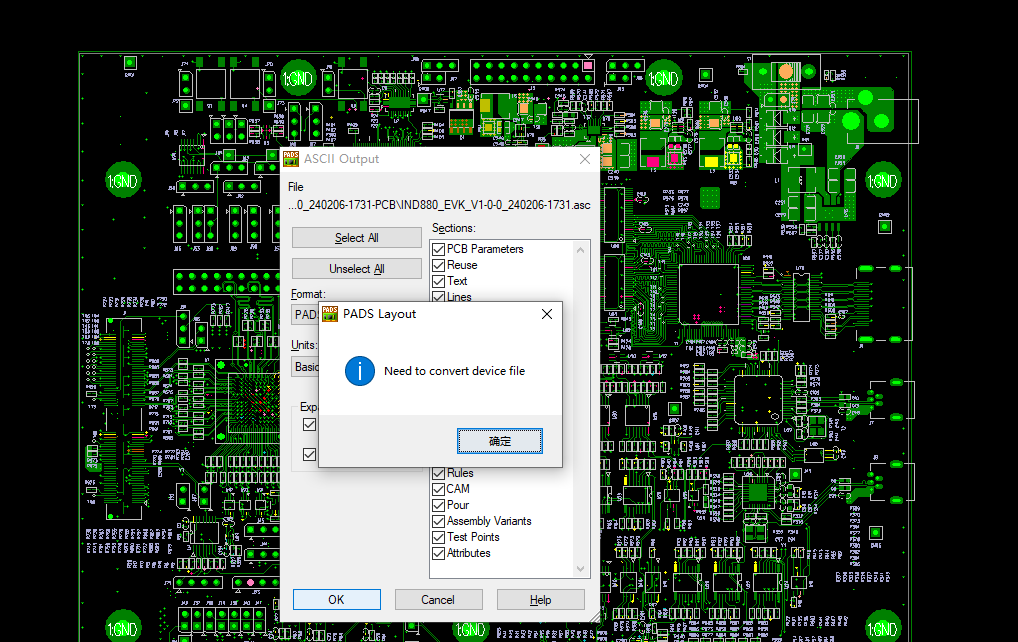

pads閃退故障解決方案 PADS報Need to convert device file然后Open error:devices.dat確定閃退

PADS 報Need to convert device file, 然后Open error:devices.dat 確定閃退

Xilinx FPGA編程技巧之常用時序約束詳解

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法

為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

發表于 05-06 15:51

時序約束實操

添加約束的目的是為了告訴FPGA你的設計指標及運行情況。在上面的生成約束之后,在Result àxx.sdc中提供約束參考(請注意該文件不能直接添加到工程中,需要熱復制到別的指定目錄或者新建自己的SDC文件添加到工程)。

Xilinx FPGA的約束設置基礎

LOC約束是FPGA設計中最基本的布局約束和綜合約束,能夠定義基本設計單元在FPGA芯片中的位置,可實現絕對定位、范圍定位以及區域定位。

發表于 04-26 17:05

?1252次閱讀

Xilinx FPGA編程技巧之常用時序約束詳解

今天給大俠帶來Xilinx FPGA編程技巧之常用時序約束詳解,話不多說,上貨。

基本的約束方法為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑以及異常路徑為

發表于 04-12 17:39

PADS的視覺約束驗證

PADS的視覺約束驗證

評論