當(dāng)前,高頻、高速PCB設(shè)計(jì)已經(jīng)成為了主流,每個(gè)PCB Layout工程師都應(yīng)該熟練掌握。接下來(lái),板兒妹和大家分享硬件大牛們?cè)诟哳l高速PCB電路中的一些設(shè)計(jì)經(jīng)驗(yàn),希望對(duì)大家有所幫助。

1、如何避免高頻干擾?

避免高頻干擾的基本思路是盡量降低高頻信號(hào)電磁場(chǎng)的干擾,也就是所謂的串?dāng)_(Crosstalk)。可用拉大高速信號(hào)和模擬信號(hào)之間的距離,或加ground guard/shunt traces 在模擬信號(hào)旁邊。還要注意數(shù)字地對(duì)模擬地的噪聲干擾。

2、在高速PCB設(shè)計(jì)原理圖設(shè)計(jì)時(shí),如何考慮阻抗匹配問(wèn)題?

在設(shè)計(jì)高速PCB 電路時(shí),阻抗匹配是設(shè)計(jì)的要素之一。而阻抗值跟走線(xiàn)方式有絕對(duì)的關(guān)系,例如是走在表面層(microstrip)或內(nèi)層(stripline/double stripline),與參考層(電源層或地層)的距離,走線(xiàn)寬度,PCB材質(zhì)等均會(huì)影響走線(xiàn)的特性阻抗值。也就是說(shuō)要在布線(xiàn)后才能確定阻抗值。一般仿真軟件會(huì)因線(xiàn)路模型或所使用的數(shù)學(xué)算法的限制而無(wú)法考慮到一些阻抗不連續(xù)的布線(xiàn)情況,這時(shí)候在原理圖上只能預(yù)留一些terminators(端接),如串聯(lián)電阻等,來(lái)緩和走線(xiàn)阻抗不連續(xù)的效應(yīng)。真正根本解決問(wèn)題的方法還是布線(xiàn)時(shí)盡量注意避免阻抗不連續(xù)的發(fā)生。

3、在高速PCB設(shè)計(jì)時(shí),設(shè)計(jì)者應(yīng)該從那些方面去考慮EMC、EMI 的規(guī)則呢?

一般EMI/EMC 設(shè)計(jì)時(shí)需要同時(shí)考慮輻射(radiated)與傳導(dǎo)(conducted)兩個(gè)方面。前者歸屬于頻率較高的部分(》30MHz)后者則是較低頻的部分(《30MHz)。所以不能只注意高頻而忽略低頻的部分。一個(gè)好的EMI/EMC 設(shè)計(jì)必須一開(kāi)始布局時(shí)就要考慮到器件的位置,PCB 疊層的安排,重要聯(lián)機(jī)的走法,器件的選擇等,如果這些沒(méi)有事前有較佳的安排,事后解決則會(huì)事倍功半,增加成本。 例如時(shí)鐘產(chǎn)生器的位置盡量不要靠近對(duì)外的連接器,高速信號(hào)盡量走內(nèi)層并注意特性阻抗匹配與參考層的連續(xù)以減少反射,器件所推的信號(hào)之斜率(slew rate)盡量小以減低高頻成分,選擇去耦合(decoupling/bypass)電容時(shí)注意其頻率響應(yīng)是否符合需求以降低電源層噪聲。另外,注意高頻信號(hào)電流之回流路徑使其回路面積盡量小(也就是回路阻抗loop impedance 盡量小)以減少輻射。還可以用分割地層的方式以控制高頻噪聲的范圍。最后,適當(dāng)?shù)倪x擇PCB 與外殼的接地點(diǎn)(chassis ground)。

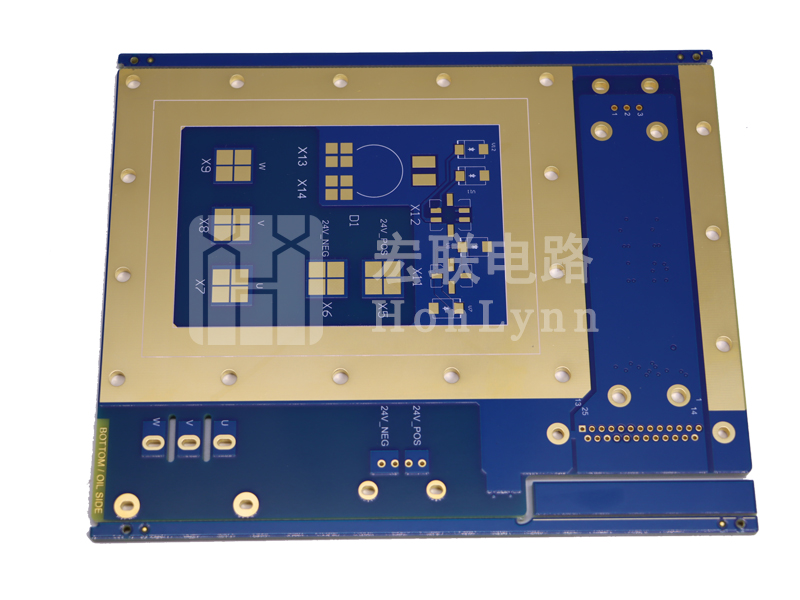

4、如何選擇PCB板材?

選擇PCB 板材必須在滿(mǎn)足設(shè)計(jì)需求和可量產(chǎn)性及成本中間取得平衡點(diǎn)。設(shè)計(jì)需求包含電氣和機(jī)構(gòu)這兩部分。通常在設(shè)計(jì)非常高速的PCB 板子(大于GHz 的頻率)時(shí)這材質(zhì)問(wèn)題會(huì)比較重要。例如,現(xiàn)在常用的FR-4 材質(zhì),在幾個(gè)GHz 的頻率時(shí)的介質(zhì)損耗(dielectric loss)會(huì)對(duì)信號(hào)衰減有很大的影響,可能就不合用。就電氣而言,要注意介電常數(shù)(dielectric constant)和介質(zhì)損在所設(shè)計(jì)的頻率是否合用。

5、如何盡可能的達(dá)到EMC 要求,又不致造成太大的成本壓力?

PCB 板上會(huì)因EMC 而增加的成本通常是因增加地層數(shù)目以增強(qiáng)屏蔽效應(yīng)及增加了ferrite bead、choke等抑制高頻諧波器件的緣故。除此之外,通常還是需搭配其它機(jī)構(gòu)上的屏蔽結(jié)構(gòu)才能使整個(gè)系統(tǒng)通過(guò)EMC的要求。以下僅就PCB 板的設(shè)計(jì)技巧提供幾個(gè)降低電路產(chǎn)生的電磁輻射效應(yīng)。

盡可能選用信號(hào)斜率(slew rate)較慢的器件,以降低信號(hào)所產(chǎn)生的高頻成分。

注意高頻器件擺放的位置,不要太靠近對(duì)外的連接器。

注意高速信號(hào)的阻抗匹配,走線(xiàn)層及其回流電流路徑(return current path),以減少高頻的反射與輻射。

在各器件的電源管腳放置足夠與適當(dāng)?shù)娜ヱ詈想娙菀跃徍碗娫磳雍偷貙由系脑肼暋L貏e注意電容的頻率響應(yīng)與溫度的特性是否符合設(shè)計(jì)所需。

對(duì)外的連接器附近的地可與地層做適當(dāng)分割,并將連接器的地就近接到chassis ground。

可適當(dāng)運(yùn)用ground guard/shunt traces 在一些特別高速的信號(hào)旁。但要注意guard/shunt traces 對(duì)走線(xiàn)特性阻抗的影響。

電源層比地層內(nèi)縮20H,H 為電源層與地層之間的距離。

6、2G 以上高頻PCB 設(shè)計(jì),走線(xiàn),排版,應(yīng)重點(diǎn)注意哪些方面?

2G 以上高頻PCB 屬于射頻電路設(shè)計(jì),不在高速數(shù)字電路設(shè)計(jì)討論范圍內(nèi)。而 射頻電路的布局(layout)和布線(xiàn)(routing)應(yīng)該和原理圖一起考慮的,因?yàn)椴季植季€(xiàn)都會(huì)造成分布效應(yīng)。而且,射頻電路設(shè)計(jì)一些無(wú)源器件是通過(guò)參數(shù)化定義,特殊形狀銅箔實(shí)現(xiàn),因此要求EDA 工具能夠提供參數(shù)化器件,能夠編輯特殊形狀銅箔。Mentor 公司的boardstation 中有專(zhuān)門(mén)的RF 設(shè)計(jì)模塊,能夠滿(mǎn)足這些要求。而且,一般射頻設(shè)計(jì)要求有專(zhuān)門(mén)射頻電路分析工具,業(yè)界最著名的是agilent 的 eesoft,和Mentor 的工具有很好的接口。

7、添加測(cè)試點(diǎn)會(huì)不會(huì)影響高速信號(hào)的質(zhì)量?

會(huì)不會(huì)影響信號(hào)質(zhì)量要看加測(cè)試點(diǎn)的方式和信號(hào)到底多快而定。基本上外加的測(cè)試點(diǎn)(不用在線(xiàn)既有的穿孔(via or DIP pin)當(dāng)測(cè)試點(diǎn))可能加在在線(xiàn)或是從在線(xiàn)拉一小段線(xiàn)出來(lái)。前者相當(dāng)于是加上一個(gè)很小的電容在在線(xiàn),后者則是多了一段分支。這兩個(gè)情況都會(huì)對(duì)高速信號(hào)多多少少會(huì)有點(diǎn)影響,影響的程度就跟信號(hào)的頻率速度和信號(hào)緣變化率(edge rate)有關(guān)。影響大小可透過(guò)仿真得知。原則上測(cè)試點(diǎn)越小越好(當(dāng)然還要滿(mǎn)足測(cè)試機(jī)具的要求)分支越短越好。

責(zé)任編輯:ct

-

pcb

+關(guān)注

關(guān)注

4324文章

23159瀏覽量

399314 -

華強(qiáng)pcb線(xiàn)路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43137

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

深度解析:PCB高速信號(hào)傳輸中的阻抗匹配與信號(hào)完整性

高速PCB設(shè)計(jì)EMI防控手冊(cè):九大關(guān)鍵步驟詳解

高速PCB設(shè)計(jì)指南

專(zhuān)業(yè)PCB設(shè)計(jì),高速PCB設(shè)計(jì),PCB設(shè)計(jì)外包, PCB Layout,PCB Design,PCB畫(huà)板公司,PCB設(shè)計(jì)公司,迅安通科技公司介紹

PCB線(xiàn)路板高頻板與高速板的區(qū)別

PCB設(shè)計(jì)與PCB制板的緊密關(guān)系

初學(xué)者必看:破解PCB設(shè)計(jì)常見(jiàn)錯(cuò)誤!

PCB設(shè)計(jì)的EMC有哪些注意事項(xiàng)

高速pcb與普通pcb的區(qū)別是什么

高速pcb的定義是什么

如何應(yīng)對(duì)PCB設(shè)計(jì)中信號(hào)線(xiàn)的跨分割呢?

PCB設(shè)計(jì)中的常見(jiàn)問(wèn)題有哪些?

高頻高速PCB設(shè)計(jì)可能遇到怎樣的問(wèn)題

高頻高速PCB設(shè)計(jì)可能遇到怎樣的問(wèn)題

評(píng)論