EDA行業的歷史不斷受到技術周期性動蕩以及權力平衡的影響。隨著電子設計自動化(EDA)解決方案的創建,半導體工藝技術的進步和不斷增加的上市時間需求成為必然。諸如綜合等關鍵技術正在成為商品,傳統的邏輯和物理設計流程所依賴的基礎不再適用。當前的多供應商,多工具設計流程無法充分解決時序收斂問題,也無法解決數百萬門設計問題。設計人員真正需要的是單一的集成系統,它可以將設計直接從RTL流向GDSII,并保證性能良好。

這一突破性解決方案將從何而來?從最新起點,。以綜合為例。 Synopsys Design Compiler在12年前取得了突破,但直到Ambit的BuildGates來到它之前,它幾乎停滯不前。 BuildGates為邏輯綜合帶來了三項重大改進:更大容量(高達100K門),在時序相關優化期間獲得更好的結果,以及為大型設計提供分布式綜合的時間預算。 Synopsys通過對DC進行略微改進,回應了其首個再合成競爭對手Ambit。但是,用戶仍然堅持使用已有12年歷史的DC技術。

地方和路線并沒有停滯不前,因為每走一步都需要兩步。這主要是由于Cadence習慣于獲得體面的技術,然后將其用于老化的設計流程而不是整合它。這為他們創造了一個有利可圖的設計服務業務,因為它需要專家們弄清楚如何將所有點工具有效地組合在一起。但是,Cadence最后一次開發出更好的,新的布局布線工具是什么時候?

由于他們需要保持Wallstreet的快樂,Cadence和Synopsys聲稱他們擁有或接近擁有RTL GDSIIflow可減少迭代次數并解決信號完整性和時序收斂問題。毫不奇怪,消除迭代,大型設計的容量和保證時序收斂不是他們的功能列表。我贊揚他們的誠實,因為他們無法提供這些信息。

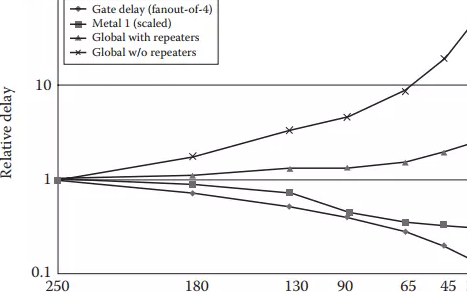

半導體工藝技術的特征尺寸的不斷減少為這些傳統的合成,布局和布線系統帶來了難以克服的問題。大多數這些工具是在10 - 15年前開發的,當時10K門設計是最后的,面積是最嚴峻的挑戰,互連延遲是不可忽視的。那時候合成與布局和布線之間的差距不是問題。

在今天的DSM設計中,互連布線代表了電路中延遲的絕大部分。與門延遲不同,互連延遲在邏輯設計期間難以預測,因為它取決于硅的最終物理布局。因此,對于傳統的EDA解決方案,硅設計團隊必須在邏輯和物理設計之間進行多次迭代,以滿足時序要求,通常會延遲產品發布數月。

雖然Synopsys和Cadence已經發布了關于物理編譯器和PKS的重大聲明 - 他們目前對RTL toGDSII流問題的回答 - 他們實際上只是在“綜合”產品中重新包裝存在的合成,放置和全局路由引擎。如果這些公司了解如何解決設計師的問題和需求,他們就會知道設計師需要處理1M到10M門設計的工具,而僅僅是減少工作是不夠的。

為了滿足這些解決方案的時間安排,當通過優化使布局估計無效并且必須以與技術無關的方式顯著重構設計的某些部分時,仍需要迭代。此外,新解決方案還需要在詳細布局和布線之間進行迭代,因為它們不提供詳細的布局規劃。如果沒有詳細的布局規劃,這些方法必須使用guesstimates formacro和pad placement。由兩個宏組成的關鍵路徑的時序僅由幾個邏輯級別組成,高度依賴于精確的宏位置。

由于這些方法無法保證芯片性能,因此設計人員對這些工具進行基準測試需要通過整個芯片設計流向GDSII。只有使用無DRC的GDSII,才能知道他的芯片是否符合時序要求。

這些新的解決方案也受到100K門綜合容量限制的阻礙。布局和布線算法通過扁平設計產生最佳結果。為了利用這些膠溶液,物理塊現在被限制在合成的極限,并且需要基于極限的限制來定義層次邊界。時序收斂的嚴重問題發生在1M +門設計中,并且是長線,宏和焊盤放置的直接結果。

為GDSII解決方案提供完整的集成RTL,可以減少迭代次數,保證時序,并且處理大型設計平板,邏輯和物理設計技術的能力必須完全重新設計。綜合必須不再依賴于隨機線載模型或初始布局的估計來管理互連延遲。合成必須與使用時序作為主要約束的完整物理設計解決方案緊密集成。為了實現必要的集成級別,此解決方案必須在單個統一的數據架構上運行,以允許工具同時工作。由于Cadence和Synopsys顯然無法提供這樣的解決方案,它將從何而來?無一例外,創業公司推動了技術的進步,改變了行業的力量平衡。如果EDA歷史記錄是任何指標,那么只有創業公司可以通過這種革命性的解決方案。

-

RTL

+關注

關注

1文章

385瀏覽量

59917 -

GDSII

+關注

關注

0文章

6瀏覽量

8867 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21795 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27884 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43138

發布評論請先 登錄

相關推薦

[求助]GDSII和ASCII格式互換!!!

GDSII是什么?什么是GDSII文件

信號流向問題

pcb如何規劃信號流向圖

三星使用Cadence統一數字流程實現20nm芯片流片

Cadence提供新一代Encounter RTL-to-GDSII流程

RTL8139C RTL8139C-LF RTL8139CL RTL8139CL-LF

我們處于EDA融合時代 更多的算法工具涌現

從RTL追蹤到Scala

Vivado中對RTL源文件如何進行加密

直接在網表中插入RTL來快速做芯片功能ECO

設計直接從RTL流向GDSII

設計直接從RTL流向GDSII

評論