S/R鎖存器

鎖存器(有時也稱為S/R鎖存器)是最小的存儲器塊。它們可以使用兩個NOR邏輯門(S和R為高電平有效)或兩個NAND門(輸入為低電平有效)構建,并用于構建更復雜的鎖存器和觸發器。

使用兩個NOR邏輯門進行S/R鎖存。

兩個輸入S和R可用于設置和復位鎖存器。設置鎖存器相當于存儲二進制鎖存器。輸出Q將變為高電平,反相輸出Q將被拉低。重置具有相反的效果。當兩個輸入均為低電平時,保持當前狀態。

此電路的簡單性是有代價的:可能會發生一些會導致不確定行為的事情(電路的下一個狀態將是未定義的) )或所謂的臨界競爭,其中鎖存器將永遠保持設置和復位。

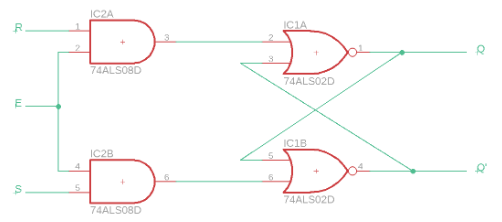

添加兩個AND門將把簡單鎖存器轉換為帶有額外使能輸入的門控鎖存器。此方法可用于控制何時鎖存數據。沒有它,只要鎖存器被置位或復位,數據就會(理論上)出現在輸出端。

將兩個AND門添加到一個簡單的鎖存器以形成一個門控鎖存器。

D-Latch

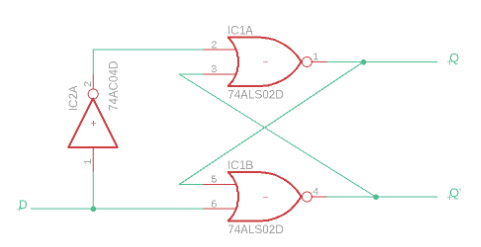

這種類型的鎖存器使用R/S鎖存器和為電路增加一個逆變器。這樣做可以防止上面描述的關鍵競爭,使閂鎖更容易使用。

使用兩個NOR門和一個NOT門的D鎖存電路。

如您所見,此鎖存器只有一個輸入。存在于D的數據將被鎖存和存儲。請注意,上圖代表了鎖存器的核心。這種設計在實際應用中是無用的,因為輸入一改變就會改變輸出。

實際上,鎖存器具有啟用它們的輸入,并且數據僅在啟用時被鎖存。為簡單起見,我省略了啟用輸入。

D觸發器和S/R觸發器

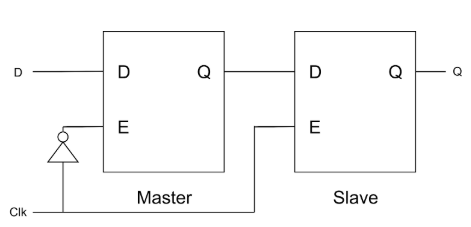

啟用鎖存器時,它們是透明的。這意味著輸出將具有與輸入相同的狀態。但是,有些情況下,僅在信號的上升沿或下降沿使輸出發生變化更為有用。例如,使用周期性時鐘信號。

Flips-flops通過串聯使用兩個鎖存器實現輸出變化。第一階段通常稱為主(鎖存器),第二階段是從屬:

這是一個正邏輯,正邊沿觸發D觸發器。

可以通過用S/R鎖存器替換D鎖存器來構造S/R觸發器。然而,當兩個輸入都被置位時,這樣的觸發器,就像上面的鎖存器一樣,可能進入未定義狀態。解決這個問題的一種方法是使用JK觸發器。

JK觸發器

JK觸發器與S/R觸發器非常相似。它有一個J輸入,其作用類似于S輸入和K輸入,用于復位電路。然而,當兩者同時被置位(正邏輯高電平,負電平低電平)時,觸發器不會進入未定義狀態,而是切換其狀態。

復查鎖存器和觸發器

鎖存器是存儲器的最小構建塊。它們用于其他電路,如觸發器和移位寄存器,只要它們被啟用,它們就會將輸入應用于它們的輸出。觸發器是邊沿觸發的,只有在啟用和觸發時才會改變它們的狀態。有幾種基本類型的鎖存器和觸發器,每種都適用于某些應用。

-

鎖存器

+關注

關注

8文章

908瀏覽量

41595 -

觸發器

+關注

關注

14文章

2003瀏覽量

61286

發布評論請先 登錄

相關推薦

如何操作基本類型的鎖存器和觸發器

如何操作基本類型的鎖存器和觸發器

評論