多bit數(shù)據(jù)流跨時(shí)鐘域傳輸

數(shù)據(jù)流和指示信號(hào)不同:

- 數(shù)據(jù)流大多具有連續(xù)性,即背靠背傳輸;

- 數(shù)據(jù)流要求信號(hào)具有較快的傳輸速度

解決方法:

- SRAM : 簡(jiǎn)單,不詳述

- 異步FIFO

FIFO(first in first out)

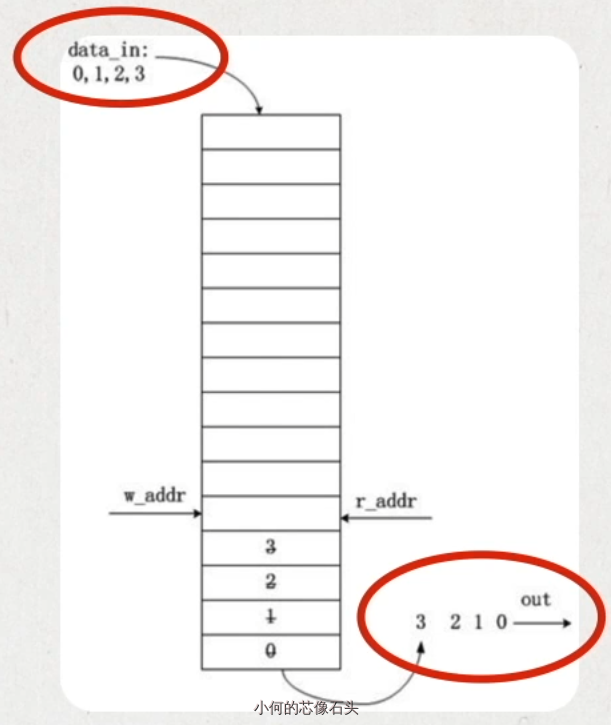

FIFO 是一種先進(jìn)先出的儲(chǔ)存結(jié)構(gòu) 與普通存儲(chǔ)器的區(qū)別:

- 沒(méi)有外部讀寫地址線

- 使用簡(jiǎn)單

缺點(diǎn)

- 只能順序?qū)懭霐?shù)據(jù),順序的讀出數(shù)據(jù),其數(shù)據(jù)地址由內(nèi)部讀寫指針自動(dòng)加1完成,不能像普通存儲(chǔ)器那樣可以由地址線決定讀取或?qū)懭肽硞€(gè)指定的地址。

在IC設(shè)計(jì)中,模塊與模塊之間的通信設(shè)計(jì)中,多時(shí)鐘的情況已經(jīng)不可避免;數(shù)據(jù)在不同時(shí)鐘域之間的傳輸很容易引起亞穩(wěn)態(tài);異步FIFO就是一種簡(jiǎn)單、快捷的解決方案。

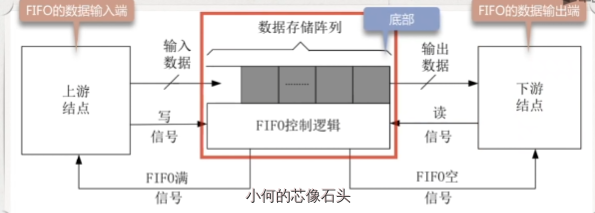

FIFO的功能類似于一個(gè)調(diào)節(jié)上下游水量的一個(gè) 蓄水池 。FIFO的上游結(jié)點(diǎn)是FIFO的數(shù)據(jù)輸入端,在寫信號(hào)有效時(shí),數(shù)據(jù)將被寫入FIFO,由FIFO內(nèi)部的寫指針控制,并且在FIFO內(nèi)部,寫指針遞增一個(gè)單元,同時(shí)FIFO的滿信號(hào)(FIFO full Signal)將控制上游結(jié)點(diǎn)是否發(fā)送數(shù)據(jù);FIFO的下游節(jié)點(diǎn)是FIFO的數(shù)據(jù)輸出端,當(dāng)讀信號(hào)有效時(shí),F(xiàn)IFO中的數(shù)據(jù)將被讀出,由FIFO內(nèi)部的讀指針控制,并且在FIFO內(nèi)部讀指針遞增一個(gè)單元,同時(shí)FIFO空信號(hào)(FIFO empty Signal))將控制下游節(jié)點(diǎn)是否讀出數(shù)據(jù)。如果FIFO內(nèi)部的空間已經(jīng)被寫滿,則實(shí)時(shí)生成滿信號(hào),以反壓上游節(jié)點(diǎn),上游節(jié)點(diǎn)停止寫新的數(shù)據(jù)進(jìn)來(lái),否則就會(huì)把已經(jīng)寫好的數(shù)據(jù)沖掉。如果FIFO內(nèi)部的數(shù)據(jù)全部被讀,則實(shí)時(shí)生成空信號(hào),控制下游節(jié)點(diǎn)不再進(jìn)行數(shù)據(jù)讀操作。否則,下游節(jié)點(diǎn)就會(huì)將讀過(guò)的數(shù)據(jù)重新再讀一遍。從這里也可以看出,空信號(hào)和滿信號(hào)對(duì)于FIFO的控制非常重要。

FIFO用途

- 用異步FIFO讀寫分別采用相互異步的不同時(shí)鐘

在現(xiàn)代集成電路芯片中,隨著設(shè)計(jì)規(guī)模的不斷擴(kuò)大,一個(gè)系統(tǒng)中往往含有數(shù)個(gè)時(shí)鐘多時(shí)鐘域帶來(lái)的一個(gè)問(wèn)題就是,如何設(shè)計(jì)異步時(shí)鐘之間的接口電路。異步FIFO是這個(gè)問(wèn)題的一種簡(jiǎn)便、快捷的解決方案,使用異步FIFO可以在兩個(gè)不同時(shí)鐘系統(tǒng)之間快速而方便地傳輸實(shí)時(shí)數(shù)據(jù)。 - 對(duì)于不同寬度的數(shù)據(jù)接口也可以用FIFO 例如單片機(jī)位8位數(shù)據(jù)輸出,而DSP可能是16位數(shù)據(jù)輸入,在單片機(jī)與DSP連接時(shí)就可以使用FIFO來(lái)達(dá)到數(shù)據(jù)匹配的目的。

FIFO類型

- 同步FIFO : 指讀時(shí)鐘和寫時(shí)鐘為同一個(gè)時(shí)鐘,在時(shí)鐘沿來(lái)臨時(shí)同時(shí)發(fā)生讀寫操作

- 異步FIFO : 指讀寫時(shí)鐘不一致,讀寫時(shí)鐘是互相獨(dú)立的。

FIFO的設(shè)計(jì)對(duì)調(diào)節(jié)上下游的吞吐量平衡具有非常重要的作用

FIFO常見參數(shù)

- FIFO的寬度:即FIFO一次讀寫操作的數(shù)據(jù)位:

- FIFO的深度:指的是FIFO可以存儲(chǔ)多少個(gè)N位的數(shù)據(jù)(如果寬度為N)。FIFO的深度相當(dāng)于蓄水池的容量,如果過(guò)小,則上游節(jié)點(diǎn)總是接收滿信號(hào),使得系統(tǒng)的數(shù)據(jù)吞吐量降低。如果過(guò)大,則浪費(fèi)空間太多。因此,F(xiàn)IFO的深度是一個(gè)很關(guān)鍵的參數(shù)。

- 滿標(biāo)志:FIFO已滿或?qū)⒁獫M時(shí)由FIFO的狀態(tài)電路送出的一個(gè)信號(hào),以阻止FIFO的寫操作繼續(xù)向FIFO中寫數(shù)據(jù)而造成溢出(overflow).

- 空標(biāo)志:FIFO已空或?qū)⒁諘r(shí)由FIFO的狀態(tài)電路送出的一個(gè)信號(hào),以阻止FIFO的讀操作繼續(xù)從FIFO中讀出數(shù)據(jù)而造成無(wú)效數(shù)據(jù)的讀出(underflow)。如我們前面講述,空滿標(biāo)志非常重要。本節(jié)我們重點(diǎn)討論如何設(shè)計(jì)空滿標(biāo)志位電路。

- 讀時(shí)鐘:讀操作所遵循的時(shí)鐘,在每個(gè)時(shí)鐘沿來(lái)臨時(shí)讀數(shù)據(jù)。

- 寫時(shí)鐘:寫操作所遵循的時(shí)鐘,在每個(gè)時(shí)鐘沿來(lái)臨時(shí)寫數(shù)據(jù)。在FIFO中,這兩個(gè)時(shí)鐘通常都不相同,而且以異步時(shí)鐘。

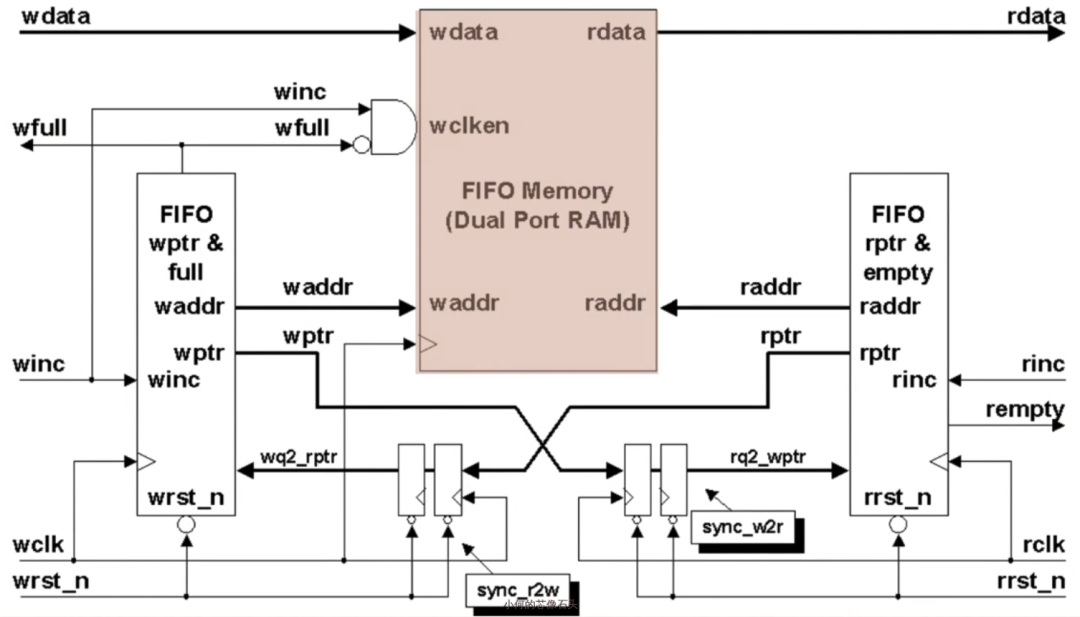

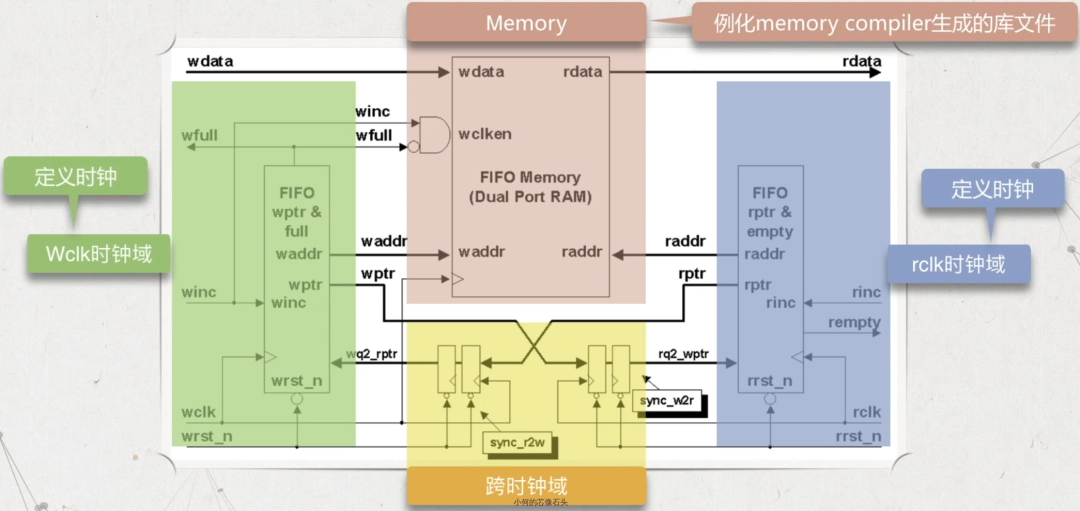

FIFO的總體結(jié)構(gòu)

結(jié)構(gòu)如下:

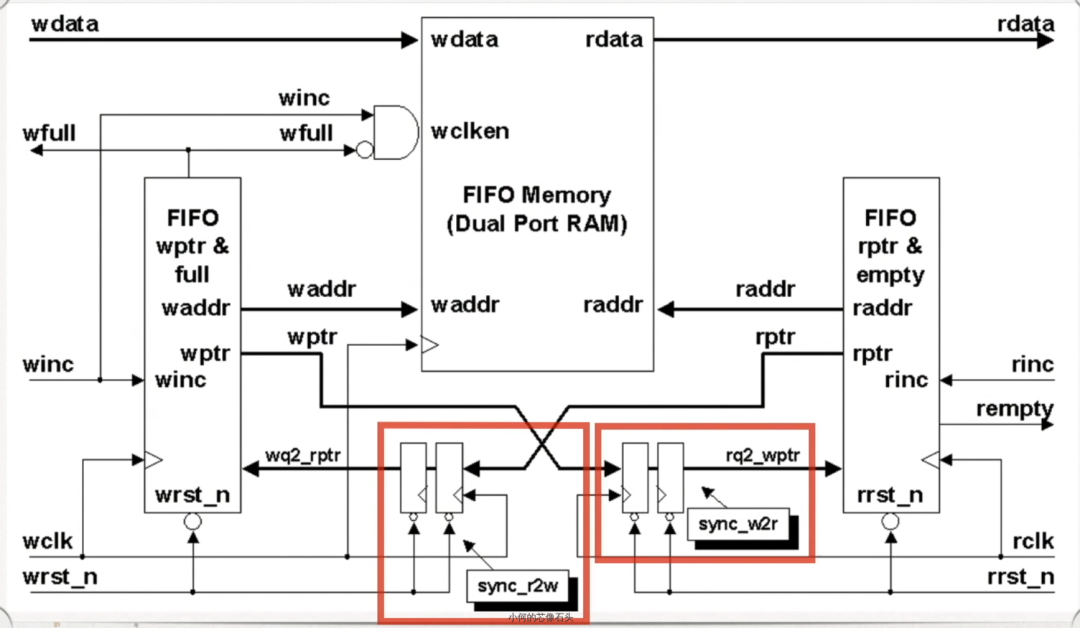

image-20221009122620242

- 雙端口SRAM,用來(lái)存儲(chǔ)上游節(jié)點(diǎn)寫入的數(shù)據(jù)wdata,下游節(jié)點(diǎn)用rdata將其讀出.SRAM的 讀寫地址采用了每次只遞增1的機(jī)制 ,保證了寫入和讀出按順序進(jìn)行,寫和讀到最高地址后,重新返回零地址。

- 在上游節(jié)點(diǎn)和SRAM之間有一個(gè) 滿信號(hào)生成電路 ,這個(gè)電路通過(guò)判斷寫時(shí)鐘域下,寫指針和讀指針的關(guān)系,然后實(shí)時(shí)生成滿信號(hào)w1,以通知上游節(jié)點(diǎn)停止寫操作。

- 同樣地,在下游節(jié)點(diǎn)和SRAM之間有一個(gè) 空信號(hào)生成電路 ,這個(gè)電路通過(guò)判斷讀時(shí)鐘域下,寫指針和讀指針的關(guān)系,然后實(shí)時(shí)生成空信號(hào)empty,以通知下游節(jié)點(diǎn)停止讀操作。

- 這兩個(gè)模塊的工作機(jī)制是我們要重點(diǎn)關(guān)注的。這里還需要注意的是,將讀 指針傳遞到寫時(shí)鐘域才能產(chǎn)生滿信號(hào) ,將 寫指針傳遞到讀時(shí)鐘域才能產(chǎn)生空信號(hào) ,因此,這里就涉及到如何處理信號(hào)傳輸?shù)膩喎€(wěn)態(tài)問(wèn)題。

設(shè)計(jì)關(guān)鍵:

- 亞穩(wěn)態(tài)的消除

- 空滿狀態(tài)的判斷-> 正確的產(chǎn)生空滿標(biāo)志是任何FIFO設(shè)計(jì)的關(guān)鍵

- 空滿狀態(tài)產(chǎn)生的原則是:寫滿而不溢出,能讀空而不多讀。

空滿狀態(tài)的判斷

讀寫指針相等 會(huì)觸發(fā)滿還是空,得看讀寫的指針?lè)较蚴窃鯓拥?/p>

空狀態(tài)

當(dāng)讀寫指針相等時(shí),表明FIFO為空,這種情況發(fā)生在復(fù)位操作時(shí)或者當(dāng)讀指針讀出FIFO中最后一個(gè)字后,追趕上了寫指針;

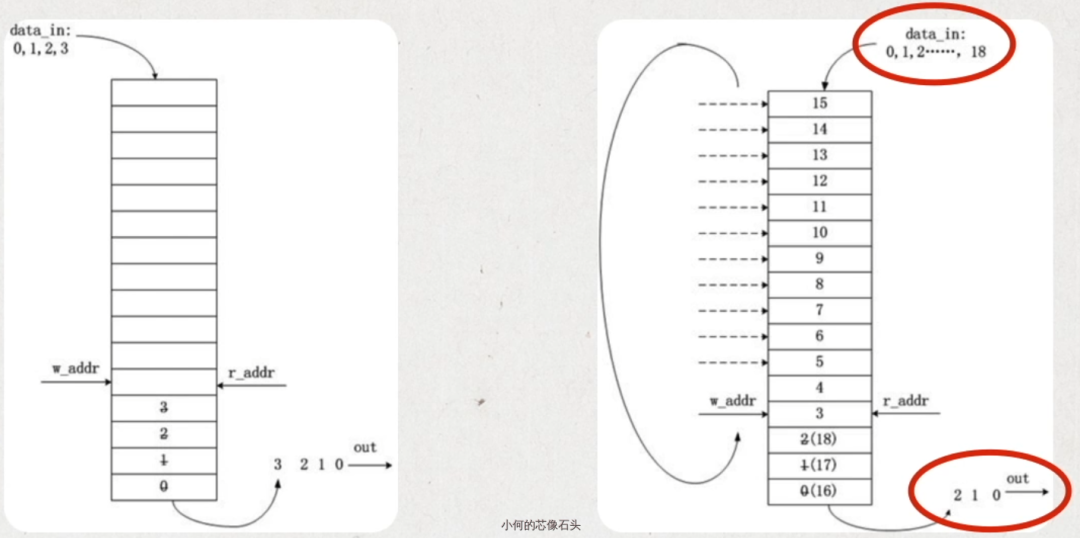

當(dāng)讀寫地址相等時(shí),說(shuō)明已經(jīng)寫入的數(shù)據(jù),已經(jīng)全部被讀走,此時(shí),F(xiàn)IFO還尚未有新的數(shù)據(jù)寫入,說(shuō)明FIFO為空,這種情況發(fā)生在復(fù)位操作時(shí),或者當(dāng)讀地址讀出FIFO中最后一個(gè)字后,追趕上了寫地址。如果兩個(gè)指針的MSB相同,則說(shuō)明兩個(gè)指針折回的次數(shù)相等。其余位相等,說(shuō)明FIFO為空

滿狀態(tài)

滿狀態(tài)。當(dāng)寫地址超過(guò)讀地址,寫到最高地址后,重新從0開始寫,再次追上了讀地址。此時(shí),讀地址已經(jīng)讀過(guò)的地址空間,再一次被寫地址寫入。而讀地址到最高地址之間的數(shù)據(jù),還尚未被讀。說(shuō)明此時(shí)FIFO處于滿的狀態(tài)。如果兩個(gè)指針的MSB不同,說(shuō)明寫指針比讀指針多折回了一次;如raddr=0000,而w_addr=1000,為滿。

區(qū)別滿和空狀態(tài)

- 在地址中添加一個(gè)額外的位(extra bit),當(dāng) 寫指針增加并越過(guò)最后一個(gè)FIFO地址時(shí),就將寫指針這個(gè)未用的MSB加1 , 其它位回零 。對(duì)讀指針也進(jìn)行同樣的操作。此時(shí),對(duì)于深度為2”的FIFO,需要的讀/寫指針位寬為(n+1)位,如對(duì)于深度為8的FIFO,需要采用4bit的計(jì)數(shù)器,0000

1000、100111111 MSB作為折回標(biāo)志位,而低3位作為地址指針。 - 如果兩個(gè)指針的MSB不同,說(shuō)明寫指針比讀指針多折回了一次;如r_addr=0000,而w_addr = 1000,為滿。

- 如果兩個(gè)指針的MSB相同,則說(shuō)明兩個(gè)指針折回的次數(shù)相等。其余位相等,說(shuō)明FIFO為空。

- 空滿標(biāo)志生成的前提是:

- 讀指針被傳遞到了寫時(shí)鐘域

- 寫指針被傳遞到了讀時(shí)鐘域

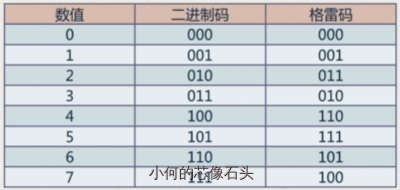

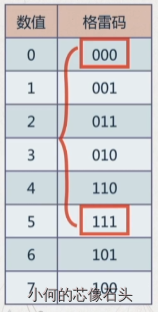

介入格雷碼

在上一節(jié)中說(shuō)過(guò), 多bit信號(hào)是不能直接通過(guò)這種打兩拍進(jìn)行同步的 ,所以我們需要采用格雷碼進(jìn)行傳輸。傳輸讀寫指針之前,需要將其先由二進(jìn)制轉(zhuǎn)為格雷碼,然后再發(fā)送到對(duì)方的時(shí)鐘域下。

格雷碼特點(diǎn):

- 格雷碼相鄰的2個(gè)數(shù)值之間只會(huì)有一位發(fā)生變化,其余各位都相同 ;

- 格雷碼是一種循環(huán)碼和最大數(shù)(2的n次方減1)之間也只有一位不同。

引用格雷碼之后,相鄰值只有1位發(fā)生翻轉(zhuǎn),1位翻轉(zhuǎn)所引起的亞穩(wěn)態(tài)的概率遠(yuǎn)遠(yuǎn)要小于幾位同時(shí)翻轉(zhuǎn)所引起的概率;因此, 格雷碼能很好的亞穩(wěn)態(tài)出現(xiàn)的概率 。

轉(zhuǎn)化方法:

- 二進(jìn)制碼轉(zhuǎn)化為格雷碼:從最右邊第一位開始,依次將每一位與左鄰一位異或(XOR),作為對(duì)應(yīng)格雷碼該位的值,最左邊一位不變;

- 格雷碼轉(zhuǎn)化為二進(jìn)制碼:從左邊第二位起,將每位與左邊一位解碼后的值異或(XOR),作為該位解碼后的值(最左邊一位依然不變)。

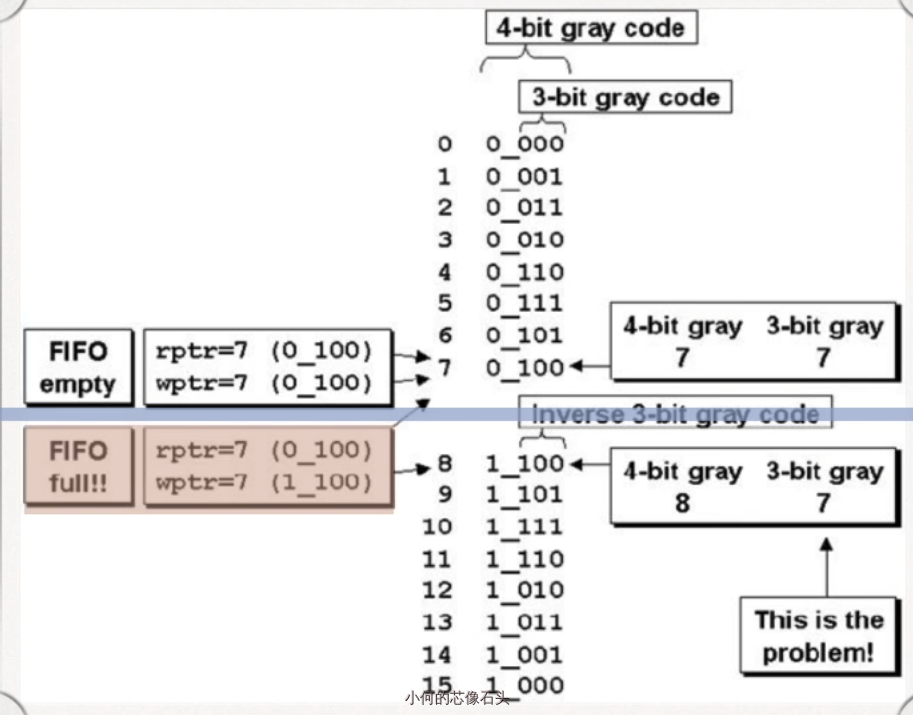

格雷碼下的空滿判斷

- 如果采用格雷碼,對(duì)于“空"的判斷依然依據(jù)二者完全相等。

- 對(duì)于“滿"的判斷,由于格雷碼除了MSB外,具有鏡像對(duì)稱的特點(diǎn),當(dāng)讀指針指向7,寫指針指向8時(shí),注意地址增加到最大地址7時(shí),然后會(huì)返回0, 所以此處8和0雖然輪次不同,但是實(shí)際上是同一個(gè)地址 。此時(shí),除了MSB,其余位皆相同,就不能說(shuō)它為滿。在格雷碼上判斷為滿必須同時(shí)滿足以下3條:wptr和同步過(guò)來(lái)的rptr的MSB不相等,因?yàn)閣ptr必須比rptr多折回一次;wptr與rptr的次高位不相等;剩下的其余位完全相等。

所以在gray碼上判斷為滿必須同時(shí)滿足以下三條:

- wptr和同步過(guò)來(lái)的rptr的MSB不相等,因?yàn)閣ptr必須比rptr多折回一次。

- wptr與rptr的次高位不相等,如上圖位置7和位置15,轉(zhuǎn)化為二進(jìn)制對(duì)應(yīng)的是0111和1111,MSB不同說(shuō)明多折回一次,111相同代表同一位置。

- 剩下的其余位完全相等。

當(dāng)FIFO深度不為2的次冪時(shí)

當(dāng)FIFO深度不為2的次冪時(shí),格雷碼的翻轉(zhuǎn)變化就不是1 bit了

假設(shè)FIFO深度為8,則讀寫指針可采用格雷碼進(jìn)行編碼;

假設(shè)FIFO深度為6,如果讀寫指針繼續(xù)采用格雷碼,那么當(dāng)前首尾指針的所有比特位都不相同,此時(shí),如果從尾部返回首部,則無(wú)法實(shí)現(xiàn)消除亞穩(wěn)態(tài)的目的。

此時(shí),首地址是000,尾地址為111,沒(méi)辦法消除亞穩(wěn)態(tài)。解決方法:

- 可將地址為5的指針設(shè)定為100,此時(shí)其與首地址的指針“000”相差一個(gè)bit位,與地址為4的指針“110”也相差一個(gè)bit位,滿足消除亞穩(wěn)態(tài)的要求。

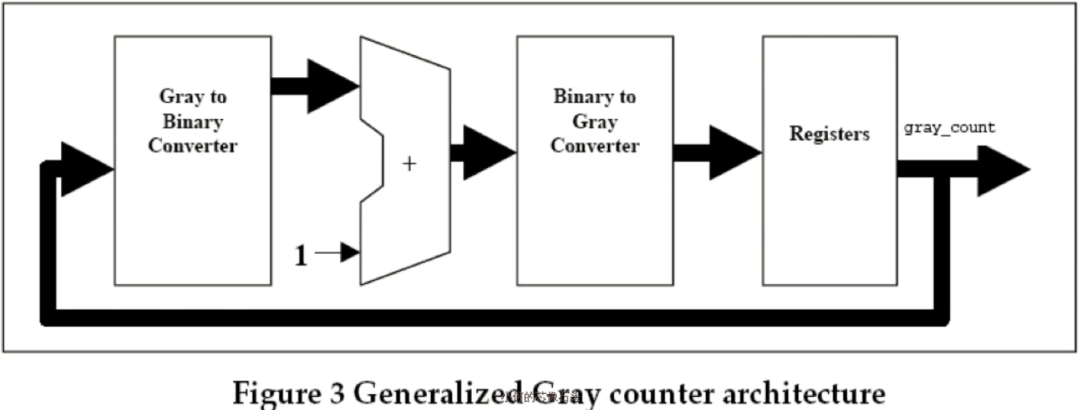

怎么設(shè)計(jì)讀寫指針的編碼

- 并不是一定要用格雷碼做讀寫指針,而是當(dāng)深度為2次冪的時(shí)候,剛好格雷碼滿足消除亞穩(wěn)態(tài)的需求;

- 在非2次冪深度情況下,格雷碼已經(jīng)不再適用,此時(shí)的解決方法通常有:

- 若深度為偶數(shù),可采用最接近的2次冪的格雷碼編碼,在此基礎(chǔ)上修改;

- 深度為一般數(shù)值時(shí),可自行設(shè)計(jì)一種邏輯電路,或者查找表,以實(shí)現(xiàn)指針每次只跳變一次的功能;

- 以上方法通常在設(shè)計(jì)層面較為復(fù)雜,若無(wú)特定需求,可將FIFO深度設(shè)置為2次冪,浪費(fèi)一些存儲(chǔ)空間,來(lái)化簡(jiǎn)控制電路的復(fù)雜度。

FIFO深度設(shè)計(jì)

面試題++

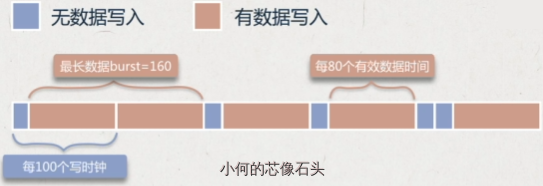

例題1

假設(shè)FIFO的寫時(shí)鐘為100 MHz,讀時(shí)鐘為80 MHz。在FIFO輸入側(cè),每100個(gè)寫時(shí)鐘,寫入80個(gè)數(shù)據(jù);讀數(shù)據(jù)側(cè),假定每個(gè)時(shí)鐘讀走一個(gè)數(shù)據(jù)。

請(qǐng)問(wèn)FIFO深度設(shè)置多少可以保證FIFO不會(huì)上溢出和下溢出?

對(duì)圖,先找到最重載的情況:

最長(zhǎng)burst寫入時(shí)間為:

這段時(shí)間能 最小讀走的數(shù)據(jù)量 :

這樣就可以得到在 最差情況下留在FIFO中的數(shù)據(jù) :

抽象一下:

寫時(shí)鐘頻率為WCLK:讀時(shí)鐘頻率為RCLK:寫時(shí)每B個(gè)時(shí)鐘周期內(nèi)會(huì)有A個(gè)數(shù)據(jù)寫入FIFO,說(shuō)明寫入效率是A/B,讀時(shí)每Y個(gè)時(shí)鐘周期內(nèi)會(huì)有X個(gè)數(shù)據(jù)讀出FIFO,說(shuō)明讀出效率是X/Y。這種情況下,F(xiàn)IFO的最小深度是多少?

(burst_length/WCLK)表示這個(gè)burst的持續(xù)時(shí)間,持續(xù)時(shí)間乘以讀時(shí)鐘頻率,可知道讀數(shù)據(jù)在效率100%的時(shí)候的讀出數(shù)據(jù)個(gè)數(shù),然后再乘以讀數(shù)據(jù)效率X/Y)則可知道在bust時(shí)間段內(nèi)讀出了多少數(shù)據(jù)。burst length與這個(gè)讀出數(shù)據(jù)的差值,F(xiàn)IFO中殘留的數(shù)據(jù),這個(gè)也就是理論上的FIFO的最小深度。

FIFO中的亞穩(wěn)態(tài)問(wèn)題

這里會(huì)結(jié)合上一節(jié)對(duì)異步FIFO進(jìn)行分析:

- 亞穩(wěn)態(tài)不能從根本上消除 ,但可以通過(guò)采取一定的措施使其對(duì)電路造成的影響降低。

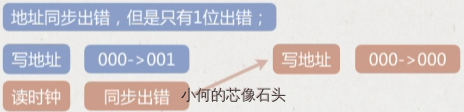

為什么優(yōu)先用格雷碼做讀寫指針編碼

如果指針為格雷碼,失效的后果?

格雷碼一次只有一位數(shù)據(jù)發(fā)生變化,這樣在進(jìn)行地址同步的時(shí)候,只有兩種情況:

也就是地址沒(méi)有跳變,但是用這個(gè)錯(cuò)誤的寫地址去做空判斷不會(huì)出錯(cuò),最多是讓空標(biāo)志在FIFO不是真正空的時(shí)候產(chǎn)生,而不會(huì)出現(xiàn)空讀的情形。

所以,gray碼保證的是同步后的讀寫地址即使在出錯(cuò)的情形下依然能夠保證FIFO功能的正確性,當(dāng)然同步后的讀寫地址出錯(cuò)總是存在的。

需要注意gray碼只是在相鄰兩次跳變之間才會(huì)出現(xiàn)只有1位數(shù)據(jù)不一致的情形超過(guò)兩個(gè)周期則不一定,所以,地址總線bus skew一定不能超過(guò)一個(gè)周期,否則可能出現(xiàn)gray碼多位數(shù)據(jù)跳變的情況,這個(gè)時(shí)候gray碼就失去了作用,因?yàn)檫@時(shí)候同步后的地址已經(jīng)不能保證只有1位跳變了。

兩拍同步或多拍同步的差異

將地址總線打兩拍 -> 為了避免亞穩(wěn)態(tài)傳播

但是并不能消除亞穩(wěn)態(tài):

- 因?yàn)闀r(shí)鐘異步,亞穩(wěn)態(tài)不可避免,但是可以極大降低亞穩(wěn)態(tài)傳播的概率,

在低頻情況下:

STA不需要分析這里的異步時(shí)序,因?yàn)?a href="http://m.1cnz.cn/tags/寄存器/" target="_blank">寄存器都可以在一拍內(nèi)將亞穩(wěn)態(tài)消除,恢復(fù)到正常0/1態(tài)。

在高頻情況下:

不一定,尤其在 28nm工藝以下,需要檢查兩級(jí)觸發(fā)器的延遲 ,保證延遲低,提高系統(tǒng)MTBF。

對(duì)多拍同步,能夠進(jìn)一步將亞穩(wěn)態(tài)出現(xiàn)的概率降低

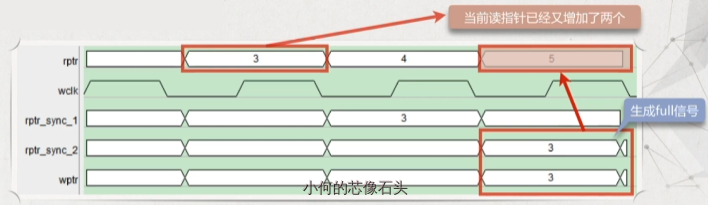

空滿標(biāo)志的判斷方法是否漏洞

對(duì)打兩拍后,讀寫指針的動(dòng)作為:

- rptr同步**兩個(gè)“wclk”**后,在wclk時(shí)鐘域與wptr進(jìn)行比較,生成full信號(hào)

- wptr同步**兩個(gè)“rclk”**后,在rclk時(shí)鐘域與rptr進(jìn)行比較,生成empty信號(hào)

假設(shè)讀寫時(shí)鐘頻率接近

這個(gè)時(shí)候看滿的時(shí)候并不是真滿,因?yàn)榇藭r(shí)又都走了兩個(gè)數(shù)據(jù)

結(jié)論:

- 對(duì)于full信號(hào)的生成機(jī)制,同步后的讀地址一定是小于或者等于當(dāng)前的讀地址,所以此時(shí)判斷FIFO為滿不一定是真滿,這樣更保守;

- Empty信號(hào)的機(jī)制同樣成立,“空”時(shí),不一定是真“空”。

- 異步FIFO通過(guò)比較讀寫地址進(jìn)行滿空判斷,但是讀寫地址屬于不同的時(shí)鐘域,所以在比較之前需要先將讀寫地址進(jìn)行同步處理,此機(jī)制保證了FIFO在空滿極限情況下,依然留有余量,存在一定的冗余空間。

頻率相差較大時(shí),同步時(shí)間可以

如何對(duì)FIFO進(jìn)行邏輯綜合和靜態(tài)時(shí)序分析

模塊劃分:

在低頻情況:

- 設(shè)置wclk和rclk之間的false path

在高頻情況下:

- 尤其在28 nm工藝以下,需要檢查兩級(jí)觸發(fā)器的延遲,保證延遲低;

在布局布線(P&R)時(shí)

- 要注意將兩級(jí)同步器放置在一起,不要被工具自動(dòng)分開

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論