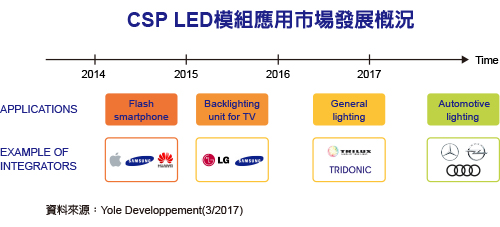

發(fā)光二極體(LED)封裝廠在生態(tài)系統(tǒng)將日趨邊緣化。上游LED晶粒廠為降低制造成本與微型化晶片尺寸,競(jìng)相展開(kāi)晶粒尺寸封裝(Chip Scale Package, CSP)技術(shù)布局,且該技術(shù)省略封裝制程,遂讓磊晶廠未來(lái)營(yíng)運(yùn)模式將跳過(guò)封裝廠,直接與下游燈具系統(tǒng)商合作,導(dǎo)致封裝廠在供應(yīng)鏈的重要性大幅下降。

2014-05-06 09:03:50 1776

1776 LED臺(tái)廠新世紀(jì)光電近年來(lái)在CSP產(chǎn)品的發(fā)展和出貨,已經(jīng)在日本與歐美海外市場(chǎng)逐漸發(fā)酵,筆者日前訪(fǎng)談了新世紀(jì)光電總經(jīng)理陳政權(quán),為業(yè)界讀者分析與探究新世紀(jì)光電在覆晶(Flip-chip)技術(shù)發(fā)展下做到的CSP晶圓級(jí)封裝LED產(chǎn)品,究竟有哪些優(yōu)勢(shì)與未來(lái)可應(yīng)用的利基型市場(chǎng)。

2016-02-02 09:38:55 1542

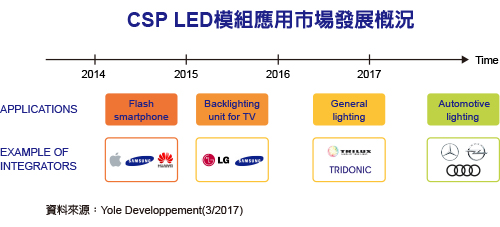

1542 LED封裝技術(shù)出現(xiàn)新面孔。一般半導(dǎo)體廠商已經(jīng)相當(dāng)熟悉的芯片級(jí)封裝(Chip Scale Package, CSP),正逐漸滲透到LED領(lǐng)域,如手機(jī)閃光燈與液晶電視背光用的LED皆已開(kāi)始導(dǎo)入此一技術(shù)。

2017-03-27 09:32:36 2770

2770

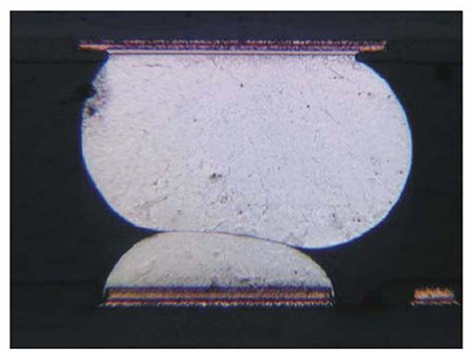

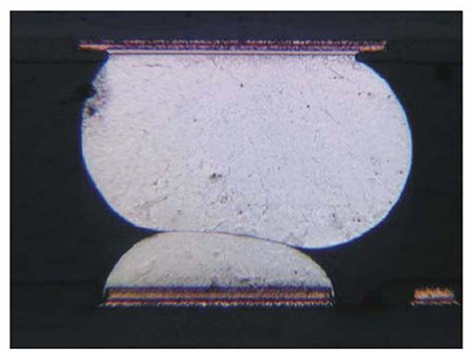

本文將系統(tǒng)、全面地介紹 BGA 和 CSP 封裝器件“枕頭效應(yīng)”產(chǎn)生機(jī)理、原因分析、以及結(jié)合作者10多年來(lái)的現(xiàn)場(chǎng)實(shí)際改善案例經(jīng)驗(yàn)匯總,詳細(xì)講解“枕頭效應(yīng)”的如何改善和預(yù)防的措施,希望此文能為電子裝聯(lián)的業(yè)界的朋友提供一些借鑒和參考作用,提升各自公司/工廠的SMT產(chǎn)線(xiàn)的CSP/BGA類(lèi)器件的焊接工藝水平。

2021-11-04 17:20:18 22556

22556

1. BGA和CSP封裝技術(shù)詳解 2.?干貨分享丨BGA開(kāi)路金相切片分析 (BGA Open Cross-Section) ? ? ? 審核編輯:彭靜

2022-07-26 14:43:18 5181

5181 請(qǐng)問(wèn)大家,0.4pitch的CSP封裝是怎么布線(xiàn)的,間距太小了

2016-06-29 21:36:01

CSP-6R0L255R-TW

2023-03-29 22:41:45

在便攜式、低引腳數(shù)和低功率產(chǎn)品中應(yīng)用廣泛,主要用于閃存、RAM、DRAM存儲(chǔ)器等產(chǎn)品中。目前,超過(guò)100家公司開(kāi)發(fā)CSP產(chǎn)品:Amkor、Tessera、Chip-scale、Sharp等,市場(chǎng)潛力巨大。

2020-03-18 09:01:54

csp模式不知道是哪里出現(xiàn)了問(wèn)題?csp模式為什么不能讓電機(jī)轉(zhuǎn)起來(lái)?

2021-09-24 06:24:56

、無(wú)阻抗IC白/藍(lán)膜片、長(zhǎng)期高價(jià)求購(gòu)封裝測(cè)試廠淘汰的廢舊QFN、PLCC、BGA、CSP、WL-CSP等各種封裝后的IC芯片、Blue tape、chip、wafer.藍(lán)膜片、白膜片、IC硅片、IC晶

2020-12-29 08:27:02

CYD3175PD做一個(gè)A口,CSP做A的地 還是GND 做地。CSP和GND之間需要串電阻嗎?

2024-02-28 06:45:20

EtherCAT igh主站是如何控制松下伺服(csp模式)的?怎樣去編寫(xiě)其代碼?

2021-10-08 06:12:54

現(xiàn)有裝配架構(gòu)輕松采用等特性。芯片級(jí)封裝 (CSP) 能在提供裸片的尺寸優(yōu)勢(shì)的同時(shí)還可以帶來(lái)封裝的許多優(yōu)勢(shì)。在無(wú)線(xiàn)手持終端市場(chǎng)需求的推動(dòng)下,CSP產(chǎn)品正不斷推陳出新。例如,采用0.84 x

2011-06-16 16:12:03

初學(xué)者,請(qǐng)老師們幫忙解疑!PBGA,CSP,SOP分別是什么意思.

2013-01-17 16:52:09

DIODESBR30V1A2CSP

2023-03-22 15:48:05

SDM2U20CSP-7

2023-03-28 13:13:28

改變板鍵合盤(pán)尺寸,就能明顯提高可靠性。 CSP應(yīng)用 如今人們常見(jiàn)的一種關(guān)鍵技術(shù)是CSP。CSP技術(shù)的魅力在于它具有諸多優(yōu)點(diǎn),如減小封裝尺寸、增加針數(shù)、功能∕性能增強(qiáng)以及封裝的可返工性等。 CSP

2013-10-22 11:43:49

。典型封裝昂貴而易損壞,特別是在器件引線(xiàn)成形之后。這些復(fù)雜技術(shù)的設(shè)計(jì)指導(dǎo)原則也與普通SMT工藝有很大差異,因?yàn)樵诖_保組裝生產(chǎn)率和產(chǎn)品可靠性方面,板設(shè)計(jì)扮演著更為重要的角色; 例如,對(duì)CSP焊接互連

2018-09-10 15:46:13

; CSP封裝優(yōu)勢(shì) ü 封裝尺寸更小,功率更大ü 體積更小,設(shè)計(jì)更靈活ü 無(wú)框架載體,寄生參數(shù)小ü 散熱好ü 先進(jìn)制程,成品率高ü 高可靠性,高生產(chǎn)效率 微小型CSP封裝 適合TVS,diodes

2020-07-30 14:40:36

qfpn封裝的散熱焊盤(pán)的soldmask層為什么要按照下圖的來(lái)做

2014-11-15 14:51:23

`什么? 你對(duì)CSP的了解還不夠?趕快來(lái)圍觀吧! 首先,得知道什么叫CSPCSP(Chip Scale Package),又稱(chēng)為芯片級(jí)封裝器件, 其技術(shù)性主要體現(xiàn)為讓芯片面積與封裝面積之比超過(guò)1

2017-02-24 16:36:32

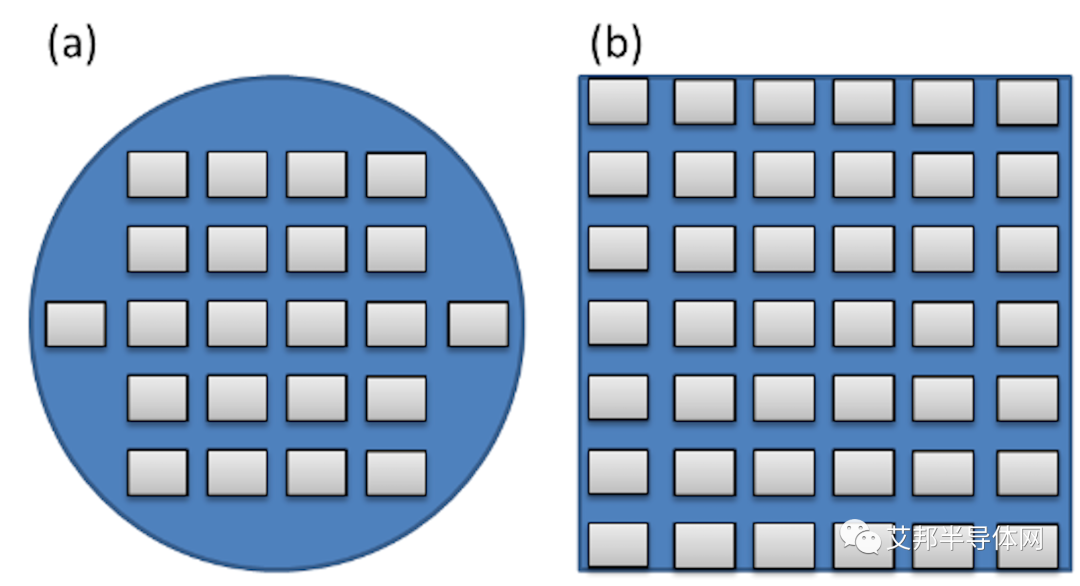

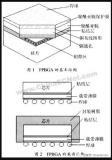

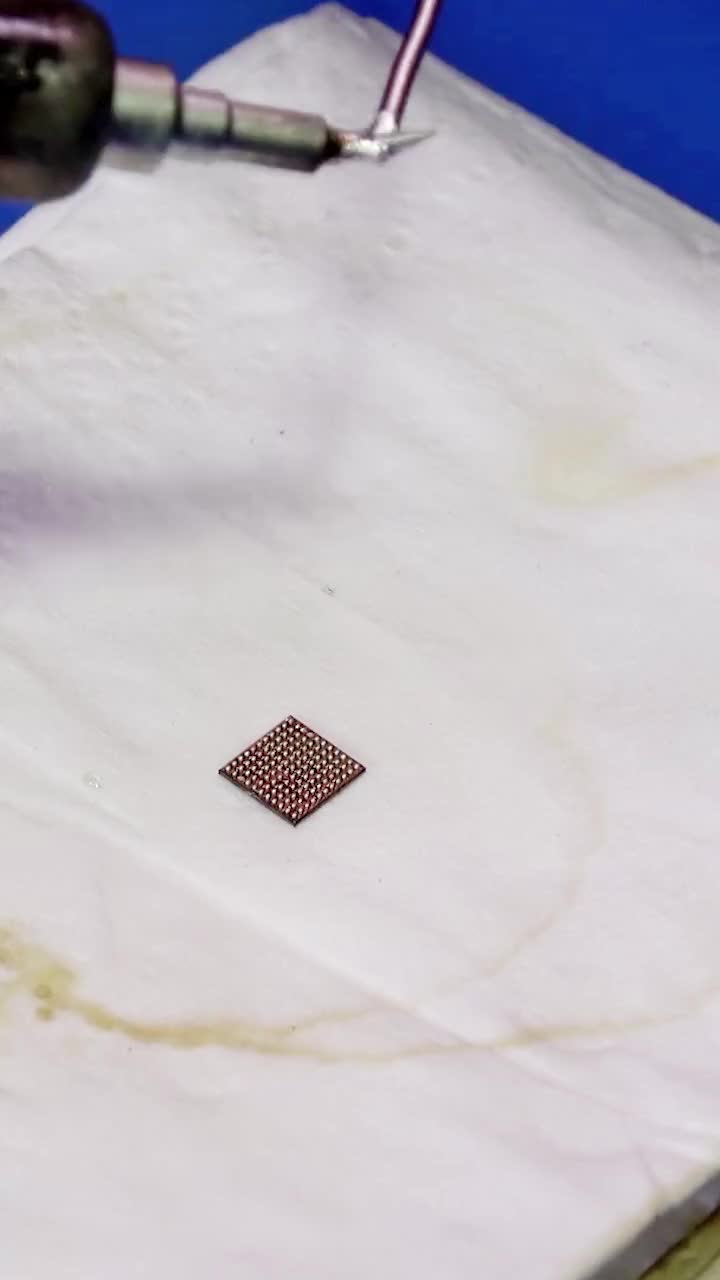

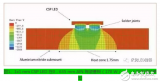

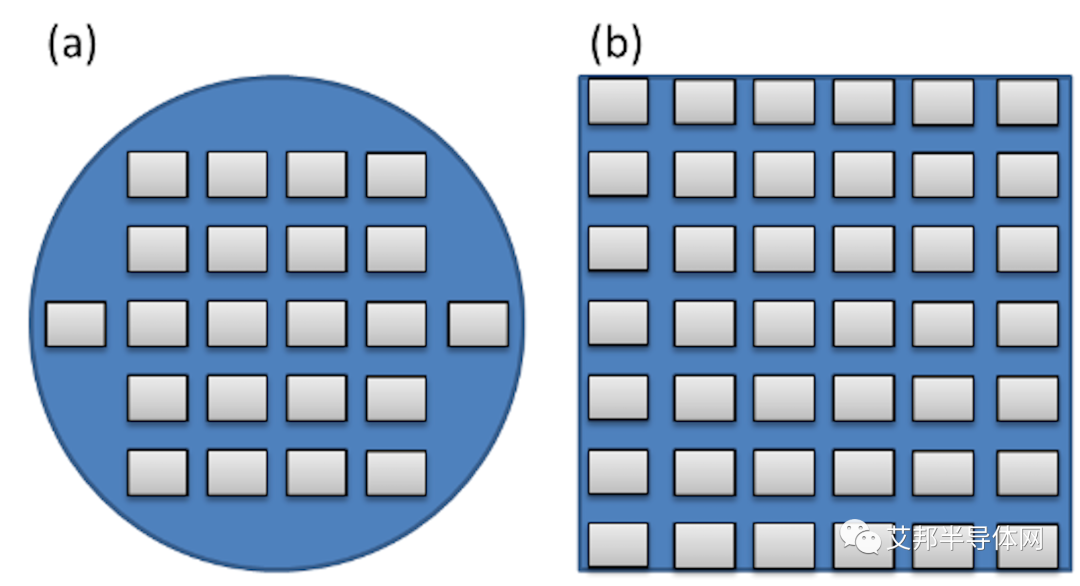

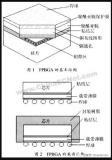

發(fā)展趨勢(shì)的推動(dòng)下,制造商開(kāi)發(fā)出更小的封裝類(lèi)型。最小的封裝當(dāng)然是芯片本身,圖1描述了IC從晶片到單個(gè)芯片的實(shí)現(xiàn)過(guò)程,圖2為一個(gè)實(shí)際的晶片級(jí)封裝(CSP)。 晶片級(jí)封裝的概念起源于1990年,在1998年

2018-08-27 15:45:31

無(wú)線(xiàn)手持設(shè)備、掌上電腦以及其他移動(dòng)電子設(shè)備的增加導(dǎo)致了消費(fèi)者對(duì)各種小外形、特征豐富產(chǎn)品的需要。為了滿(mǎn)足越來(lái)越小的器件同時(shí)具有更多功能的市場(chǎng)趨勢(shì)和移動(dòng)設(shè)計(jì)要求,業(yè)界開(kāi)發(fā)了芯片級(jí)封裝(CSP)形式的特定

2018-11-23 16:58:54

(1)從封裝效率進(jìn)行比較。DIP最低(約2%~7%),QFP次之(可達(dá)10%~30%),BGA和PGA的效率較高(約為20%~80%),CSP最高(可于70%~85%)。 (2)從封裝厚度進(jìn)行比較

2018-11-26 16:16:49

怎么選擇晶圓級(jí)CSP裝配工藝的錫膏?

2021-04-25 08:48:29

首先,要看芯片面積與封裝面積之比,這個(gè)比值越接近1越好。當(dāng)然這個(gè)比值永遠(yuǎn)也不可能等于1,那應(yīng)該稱(chēng)作“裸晶”。例如采用40根引腳的塑封雙列直插式封裝(PDIP)的CPU為例,其芯片面積/封裝面積

2011-10-28 10:51:06

;導(dǎo)熱膠:硅樹(shù)脂;散熱板:銅。目前,國(guó)際上FCBGA的典型系列示于表1。 3.2 芯片尺寸封裝(CSP) CSP(Chip Scale Package)封裝,是芯片級(jí)封裝的意思。CSP封裝最新一代

2018-09-12 15:15:28

引言 無(wú)引線(xiàn)導(dǎo)線(xiàn)封裝(LLP)是一種基于導(dǎo)線(xiàn)架的晶片級(jí)封裝(CSP),它可以提高芯片的速度、降低熱阻并減小貼裝芯片所需要的PCB面積。由于這種封裝的尺寸小、高度很低,所以此封裝是高密度PCB

2018-09-10 16:37:26

晶圓級(jí)CSP的返修工藝包括哪幾個(gè)步驟?晶圓級(jí)CSP對(duì)返修設(shè)備的要求是什么?

2021-04-25 08:33:16

目前有兩種典型的工藝流程,一種是考慮與其他元件的SMT配,首先是錫膏印刷,然后貼裝CSP,回流焊接,最后如果要求底部填充,還需進(jìn)行底部填充工藝,如圖1所示。為了避免“橋連”或“少錫”缺陷,在組裝

2018-09-06 16:24:04

晶圓級(jí)CSP裝配回流焊接工藝控制,看完你就懂了

2021-04-25 06:28:40

經(jīng)底部填充的CSP裝配,其穩(wěn)健的機(jī)械連接強(qiáng)度得到很大的提升。在二級(jí)裝配中,由于底部填充,其抵御 由于扭轉(zhuǎn)、振動(dòng)和熱疲勞應(yīng)力的能力得以加強(qiáng)。但經(jīng)過(guò)底部填充的CSP如何進(jìn)行返修成了我們面臨

2018-09-06 16:32:17

,20世紀(jì)最后二十年,隨著微電子、光電子工業(yè)的巨變,為封裝技術(shù)的發(fā)展創(chuàng)造了許多機(jī)遇和挑戰(zhàn),各種先進(jìn)的封裝技術(shù)不斷涌現(xiàn),如BGA、CSP、FCIP、WLP、MCM、SIP等,市場(chǎng)份額不斷增加,2000年已達(dá)

2018-08-23 12:47:17

;導(dǎo)熱膠:硅樹(shù)脂;散熱板:銅。目前,國(guó)際上FCBGA的典型系列示于表1。

3.2 芯片尺寸封裝(CSP)

CSP(Chip Scale Package)封裝,是芯片級(jí)封裝的意思。CSP封裝最新一代

2023-12-11 01:02:56

芯片封裝測(cè)試流程詳解ppt?按封裝外型可分為:SOT 、QFN 、SOIC、TSSOP、QFP、BGA、CSP等;? 決定封裝形式的兩個(gè)關(guān)鍵因素:?封裝效率。芯片面積/封裝面積,盡量接近1:1

2012-01-13 11:46:32

請(qǐng)問(wèn)ADN4670BCPZ焊接溫度曲線(xiàn)有么?以及這種CSP封裝的焊接需要注意的事項(xiàng)有哪些?

2019-01-18 16:44:20

由于疊層CSP封裝的復(fù)雜性,其振動(dòng)特性很難用精確的理論模型表示。同時(shí),由于傳統(tǒng)的共振準(zhǔn)則沒(méi)有考慮到系統(tǒng)的變異性和模糊性,導(dǎo)致分析結(jié)果與真值具有較大偏差。該文利用

2009-02-27 15:37:11 9

9 電子元器件的封裝形式,元器件封裝形式

大的來(lái)說(shuō),元件有插裝和貼裝. 1.BGA 球柵陣列封裝 2.CSP 芯片縮放式封裝 3.COB 板上芯片貼裝 4.COC 瓷質(zhì)基

2009-05-05 10:10:10 322

322 CSP產(chǎn)品簡(jiǎn)介封裝完成後之面積(Footprint)約為晶片(Die)之1.2倍依其結(jié)構(gòu)可分為四類(lèi)Flex Circuit InterposerRigid Substrate InterposerLead Frame (Lead-on-Chip)Wafer Level Assembly可靠度簡(jiǎn)

2009-07-06 09:28:14 12

12 基于進(jìn)程代數(shù)的CSP 方法是一種重要的形式化協(xié)議分析驗(yàn)證方法。本文首先簡(jiǎn)單介紹了CSP 相關(guān)理論,并以NSPK 協(xié)議為例系統(tǒng)概述了安全協(xié)議的CSP 建模方法。為更好的查明協(xié)議的安全缺

2009-08-06 11:22:16 12

12 1.BGA 球柵陣列封裝 2.CSP 芯片縮放式封裝 3.COB 板上芯片貼裝 4.COC 瓷質(zhì)基板上芯片貼

2006-04-17 20:46:44 2648

2648 可以解決眾多封裝難題的CSP-ASIP

無(wú)線(xiàn)手持設(shè)備、掌上電腦以及其他移動(dòng)電子設(shè)備的增加導(dǎo)致了消費(fèi)者對(duì)各種小外形、特征豐富產(chǎn)品的需要。為了滿(mǎn)足越來(lái)越小的器件同時(shí)具有

2009-03-28 17:02:02 927

927 摘要:本文詳細(xì)討論了Maxim的晶片級(jí)封裝(WL-CSP),其中包括:晶圓架構(gòu)、卷帶包裝、PCB布局、安裝及回流焊等問(wèn)題。本文還按照IPC和JEDEC標(biāo)準(zhǔn)提供了可靠性測(cè)試數(shù)據(jù)。 注

2009-04-21 11:30:27 8552

8552

SMT最新技術(shù)之CSP及無(wú)鉛技術(shù)

CSP、0201無(wú)源元件、無(wú)鉛焊接和光電子,可以說(shuō)是近來(lái)許多公司在PCB上實(shí)踐和積極*價(jià)的熱門(mén)先進(jìn)技術(shù)。

2009-11-16 16:41:10 1405

1405 晶圓級(jí)CSP的返修工藝

經(jīng)底部填充的CSP裝配,其穩(wěn)健的機(jī)械連接強(qiáng)度得到很大的提升。在二級(jí)裝配中,由于底部填充,其抵御 由于

2009-11-20 15:42:17 483

483 晶圓級(jí)CSP的裝配工藝流程

目前有兩種典型的工藝流程,一種是考慮與其他元件的SMT配,首先是錫膏印刷,然后貼裝CSP,回流焊接

2009-11-20 15:44:59 1348

1348 CSP封裝內(nèi)存

CSP(Chip Scale Package),是芯片級(jí)封裝的意思。CSP封裝最新一代的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封裝可以讓芯片面積與封裝面積之比超

2009-12-25 14:24:49 636

636 高級(jí)封裝,高級(jí)封裝是什么意思

晶片級(jí)封裝CSP(Chip Scale Package)。幾年之前以上所有的封裝其封裝本體面積與芯片面積之比通常都是

2010-03-04 11:13:29 1420

1420 什么是CSP封裝

近幾年的硬件發(fā)展是日新月異,處理器已經(jīng)進(jìn)入G赫茲時(shí)代,封裝形式也是經(jīng)歷了數(shù)種變化。不過(guò),光有一顆速急力猛的芯還遠(yuǎn)遠(yuǎn)不夠

2010-03-04 11:43:25 14777

14777 半導(dǎo)體封裝類(lèi)型總匯(封裝圖示)

1.BGA 球柵陣列封裝 2.CSP 芯片縮放式封裝 3.COB 板上芯片貼裝 4.COC 瓷

2010-03-04 14:31:53 5659

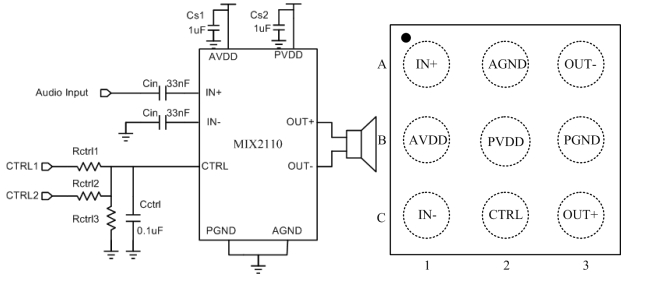

5659 上海矽諾微電子針對(duì)目前的便攜式市場(chǎng)推出全系列兼容的CSP-9封裝的D類(lèi)音頻功放。該系列產(chǎn)品目前有三顆,分別是MIX

2011-01-11 09:15:17 1444

1444

1996年,Lowe首先使用通信順序進(jìn)程CSP和模型檢測(cè)技術(shù)分析NSPK(Needham-Schroeder Public Key)協(xié)議,并成功發(fā)現(xiàn)了協(xié)議中的一個(gè)中間人攻擊行為。隨后,Roscoe對(duì)CSP和FDR(Fallures-Divergence Refinenent)的組合

2011-10-19 13:57:37 1134

1134

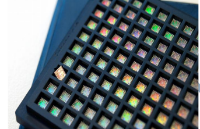

CSP封裝芯片的量產(chǎn)測(cè)試采用類(lèi)似晶圓測(cè)試的方法進(jìn)行,但是兩者的區(qū)別在于:晶圓的測(cè)試,探針是扎在管芯的PAD(通常情況下為鋁金屬)上,而CSP封裝的測(cè)試座,探針是扎到CSP封裝的錫

2012-05-02 10:00:40 1546

1546 sensor OV9750_CSP5_DS_1.0_King Horn Enterprise Ltd.

2016-02-25 11:34:09 78

78 OV2715_CSP3_Datasheet

2016-12-25 23:00:49 4

4 芯片級(jí)封裝介紹本應(yīng)用筆記提供指引使用與PCB安裝設(shè)備相關(guān)的芯片級(jí)封裝。包括系統(tǒng)的PCB布局信息制造業(yè)工程師和制造工藝工藝工程師。 包概述 倒裝芯片CSP的包概述半導(dǎo)體封裝提供的芯片級(jí)封裝代表最小

2017-03-31 10:57:32 45

45 超級(jí)CSP——讓倒裝芯片獲得最大可靠性一種晶圓片級(jí)封裝

2017-09-14 11:31:37 22

22 CSP LED一定是未來(lái)主流產(chǎn)品 那么CSPLED能否成為未來(lái)主流產(chǎn)品嗎?結(jié)論是肯定的,但必須緊緊圍繞CSPLED的特點(diǎn)去尋找CSPLED的性?xún)r(jià)比、用戶(hù)體驗(yàn)與附加價(jià)值,否則,在短時(shí)期內(nèi),CSPLED

2017-09-22 16:41:20 24

24 CSP封裝的芯片測(cè)試,由于其封裝較小,采用普通的機(jī)械手測(cè)試無(wú)法實(shí)現(xiàn),目前主要采用類(lèi)似晶圓測(cè)試的方法,在芯片完成置球封裝后,先不做劃片,而直接用探針卡進(jìn)行測(cè)試,測(cè)試完成后,再實(shí)行劃片、分選和包裝。

2017-10-27 15:11:10 7297

7297 模型檢測(cè)是通信順序進(jìn)程(communicatmg sequential processes,簡(jiǎn)稱(chēng)CSP)形式化驗(yàn)證的重要手段.當(dāng)前,CSP模型檢測(cè)方法基于操作語(yǔ)義,需將進(jìn)程轉(zhuǎn)化為遷移系統(tǒng),進(jìn)而

2018-01-23 16:03:53 1

1 CSP(chip scale package)封裝是指一種封裝自身的體積大小不超過(guò)芯片自身大小的20%的封裝技術(shù)(下一代技術(shù)為襯底級(jí)別封裝,其封裝大小與芯片相同)。為了達(dá)成這一目的,LED制造商

2018-06-07 15:40:00 945

945

近幾年大陸背光產(chǎn)品價(jià)格持續(xù)下滑,億光等LED廠商在背光市場(chǎng)出貨比重仍不低,為避開(kāi)陸廠價(jià)格競(jìng)爭(zhēng),今年億光將以mini LED、CSP封裝產(chǎn)品搶攻高端背光應(yīng)用。

2018-04-27 11:20:00 2560

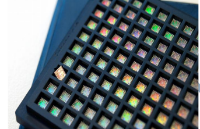

2560 目前CSP LED的主流結(jié)構(gòu)可分為有基板和無(wú)基板,也可分為五面發(fā)光與單面發(fā)光。所說(shuō)的基板自然可以視為一種支架。很顯然,為了滿(mǎn)足CSP對(duì)封裝尺寸的要求,傳統(tǒng)的支架,如2835,的確不能使用,但并不

2018-07-12 14:34:00 10628

10628 針對(duì)CSP技術(shù)難題,海迪科經(jīng)過(guò)技術(shù)團(tuán)隊(duì)的刻苦攻關(guān)之后,成功研發(fā)并推出了一款新型光源WLCSP,從而實(shí)現(xiàn)了CSP技術(shù)的大幅升級(jí)。

2018-07-17 14:21:20 4146

4146 CSP(Chip Scale Package)封裝,是芯片級(jí)封裝的意思。CSP封裝最新一代的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封CSP封裝裝可以讓芯片面積與封裝面積之比超過(guò)

2018-08-17 15:25:38 18203

18203 CSP(chip scale package)封裝是指一種封裝自身的體積大小不超過(guò)芯片自身大小的20%的封裝技(下一代技術(shù)為襯底級(jí)別封裝,其封裝大小與芯片相同)。

2018-09-05 08:36:00 13375

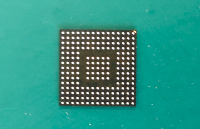

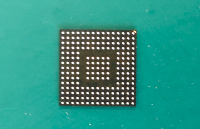

13375 CSP封裝是一種芯片級(jí)封裝,我們都知道芯片基本上都是以小型化著稱(chēng),因此CSP封裝最新一代的內(nèi)存芯片封裝技術(shù),可以讓芯片面積與封裝面積之比超過(guò)1:1.14,已經(jīng)相當(dāng)接近1:1的理想情況,被行業(yè)界評(píng)為單芯片的最高形式,與BGA封裝相比,同等空間下CSP封裝可以將存儲(chǔ)容量提高三倍。

2019-03-07 15:41:08 12386

12386 CSP封裝是最新一代的內(nèi)存芯片封裝技術(shù),其技術(shù)性能又有了新的提升。CSP封裝可以讓芯片面積與封裝面積之比超過(guò)1:1.14,已經(jīng)相當(dāng)接近1:1的理想情況,絕對(duì)尺寸也僅有32平方毫米,約為普通的BGA的1/3,僅僅相當(dāng)于TSOP內(nèi)存芯片面積的1/6。與BGA封裝相比,同等空間下CSP封裝可以將存儲(chǔ)容量提高三倍。

2019-06-24 14:12:36 19779

19779 電子發(fā)燒友網(wǎng)為你提供TE(ti)CAT-CSP-5T相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有CAT-CSP-5T的引腳圖、接線(xiàn)圖、封裝手冊(cè)、中文資料、英文資料,CAT-CSP-5T真值表,CAT-CSP-5T管腳等資料,希望可以幫助到廣大的電子工程師們。

2021-07-08 21:00:04

隨著集成電路的廣泛應(yīng)用,集成度越來(lái)越高,在BGA技術(shù)開(kāi)始推廣的同時(shí),另外一種從BGA發(fā)展來(lái)的CSP封裝技術(shù)正在逐漸展現(xiàn)它的生力軍本色。作為新一代的芯片封裝技術(shù),CSP封裝可以讓芯片面積與封裝面積之比

2021-12-03 13:58:36 2405

2405 先進(jìn)封裝形式μBGA、CSP的回流焊接技術(shù)介紹說(shuō)明。

2022-05-06 15:17:46 4

4 ./oschina_soft/CSP-Validator.zip

2022-05-19 09:41:58 2

2 倒裝芯片 CSP 封裝

2022-11-14 21:07:58 19

19 CSP封裝(Chip Scale Package)是指芯片級(jí)封裝,其封裝尺寸和芯片核心尺寸基本相同,一般芯片面積與封裝面積的比例約在1:1.1。CSP封裝最先規(guī)模應(yīng)用在消費(fèi)電子和個(gè)人電腦,與我們的生活息息相關(guān)。

2023-03-28 14:52:09 10625

10625 CSP2510C 數(shù)據(jù)表

2023-04-26 19:29:44 1

1 CSP(Chip Scale Package)封裝芯片是一種高密度、小尺寸的封裝形式,它在集成電路行業(yè)中具有廣泛的應(yīng)用。對(duì)于CSP封裝芯片的測(cè)試方法而言,主要涉及到以下幾個(gè)方面:

2023-06-03 10:58:16 1142

1142 隨著芯片集成度的不斷提高,芯片封裝密度也在不斷增加,這給芯片散熱帶來(lái)了巨大的挑戰(zhàn)。高溫會(huì)導(dǎo)致芯片性能下降,甚至?xí)斐尚酒瑩p壞。因此,解決芯片封裝散熱問(wèn)題是一項(xiàng)至關(guān)重要的任務(wù)。

2023-06-04 14:33:00 4291

4291 今天我們來(lái)介紹PLCSP(Panel Level Chip Scale Packaging)。同理,PLCSP是一種將面板級(jí)封裝(PLP)和芯片尺寸封裝(CSP)合為一體的封裝技術(shù)。芯片尺寸封裝(CSP)是指整個(gè)package的面積相比于silicon總面積不超過(guò)120%的封裝技術(shù)。

2023-06-19 11:31:46 867

867

光電傳感器WL-CSP封裝芯片底部填充膠應(yīng)用由漢思新材料提供光電傳感器芯片(CCD)經(jīng)過(guò)聯(lián)系客戶(hù)工程技術(shù)和研究其提供的封裝工藝流程。了解到以下信息。客戶(hù)用膠項(xiàng)目是:光電傳感器芯片(CCD

2023-05-18 05:00:00 546

546

電子封裝是現(xiàn)代電子產(chǎn)品中不可或缺的一部分,它將電子元件組裝在一起,形成了一個(gè)完整的電子系統(tǒng)。其中,BGA和CSP是兩種常見(jiàn)的電子封裝技術(shù),它們各有優(yōu)缺點(diǎn),廣泛應(yīng)用于半導(dǎo)體制造、LCD顯示器等領(lǐng)域

2023-06-14 09:11:18 850

850

芯片封裝的發(fā)展歷程可以總結(jié)為七種類(lèi)型:TO→DIP→SOP→QFP→PLCC→BGA→CSP。

2023-07-20 14:33:20 838

838 短1/5~1/6左右,同時(shí)CSP的抗噪能力強(qiáng),開(kāi)關(guān)噪聲只有DIP(雙列直插式封裝)的1/2。這些主要電學(xué)性能指標(biāo)已經(jīng)接近裸芯片的水平,在時(shí)鐘頻率己超過(guò)雙G的高速通信領(lǐng)域,LSI芯片的CSP將是十分理想的選擇。

2023-08-20 09:42:07 1110

1110

CSP是近幾年才出現(xiàn)的一種集成電路的封裝形式,目前已有上百種CSP產(chǎn)品,并且還在不斷出現(xiàn)一些新的品種。盡管如此,CSP技術(shù)還是處于發(fā)展的初期階段,因此還沒(méi)有形成統(tǒng)一的標(biāo)準(zhǔn)。不同的廠家生產(chǎn)不同的CSP

2023-09-08 14:09:40 294

294 BGA和CSP封裝技術(shù)詳解

2023-09-20 09:20:14 951

951

焊盤(pán)整理完成之后就可以重新貼裝元件了。這時(shí)我們又面臨了新的問(wèn)題:如果選擇錫膏裝配的話(huà),如何印刷錫膏呢?對(duì)于密間距的晶圓級(jí)CSP來(lái)說(shuō),這的確是一個(gè)難題。

2023-09-28 15:45:12 660

660 簡(jiǎn)要解讀BGA、CSP封裝中的球窩缺陷

2023-10-08 08:47:53 339

339

CSP的高效優(yōu)點(diǎn)體現(xiàn)在:用于板級(jí)組裝時(shí),能夠跨出細(xì)間距(細(xì)至0.075mm)周邊封裝的界限,進(jìn)入較大間距(1,0.8,0.75,0.5,0.4mm)區(qū)域陣列結(jié)構(gòu)。 已有許多CSP器件在消費(fèi)類(lèi)電信領(lǐng)域

2023-10-17 14:58:21 321

321 如何解決汽車(chē)大功率集成磁元件的散熱難題?

2023-11-29 11:57:07 212

212

為了實(shí)現(xiàn)集成電路芯片的電通路,一般需要將芯片裝配到在塑料或陶瓷載體上,這一過(guò)程可以稱(chēng)為CSP。CSP的尺寸只是略大于芯片,通常封裝尺寸不大于芯片面積的1.5倍或不大于芯片寬度或長(zhǎng)度的?1.2

2023-12-22 09:08:31 535

535

提及CSP封裝基板領(lǐng)域,興森科技目前每月的產(chǎn)量約為3.5萬(wàn)平方米,其中廣州基地生產(chǎn)能力達(dá)到了2萬(wàn)平方米/月,已處于飽和狀態(tài);而廣州興科與珠海基地的產(chǎn)能分別為1.5萬(wàn)平方米/月,且利用率都超過(guò)了50%。

2024-01-30 09:59:33 260

260 立錡推出的低壓輸入、CSP 小封裝降壓轉(zhuǎn)換器系列,不僅滿(mǎn)足各式小型穿戴式和 IoT 物聯(lián)網(wǎng)應(yīng)用的需求,更在性能和尺寸上取得了絕佳平衡。

2024-03-14 15:03:10 192

192

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論