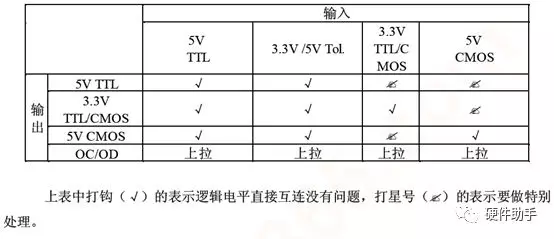

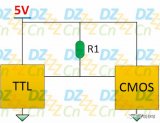

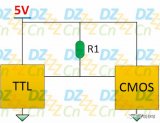

在 同樣5V電源電壓情況下,COMS電路可以直接驅(qū)動TTL,因?yàn)?b class="flag-6" style="color: red">CMOS的輸出高電平大于2.0V,輸出低電平小于0.8V。

2017-09-20 10:04:53 31370

31370

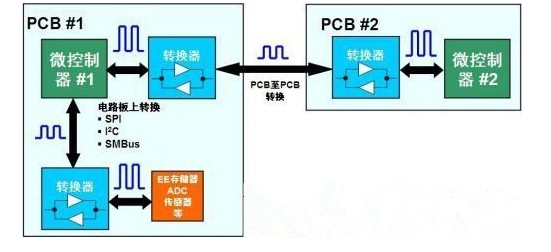

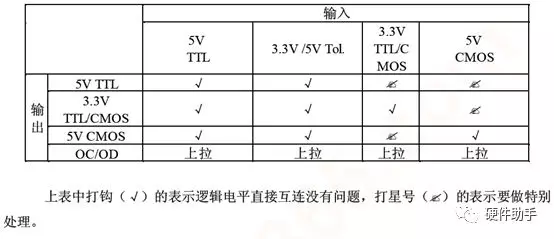

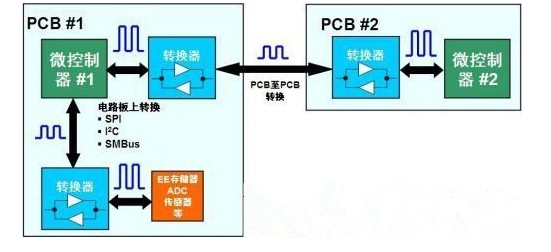

本篇主要介紹TTL/CMOS電平的互連、OC/OD的互連,其余單端邏輯電平的互連可參考相關(guān)器件規(guī)范、電平規(guī)范。 1、TTL/CMOS互連 常用的TTL和CMOS電平主要是5V TTL、5V CMOS

2020-12-23 14:15:12 5648

5648

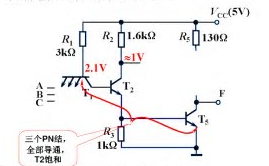

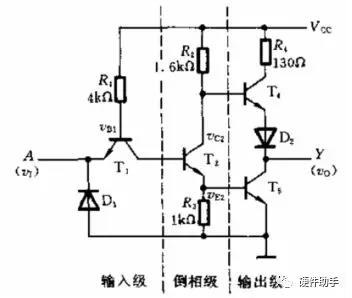

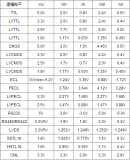

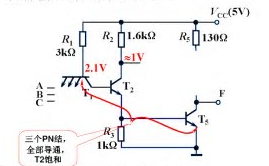

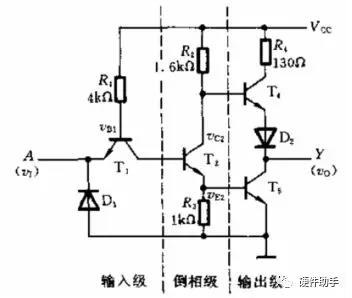

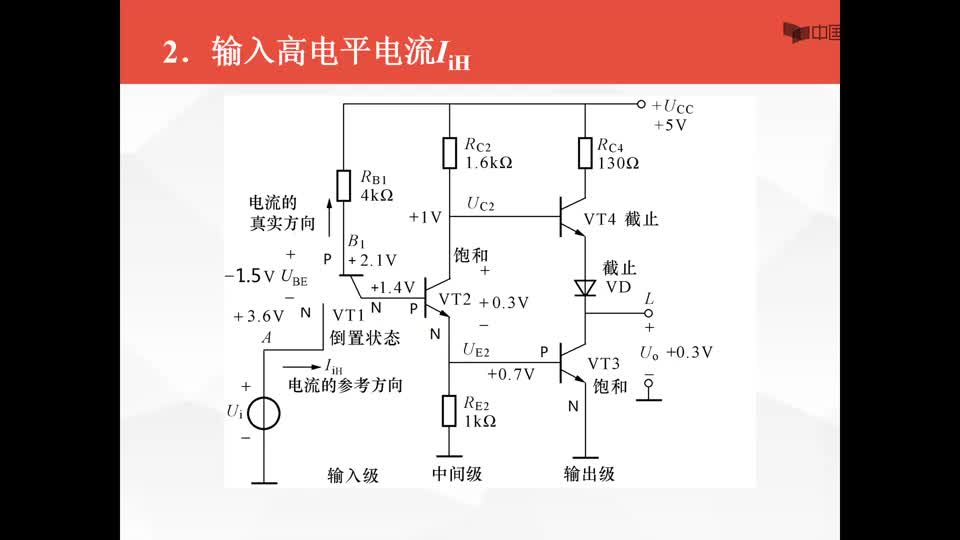

本篇主要介紹常用的單端邏輯電平,包括TTL、CMOS、SSTL、HSTL、POD12等。 1、TTL電平 ? ? ? 下面以一個三輸入的TTL與非門介紹TTL電平的原理。 ? ? ? 三輸入TTL

2020-12-24 13:05:29 33383

33383

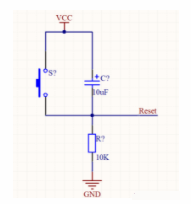

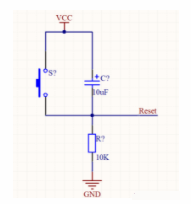

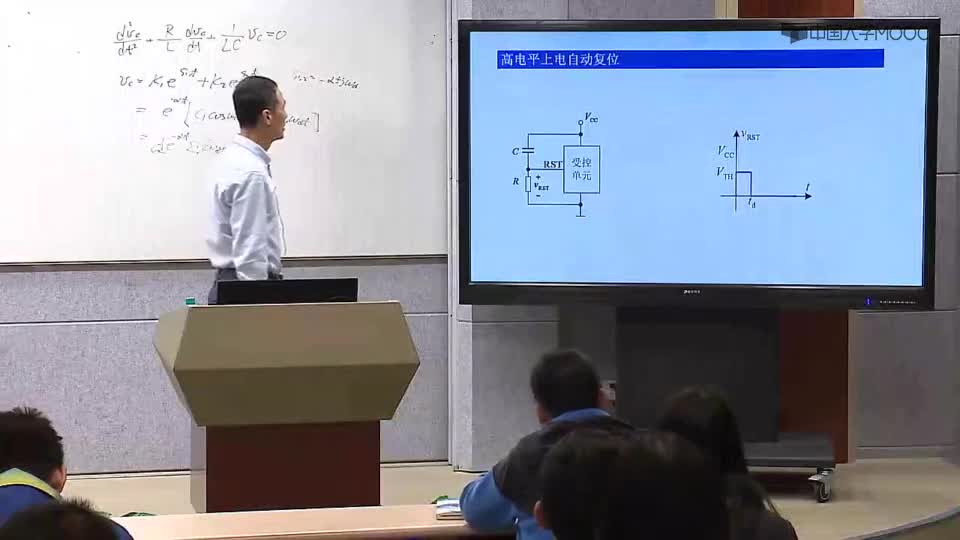

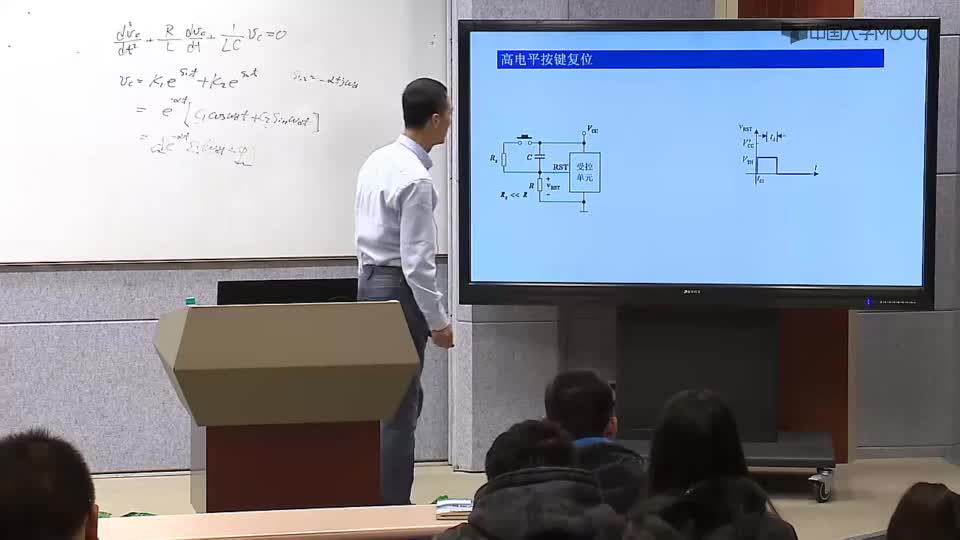

單片機(jī)復(fù)位電路分為兩種類型:低電平復(fù)位和高電平復(fù)位。

2022-08-05 15:45:28 20918

20918

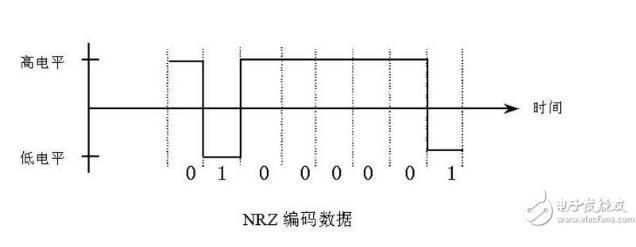

高電平和低電平是數(shù)字電路中經(jīng)常會出現(xiàn)的專業(yè)名詞,它們所表面的意思就是電路上有和無,兩者之間沒有中間值,在不同的電路上,電壓的具體值也是各不相同的。如果用簡單的語言表達(dá)它們的意思就是開和關(guān),平時

2023-05-26 10:17:30 24069

24069

單端邏輯電平的匹配是我們平時在硬件設(shè)計中最經(jīng)常碰到的,我們在《TTL&CMOS電平》章節(jié)中已經(jīng)對TTL和COMS電平的匹配設(shè)計做了一些分析,一般3.3V LVTTL和LVCMOS是可以直接相互驅(qū)動的。但是其它不同邏輯電平之間呢?舉個栗子,3.3V邏輯電平和1.8V邏輯電平之間呢?

2023-06-25 14:52:24 1384

1384

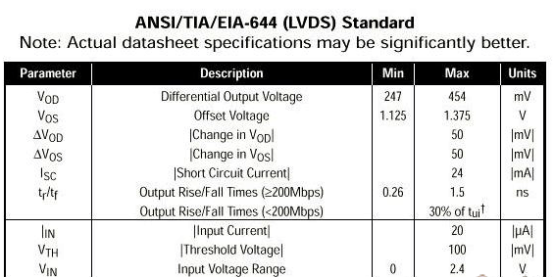

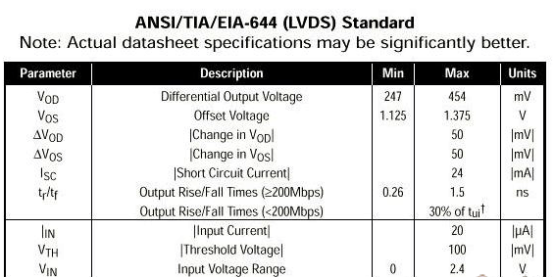

LVDS電平是根據(jù)ANSI/EIA/TIA-644定義的一種電平標(biāo)準(zhǔn),其標(biāo)準(zhǔn)定義的相關(guān)參數(shù)如下。

2023-09-20 15:29:58 822

822

CMOS電平和TTL電平對比分析為什么引入OC門?什么是OC、OD?

2021-04-20 06:53:21

1.TTL電平: 輸出高電平>2.4V,輸出低電平=2.0V,輸入低電平

2016-09-23 14:11:11

1.TTL電平: 輸出高電平>2.4V,輸出低電平=2.0V,輸入低電平

2016-09-25 10:13:14

CMOS和TTL通過電阻接電源,要如何判斷接入高電平還是低電平?

2023-04-25 09:27:35

STM8的引腳要怎么才能輸出CMOS電平

2023-10-11 08:20:58

什么是TTL電平,什么是CMOS電平,他們的區(qū)別(一)TTL高電平3.6~5V,低電平0V~2.4V CMOS電平Vcc可達(dá)到12V ...

2022-01-25 06:19:09

指示出什么顏色代表什么區(qū)域,謝謝了!舉例,VIHX線往上方邊界Vcc看,中間包含的藍(lán)色和條紋帶都能被認(rèn)為是高電平。是可靠電平。左邊2個是ttl邏輯電路不同供電電壓時情況;右邊2個是cmos邏輯電路

2008-07-21 10:22:44

“TTL電平”最常用于有關(guān)電專業(yè),如:電路、數(shù)字電路、微機(jī)原理與接口技術(shù)、單片機(jī)等課程中都有所涉及。在數(shù)字電路中只有兩種電平(高和低)高電平+5V、低電平0V。同樣運(yùn)用比較廣泛的還有CMOS電平

2018-01-17 14:52:47

TTL與CMOS電平詳解超級有用

2014-03-12 00:03:46

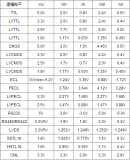

的平臺,給老司機(jī)交流的平臺。所有文章來源于項(xiàng)目實(shí)戰(zhàn),屬于原創(chuàng)。一、電平規(guī)范1、名稱解釋Uoh -> 輸出高電平,Uol -> 輸出低電平;Uih -> 輸入高電平,Uil -&g...

2022-01-25 07:56:18

,輸出在0.5V以下為低電平,輸入在2V以上為高電平,在0.8V以下為低電平。因此,CMOS電路與TTL電路就有一個電平轉(zhuǎn)換的問題,使兩者電平域值能匹配TTL電平與CMOS電平的區(qū)別:(一)TTL高電平

2016-09-27 16:26:31

什么是TTL電平?什么是CMOS電平?開漏形式的電路有什么特點(diǎn)?

2021-09-28 07:56:38

高電平低電平主要應(yīng)用于數(shù)字電路。體現(xiàn)在電路上就是只有‘有’和‘無’,沒有中間值,這個有在不同電路上的電壓值不相同。如果是5V供電的數(shù)字電路,高電平就是5V,或接近5V。低電平就是‘無’,就是0V或

2018-08-28 14:59:04

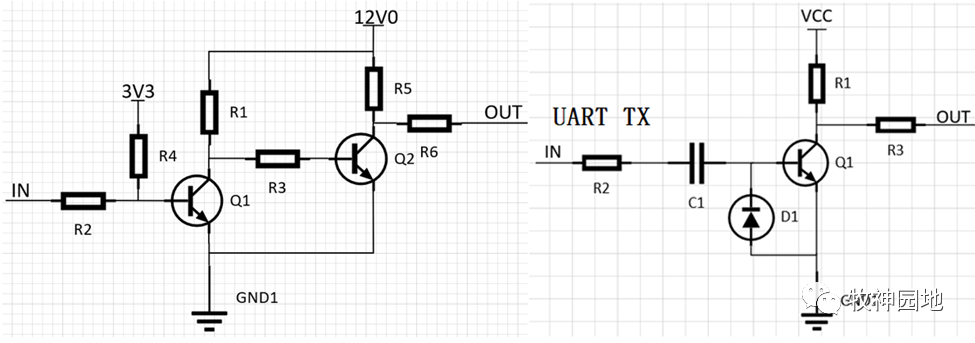

今天買個繼電器,買錯了,想要高電平出發(fā),結(jié)果整個低電平出發(fā),用什么方法能改成高電平觸發(fā)的啊,如果可以多給幾種方法,我手頭材料不算多

2015-11-04 17:38:42

硬件研發(fā)工程師設(shè)計時肯定離不開電平這個概念,目前有多種電平定義,今天我就常用的電平做了下總結(jié),和大家分享下現(xiàn)在常用的電平標(biāo)準(zhǔn)有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL

2011-05-11 08:02:01

看TTP224B手冊的時候看到這樣一句話。直接輸出模式, CMOS 輸出低電平有效到底是指低電平時才能有效輸出,還是指輸出端輸出低電平?

2020-10-18 15:39:26

設(shè)置P2.3口為低電平,若P2.3變?yōu)?b class="flag-6" style="color: red">高電平,P2.7輸出低電平,否則仍未高電平這個代碼寫的有問題嗎??void sh_gongzuo(){sh_in=0;if(sh_in==1)sh_out=0;else sh_out=1;}定義過***it sh_in=P2^3;***it sh_out=P2^7;

2015-05-24 15:57:35

我想實(shí)現(xiàn)2.2V的非標(biāo)準(zhǔn)ttl電平轉(zhuǎn)3.3V的cmos電平,請問有什么合適的電平轉(zhuǎn)換器或者是電壓比較器推薦嗎?

2024-03-11 09:30:08

,輸出電壓低于VSS+0.5V(VSS為數(shù)字地)為邏輯 0。CMOS電路輸出高電平約為 0.9Vcc,而輸出低電平約為 0.1Vcc.當(dāng)輸入電壓高于VDD-1.5V時為邏輯 1,輸入電壓

2019-03-22 07:00:00

CMOS電平和TTL電平的區(qū)別

2021-04-06 09:52:03

當(dāng)Vccio=3. 3V時, 對于輸入腳, 它兼容TTL, CMOS電平;對輸出腳, 它是否也兼容TTL和CMOS電平?對CMOS電平, 是否需要用OpenDrain 加上下拉電阻來實(shí)現(xiàn)?

2019-09-03 05:55:08

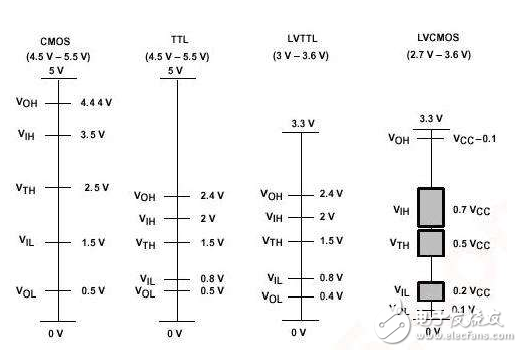

是從5V CMOS邏輯電平關(guān)注移植過來的,所以它的Vih、Vil和Voh、Vol與工作電壓有關(guān),其值如上圖所示。LVCMOS邏輯電平定義的工作電壓范圍是2.7-3.6V。 5V的CMOS邏輯器件工作于

2009-04-12 12:03:33

。LVCMOS邏輯電平標(biāo)準(zhǔn)是從5V CMOS邏輯電平關(guān)注移植過來的,所以它的Vih、Vil和Voh、Vol與工作電壓有關(guān),其值如上圖所示。LVCMOS邏輯電平定義的工作電壓范圍是2.7-3.6V。5V

2008-06-24 09:38:52

TTL電平與CMOS電平的區(qū)別

1,TTL電平:

輸出高電平>2.4V,輸出低電平<0.4V。在室溫下,一般輸出高電平是3.5V,輸出低電

2007-10-10 12:26:19 8208

8208 TTL電平 CMOS電平推挽輸出

TTL——Transistor-Transistor Logic HTTL——High-speed TTL LTTL——Low-power TTL STTL——Schottky TTL LSTTL——Low-power Schottky TTL

2007-12-05 09:35:31 2803

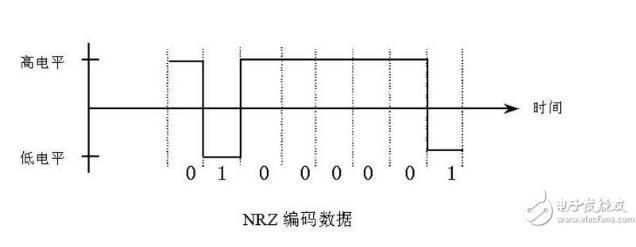

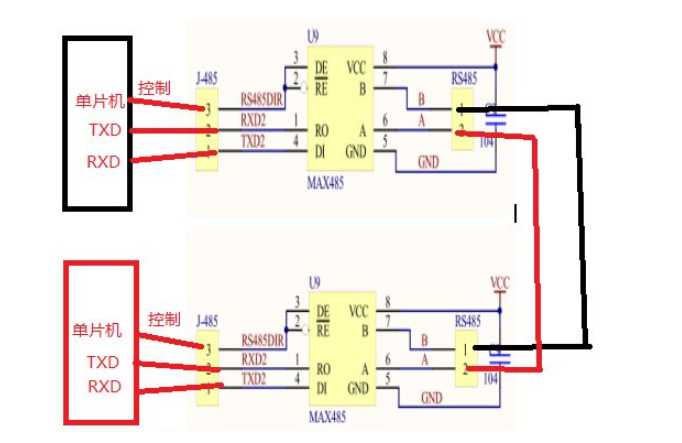

2803 電平標(biāo)準(zhǔn):現(xiàn)在常用的電平標(biāo)準(zhǔn)有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,還有一些速

2008-07-21 10:25:08 2699

2699 邏輯電平詳細(xì)介紹邏輯電平有:TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、GTL、BTL、ETL、GTLP;RS232、RS422、RS485等。 常用邏輯系列器件 TTL:Transistor-Transistor Logic CMOS:Compl

2009-04-12 12:03:16 10896

10896

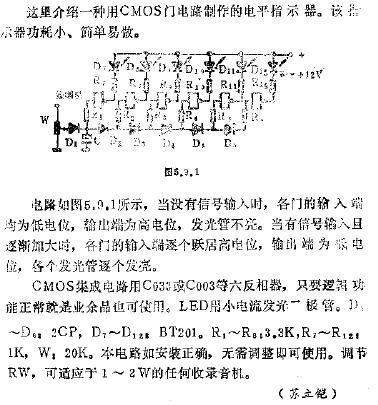

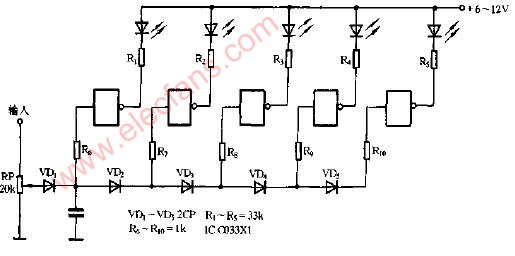

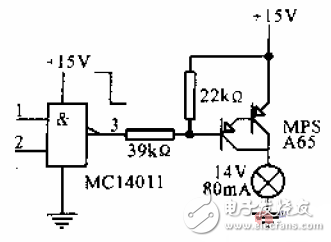

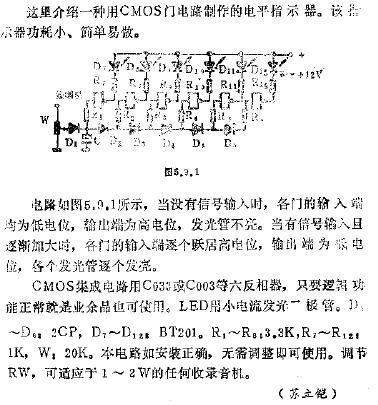

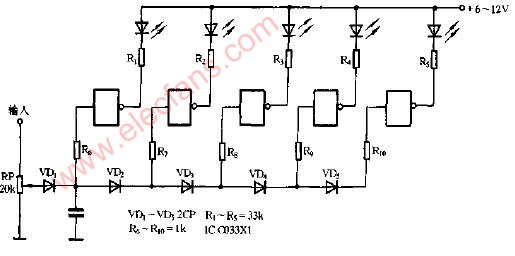

用CMOS集成電路制作的電平指示器

2009-04-20 11:37:05 646

646

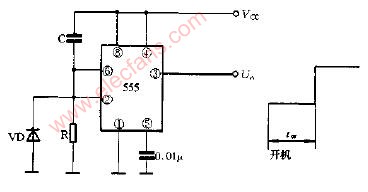

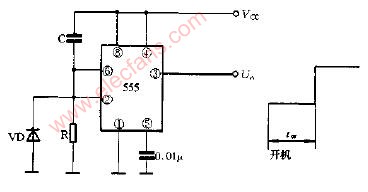

開機(jī)延時輸出高電平電路圖

2009-05-08 14:55:42 2001

2001

CMOS集成電路電平指示電路圖

2009-05-08 15:57:02 814

814

TTL和CMOS電平基礎(chǔ)知識

TTL電平: 輸出高電平 > 2.4V 輸出低電平 <

2009-11-28 11:28:33 1282

1282 車載功放的高電平輸入 高電平輸入是指車載功放可以直接從車載主機(jī)接收原本輸出至車載揚(yáng)聲器的信

2010-01-04 11:11:59 7204

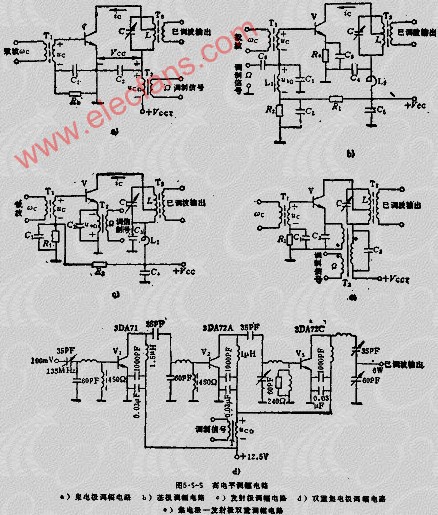

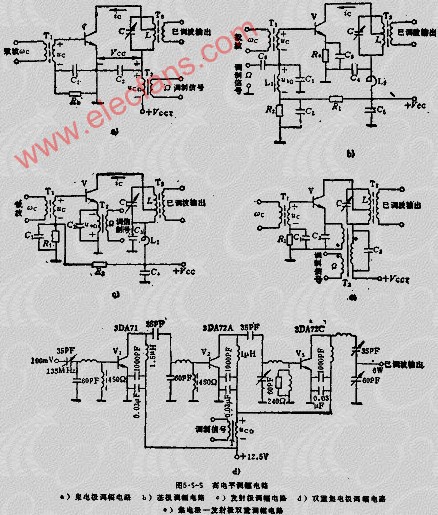

7204 調(diào)幅電路工作原理--高電平調(diào)幅電路

調(diào)幅的方法按電平的高低可區(qū)分為高電平調(diào)制和低電平調(diào)制,前者是直接產(chǎn)生滿足發(fā)射機(jī)輸出功率要

2010-05-25 15:50:49 15287

15287

CMOS 電路是電壓控制器件,輸入電阻極大,對于干擾信號十分敏感,因此不用的輸入端不應(yīng)開路,接到地或者電源上。 CMOS 電路的優(yōu)點(diǎn)是噪聲容限較寬,靜態(tài)功耗很小。TTL 電平輸出高電

2011-08-08 16:02:01 181

181 在電路設(shè)計時,最容易忽視也最容易造成錯誤的問題,詳細(xì)介紹TTL電平和CMO電平之間怎么轉(zhuǎn)換

2016-01-13 10:23:26 7

7 高電平輸出光控電路原理圖都是值得參考的設(shè)計。

2016-05-11 17:00:47 26

26 數(shù)字信號才是0和1 。凡是輸入與 5V TTL 電平兼容的 5V CMOS 器件都可以用作 3.3V→5V 電平轉(zhuǎn)換,這是由于 3.3V CMOS 的電平剛好和5V TTL電平兼容(巧合),而 CMOS 的輸出電平總是接近電源電平的。

2017-08-26 16:52:00 8382

8382

1、CMOS電平標(biāo)準(zhǔn)

輸出 L: 《0.1*Vcc ; H:》0.9*Vcc。

輸入 L: 《0.3*Vcc ; H:》0.7*Vcc.

由于CMOS電源采用12V,則輸入低于3.6V為低電平

2017-08-26 17:08:00 15479

15479

UolUoh2.4V,Uol0.4V 2.輸入高電平和輸入低電平Uih2.0V,Uil0.8V 二.CMOS CMOS電路是電壓控制器件,輸入電阻極大,對于干擾信號十分敏感,因此不用的輸入端不應(yīng)開路,接到

2017-11-08 12:59:13 0

0 數(shù)字電路中,把電壓的高低用邏輯電平來表示。邏輯電平包括高電平和低電平這兩種。不同的元器件形成的數(shù)字電路,電壓對應(yīng)的邏輯電平也不同。在TTL門電路中,把大于3.5伏的電壓規(guī)定為邏輯高電平,用數(shù)字1表示

2017-11-14 10:37:26 291204

291204

TTL電平最常用于有關(guān)電專業(yè),如:電路、數(shù)字電路、微機(jī)原理與接口技術(shù)、單片機(jī)等課程中都有所涉及。在數(shù)字電路中只有兩種電平(高和低)高電平+5V、低電平0V.同樣運(yùn)用比較廣泛的還有CMOS電平、232

2017-11-15 14:34:49 6

6 ,其引腳基本上是CMOS結(jié)構(gòu),因此輸入電壓范圍是:高電平不低于0.7VCC,低電平不高于0.3VCC。 但在介紹電平轉(zhuǎn)換電路之前,我們需要先來了解以下幾點(diǎn): 1.解決電平轉(zhuǎn)換問題,最根本的就是要解決電平的兼容問題,而電平兼容原則有兩條:①VOH》VIH ②VO

2017-11-28 10:14:40 18

18 輸入高電平門限Vih:保證邏輯門的輸入為高電平時所允許的最小輸入高電平,當(dāng)輸入電平高于Vih時,則認(rèn)為輸入電平為高電平;

2018-03-10 09:47:49 12458

12458

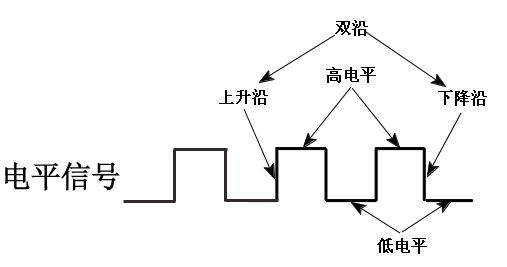

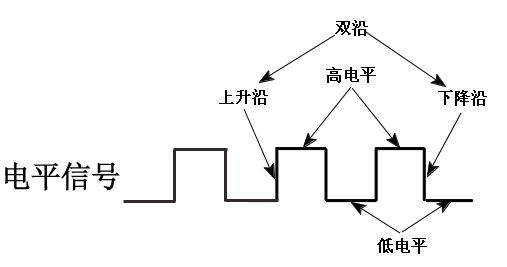

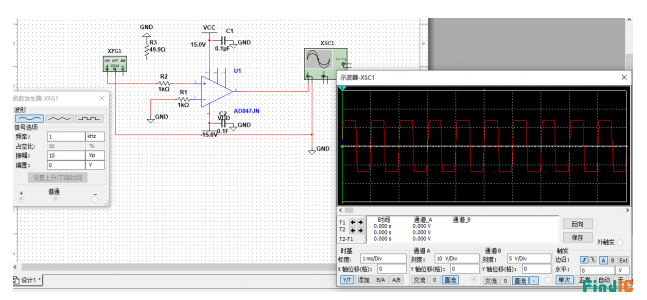

本文開始闡述了電平信號什么意思以及電平信號的產(chǎn)生,其次對TTL電平的相關(guān)定義進(jìn)行了介紹,最后闡述了電平信號和脈沖信號區(qū)別以及闡述了電平和電壓的區(qū)別。

2018-03-13 10:02:07 67340

67340

TTL、CMOS電平和OC門知識大全

2018-07-15 10:33:00 7563

7563 LS、HC 二者高電平低電平定義不同,HC高電平規(guī)定為0.7倍電源電壓,低電平規(guī)定為0.3倍電源電壓。

2018-08-02 16:52:25 74783

74783 (AHCT與TTL電平兼容)

FCT——FACT擴(kuò)展系列,與TTL電平兼容

FACT——Fairchild Advanced CMOS Technology,其

?

1,TTL電平:

???輸出高電平>2.4V,輸出低電平=2.0V,輸入低電平

2018-09-20 18:26:45 8039

8039 CMOS電平:CMOS電路輸出高電平為3V~12V,低電平輸出接近0V 計算機(jī)的MAX232電平:高電平為-5V到-12V,低電平為+5V到+12V,為負(fù)電壓電平

2019-09-09 17:26:00 2

2 晶體管組成了TTL集成電路,TTL大多采用5V電路。用二進(jìn)制來進(jìn)行表示的話, 5V正好等于邏輯上的“1”, 0V等于邏輯上的“0”,因此, TTL電平在電路中得以被大星應(yīng)用。而在此領(lǐng)域中,同樣被大量應(yīng)用的還有CMOS電平。除了邏輯電平范圍的不同,TTL電平和CMOS電平之間還有哪些不同呢?

2019-08-19 14:20:23 28450

28450 1.CMOS電平:

‘1’邏輯電平電壓接近于電源電壓,‘0’邏輯電平接近于0V。噪聲容限很大

2.TTL電平:

輸出高電平》2.4V,輸出低電平《0.4V。在室溫下,一般輸出高電平是3.5V

2019-09-14 10:52:00 5428

5428

本文檔的主要內(nèi)容詳細(xì)介紹的是TTL和CMOS電平的區(qū)別詳細(xì)資料說明。

2020-06-05 17:10:31 27

27 在門電路輸入端串聯(lián)10K電阻后再輸入低電平,輸入端出呈現(xiàn)的是高電平而不是低電平。因?yàn)橛蒚TL門電路的輸入端負(fù)載特性可知,只有在輸入端接的串聯(lián)電阻小于910歐時,它輸入來的低電平信號才能被門電路識別出來,串聯(lián)電阻再大的話輸入端就一直呈現(xiàn)高電平。這個一定要注意。COMS門電路就不用考慮這些了。

2020-08-05 10:41:30 17100

17100

由于晶體管-晶體管邏輯(TTL)和互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)是邏輯電路中的標(biāo)準(zhǔn)電平,因傳統(tǒng)邏輯電平轉(zhuǎn)換方法中,TTL-CMOS輸入轉(zhuǎn)換很常見。這種轉(zhuǎn)換方法簡單,成本低,主要用于低電平至高電平

2020-08-12 16:16:57 2486

2486

由于實(shí)現(xiàn)方式簡單,CMOS電平時鐘被廣泛使用(通常頻率在200MHz以內(nèi))。但實(shí)際應(yīng)用中由于電源軌的限制經(jīng)常需要將CMOS信號的電平進(jìn)行轉(zhuǎn)化,比方將3.3V轉(zhuǎn)換成1.8V,或1.8V轉(zhuǎn)換成1.2V。在此給出一種簡單的轉(zhuǎn)換電路和計算。

2020-09-08 09:41:29 3809

3809

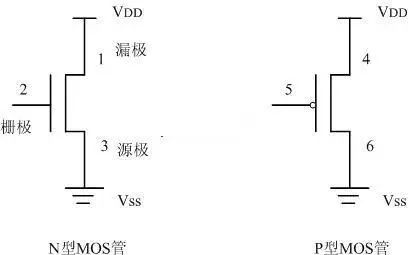

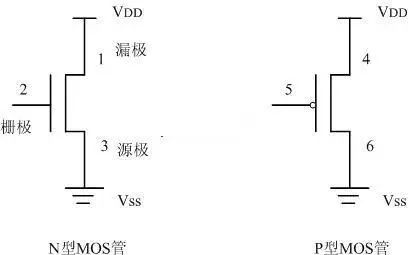

,1端接正電壓,稱為“漏極”,漏極電壓記作VDD。要使1端與3端導(dǎo)通,柵極2上要加高電平。 對P型管,柵極、源極、漏極分別為5端、4端、6端。要使4端與6端導(dǎo)通,柵極5要加低電平。 在CMOS工藝制成的邏輯器件或單片機(jī)中,N型管與P型管往往是成對出現(xiàn)的。同時出現(xiàn)的這兩個

2021-01-02 15:17:00 3621

3621

本篇主要介紹TTL/CMOS電平的互連、OC/OD的互連,其余單端邏輯電平的互連可參考相關(guān)器件規(guī)范、電平規(guī)范。

2021-01-06 17:40:22 20

20 邏輯輸出的高電平最小值VOHMIN(2.4V)卻低于CMOS邏輯輸入高電平的最小值VIHMIN(0.7×VCC=3.5V),換言之,CMOS邏輯可能不能夠識別TTL邏輯高電平(注意“可能”這兩個字)。

2021-01-20 17:14:12 4885

4885

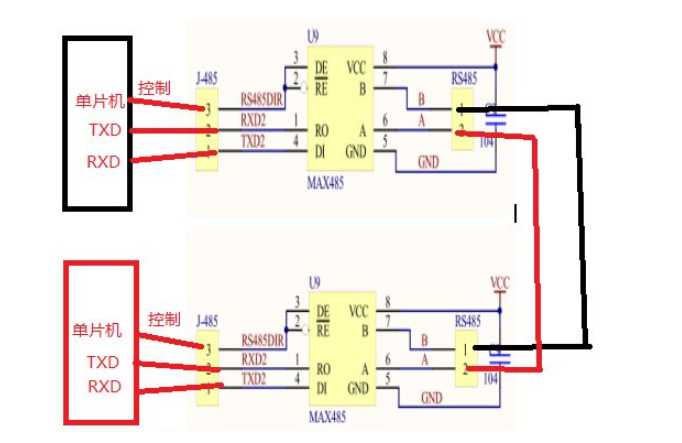

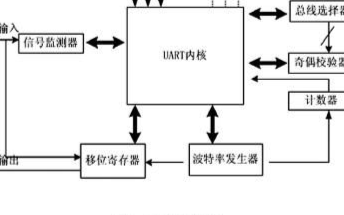

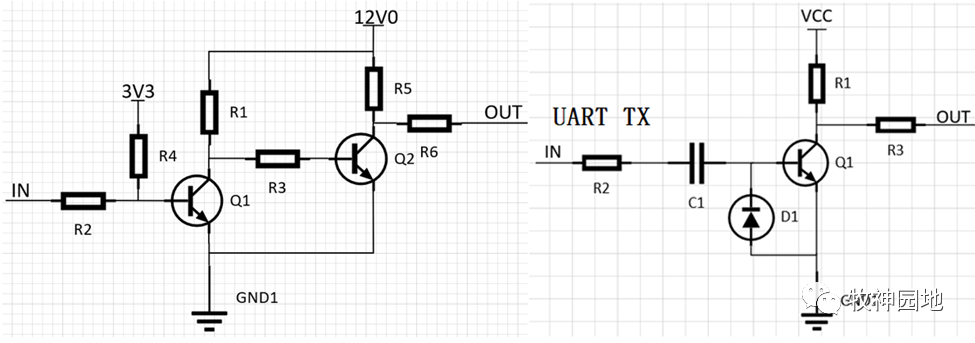

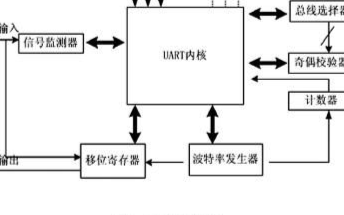

實(shí)現(xiàn)RS-232電平和TTL/CMOS電平轉(zhuǎn)換可以用接口芯片來實(shí)現(xiàn),實(shí)現(xiàn)數(shù)據(jù)的串行到并行轉(zhuǎn)換用的是UART,它們是實(shí)現(xiàn)串行通信必不可少的兩個部分。

2021-03-26 14:19:59 3767

3767

電子發(fā)燒友網(wǎng)為你提供什么是TTL電平、CMOS電平?都有哪些區(qū)別?資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-29 08:41:19 21

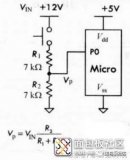

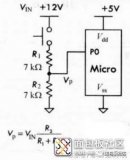

21 可靠的邏輯高電平I/O電路(輸入) 微控制器I/O端口線能承受的最大電壓不超過5V(不同微控制器有所區(qū)別),否則有可能燒壞I/O端口。本電路中,即使使用較大的電源電壓,分壓網(wǎng)絡(luò)也會送一個安全的(5V

2021-08-16 14:52:33 6469

6469

TTL,CMOS都屬于數(shù)字電路。TTL電流控制器件輸出高電平>2.4V輸出低電平<0.4VCMOS電壓控制器件輸出高電平>2.4V輸出低電平<0.4V

2021-11-26 18:51:08 10

10 的平臺,給老司機(jī)交流的平臺。所有文章來源于項(xiàng)目實(shí)戰(zhàn),屬于原創(chuàng)。一、電平規(guī)范1、名稱解釋Uoh -> 輸出高電平,Uol -> 輸出低電平;Uih -> 輸入高電平,Uil -&g...

2021-11-30 20:21:12 6

6 什么是TTL電平,什么是CMOS電平,他們的區(qū)別

2021-11-30 20:51:06 39

39 初學(xué)51單片機(jī),可能不太理解復(fù)位電路,復(fù)位電路有高電平和低電平兩種,C51是高電平復(fù)位,現(xiàn)在一般的MCU都是低電平復(fù)位。

2021-12-08 11:51:04 15

15 電平轉(zhuǎn)換也可以叫電壓轉(zhuǎn)換,它可以解決器件接口中的電平兼容問題。

2022-02-02 17:59:00 1720

1720 單片機(jī)最小系統(tǒng),即單片機(jī)能正常工作的最簡單的電路。復(fù)位電路是單片機(jī)最小系統(tǒng)的組成部分之一。對于不同單片機(jī),復(fù)位方式有高電平復(fù)位和低電平復(fù)位,從而相對應(yīng)地就有兩種復(fù)位電路,高電平和低電平復(fù)位電路,本文

2022-01-17 12:38:52 13

13 什么是ttl電平

TTL電平信號被利用的最多是因?yàn)橥ǔ?shù)據(jù)表示采用二進(jìn)制規(guī)定,+5V等價于邏輯"1",0V等價于邏輯"0",這被稱做TTL(晶體管-晶體管邏輯電平)信號系統(tǒng),這是計算機(jī)處理器控制

2022-02-11 15:12:28 14

14 請注意LS和CMOS之間的高電平的不兼容性。

2022-03-11 10:28:15 1129

1129 TTL器件輸出低電平要小于0.8V,高電平要大于2.4V。輸入,低于1.2V就認(rèn)為是0,高于2.0就認(rèn)為是1。于是TTL電平的輸入低電平的噪聲容限就只有(0.8-0)/2=0.4V,高電平的噪聲容限為(5-2.4)/2=1.3V。

2022-08-22 10:10:50 9362

9362 為了精簡電路 電器中會用到邏輯電平代替復(fù)雜的接線 他們都是如何設(shè)計的呢? CMOS器件與TTL器件? ? CMOS電平與TTL電平 ? 如何利用MOS管實(shí)現(xiàn)雙向電平轉(zhuǎn)換 ? 什么是LVDS電平

2022-12-14 11:36:07 437

437 什么是TTL電平、CMOS電平、RS232電平?它們有什么區(qū)別呢?一般說來,CMOS電平比TTL電平有著更高的噪聲容限。

2023-02-07 14:58:26 4099

4099 電平,就是指電路中兩點(diǎn)或幾點(diǎn)在相同阻抗下電量的相對比值。這里的電量自然指“電功率”、“電壓”、“電流”,并將倍數(shù)化為對數(shù),用“分貝”表示,記作“dB”。常用邏輯電平有TTL、CMOS、RS232、RS485等。

2023-04-12 14:58:39 8897

8897

推挽輸出是低電平還是高電平? 推挽輸出器是一種常見的輸出方式。它由負(fù)和正三項(xiàng)組成,其中,負(fù)電平被連接到PNP晶體管,而正電平被連接到NPN晶體管。當(dāng)給定輸入信號時,晶體管被開啟或關(guān)閉,電流流過負(fù)極

2023-08-31 10:26:31 1544

1544 讀取某一個上拉電平信號,它可能輸出是低電平,可能是高電平,可能是方波,并且這個方波不知道頻率何占空比,那么如何來通過程序來判斷呢?高電平和低電平都好說,利用HAL庫讀取即可,如下

2023-11-07 08:00:52 996

996

金屬氧化物半導(dǎo)體)技術(shù)利用了兩種類型的晶體管:NMOS(負(fù)極性金屬氧化物半導(dǎo)體)晶體管和PMOS(正極性金屬氧化物半導(dǎo)體)晶體管。NMOS晶體管只有有源端施加

高電平時才能導(dǎo)通,而PMOS晶體管只有有源端施加低

電平時才能導(dǎo)通。這種互補(bǔ)配置使得

CMOS電路能夠?qū)?/div>

2024-01-09 11:25:51 669

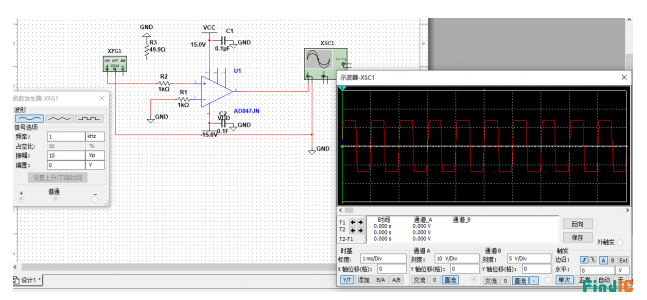

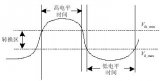

669 能夠看到,當(dāng)一個正弦波信號經(jīng)過比較器出來以后,就成為了一個方波信號(PWM信號)。從廣義的角度上來說,PWM信號是模擬信號,可以所所有的信號都是模擬的,數(shù)字信號是我們將其所謂的高電平定義為 1 ,低電平定義為 0 。

2024-02-15 10:41:00 100

100

STM32單片機(jī)以兼容CMOS與TTL電平。 首先,我們先了解一下CMOS和TTL電平的特性。CMOS和TTL是兩種常見的邏輯電平標(biāo)準(zhǔn)。CMOS電平一般定義為0V至VDD之間的電壓范圍,其中VDD

2024-02-02 13:57:47 576

576 )是常用的數(shù)字電路家族,兩者都有自己的特點(diǎn)和應(yīng)用范圍。在介紹如何轉(zhuǎn)換CMOS電平和TTL電平之前,我們先來了解一下它們的定義和特點(diǎn)。 CMOS電平: CMOS電平是一種用于數(shù)字電路傳輸?shù)碾妷簶?biāo)準(zhǔn)。常見

2024-02-22 11:10:52 341

341 半導(dǎo)體)管道組成。在CMOS電路中,輸入信號的高和低電平取決于輸入信號的電壓和電路中的配置。 對于CMOS門電路來說,判斷輸出電平的關(guān)鍵是輸入電壓。在理想的情況下,當(dāng)輸入電壓為高電平時,輸出為低電平;當(dāng)輸入電壓為低電平時,輸出電平為高電平。這是因?yàn)?b class="flag-6" style="color: red">CMOS電路的輸入管道是一個開關(guān),當(dāng)輸入電壓為高

2024-02-22 11:12:34 518

518 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論