在《數字電路之如雷貫耳的“邏輯電路”》、《數字電路之數字集成電路IC》之后,本文是數字電路入門3,將帶來「時序電路」的講解,及其核心部件觸發器的工作原理。什么是時序電路?

2016-08-01 10:58:48 18171

18171

在Vivado Implementation階段,有時是有必要分析一下什么原因導致運行時間(runtime)過長,從而找到一些方法來縮短運行時間。

2019-05-29 14:37:45 13596

13596

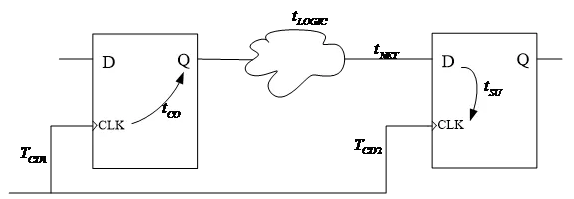

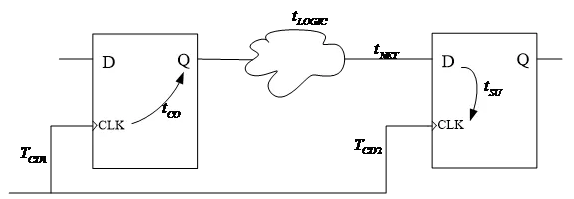

時序電路 首先來看兩個問題: 1.為什么CPU要用時序電路,時序電路與普通邏輯電路有什么區別。 2.觸發器、鎖存器以及時鐘脈沖對時序電路的作用是什么,它們是如何工作的。 帶著這兩個問題,我們從頭了解

2020-11-20 14:27:09 3998

3998

對于絕大部分的電路來說輸出不僅取決于當前的輸入值,也取決于原先的輸入值,也就是說電路具有記憶功能,這屬于同步時序電路。

2020-12-07 15:00:15 6297

6297

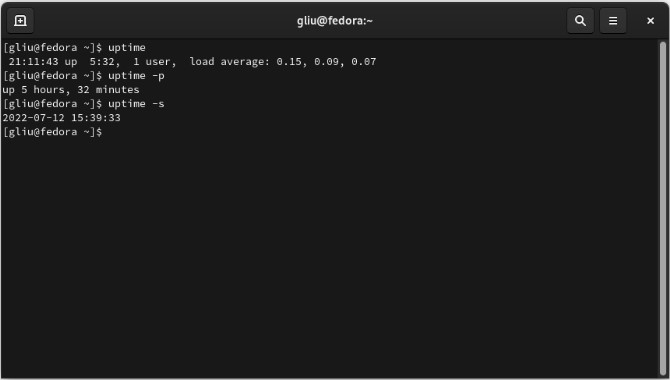

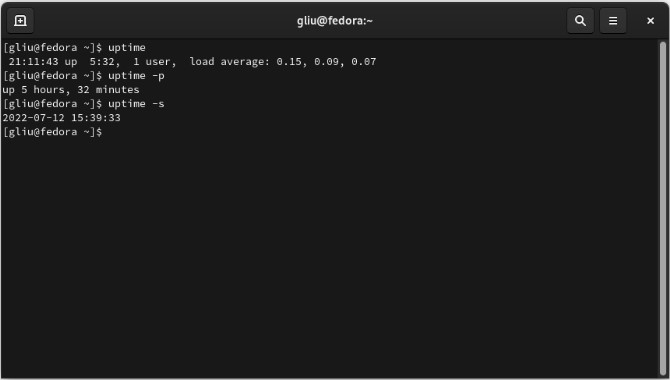

Linux 中的 uptime 用于查看系統啟動后的運行時間。它是一個比較簡單的 Linux 命令,可以不帶參數直接運行。

2022-11-25 15:25:47 14544

14544

什么是中斷?為什么CPU要用時序電路?時序電路與普通邏輯電路有什么區別呢?

2021-10-29 07:03:45

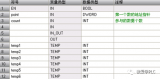

時序電路測試及應用一、實驗目的1.掌握常用時序電路分析,設計及測試方法。2.訓練獨立進行實驗的技能.二、實驗儀器及材料1.雙蹤示波器 2.

2009-08-20 18:55:27

(激勵函數),由此得到觸發器的特征方程.由上步得出的方程寫出狀態真值表,把觸發器的現態和外界的輸入信號作為時序電路的輸入信號.通過狀態真值表得到該時序電路的狀態圖和狀態表.通過電路的狀態表和狀態圖,對電路

2018-08-23 10:28:59

怎么在運行時隱藏控件,比如一個按鈕,用ON/OFF來隨時控制它的隱藏和可見,謝謝各位高手了!!!!

2013-09-06 10:41:16

消息。在此之后我甚至無法打開檢查點 - 如果我正在嘗試打開dcp,我將收到運行時錯誤“R6025 -pure虛函數調用”。在本主題中看起來像是一個錯誤:得到-R6025-運行時錯誤 - 運行 - 解構

2018-10-30 18:02:09

示波器查看IO口A電平,發現翻轉間隔時間很準;

2、雙核同時運行時,用示波器查看IO口A電平和IO口B電平,發現A和B的電平翻轉時間間隔大部分時間是準的,不定時會出現翻轉不準現象。

請教一下這是什么原因

2023-05-26 06:56:56

到了SystemInit的初始化Flash里,后面初始化字庫等都沒有運行就直接跳到while(1)中運行,所以對MDK的運行時序不是很明確,特求解答。

2019-06-05 04:35:27

嗨大家好,每當我嘗試運行vee運行時間來測試一個單元時,我得到“配置錯誤:串行接口,在10,沒有為此系統配置錯誤號碼:801請參閱安裝手冊中的說明在交易號:1對象標題:多儀器直接I / O對象類型

2019-05-15 13:18:09

對于相同優先級的任務采用時間片輪詢的方式運行,那比如說有兩個優先級都為5的任務,那這兩個任務的運行時間如何設置呢?在rt-thread中創建任務時就可以設置任務的運行時間,在freertos中怎么用呢?

2020-07-19 08:03:05

老師讓我把控件設置一下,他想讓控件在程序運行時不能再變動,類似變灰一樣,不運行時,能正常使用,問各路大神要怎么設置?

2013-12-04 16:57:22

嘿,有人注意到.NET事件沒有在運行時傳輸嗎?這是真的還是我瘋了?我不能發布一個例子,因為我無法重新創建它。我做的任何簡單的工作,它只是由于某種原因(顯然)完整的程序要么不是在運行時生成一些

2018-09-07 16:37:50

什么是時序電路?時序電路核心部件觸發器的工作原理

2021-03-04 06:32:49

什么是時序電路?SRAM是觸發器構成的嗎?

2021-03-17 06:11:32

來設計高能效的時序電路。 約翰遜計數器系統,可同步提供多種特殊類型的數據序列,這對于大多數重要應用(如D/A轉換器、FSM和時鐘分頻器)來說至關重要。為支持不同頻率(從MHz 到 GHz)的模塊

2018-09-30 16:00:50

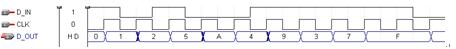

實驗二 基本時序電路設計(1)實驗目的:熟悉QuartusⅡ的VHDL文本設計過程,學習簡單時序電路的設計、仿真和硬件測試。(2)實驗內容:Ⅰ.用VHDL設計一個帶異步復位的D觸發器,并利用

2009-10-11 09:21:16

你好我想在我的設計中使用一個16位RAM,它包含N個數字系數。我想在運行時更新RAM。所以要做到這一點我應該使用哪種類型的RAM以及如何在運行時更新RAM。我正在使用ZC706板。

2019-10-23 09:03:15

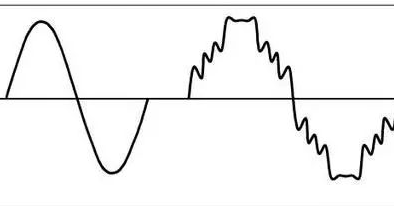

根據波形圖設計異步時序電路 急 求大神

2017-12-08 23:07:44

雖然學了一段時間STM32,但是還是沒明白指令的運行時間是怎么計算的,前段時間用IO模擬寫了一個SMBUS的程序,發現函數在“while(1)”里運行和在定時器中運行效果是不一樣的,還造成數據讀取

2016-01-20 09:16:16

混合波形圖運行時無法顯示曲線,怎么辦?!

2015-12-24 15:01:35

計數器及時序電路原理及實驗 一、實驗目的1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。 &

2009-10-10 11:47:02

設計一個同步時序電路:只有在連續三個或者三個以上時針作用期間兩個輸入信號相同時,其輸出為1,其余情況下輸出為0。

2013-03-22 10:44:50

運行庫文件是做什么的呢?運行時模型是什么?

2021-04-20 07:07:34

基于使用SDIO卡的Kintex-7 FPGA,我幾乎沒有查詢。你能否解決這些問題: - 查詢如下:我們在項目中使用XC7K160T-2FBG484C FPGA,在運行時我們要求IO bank

2020-04-28 10:17:52

PLD練習2(時序電路)

2006-05-26 00:14:19 20

20 針對實際故障診斷中難以有效獲得故障現場信息的問題,提出通過在軟件運行時注入故障的方式獲取故障現場信息,設計并實現一種運行時軟件故障注入器,給出其中的故障腳本描

2009-04-06 08:40:09 19

19 摘要:針對同步時序電路的初始化問題,提出了一種新的實現方法。當時序電路中有未確定狀態的觸發器時,就不能順利完成該電路的測試生成,因此初始化是時序電路測試生成中

2010-05-13 09:36:52 6

6 本文介紹將量子進化算法應用在時序電路測試生成的研究結果。結合時序電路的特點,本文將量子計算中的量子位和疊加態的概念引入傳統的測試生成算法中,建立了時序電路的量

2010-08-03 15:29:01 0

0 本章內容:q 鏡像電路q 準nMOS電路q 三態電路q 鐘控CMOS電路q 動態CMOS電路q 雙軌邏輯電路q 時序電路

2010-08-13 14:44:30 0

0

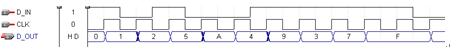

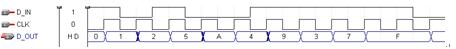

時序電路設計串入/并出移位寄存器一 實驗目的1掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進行時序電路設計的方法。

2009-03-13 19:29:51 5733

5733

時序電路設計串入/并出移位寄存器一 實驗目的1掌握VHDL語言的基本描述語句的使用方法。2掌握使用VHDL語言進行時序電路設計的方法。

2009-03-13 19:29:52 2023

2023

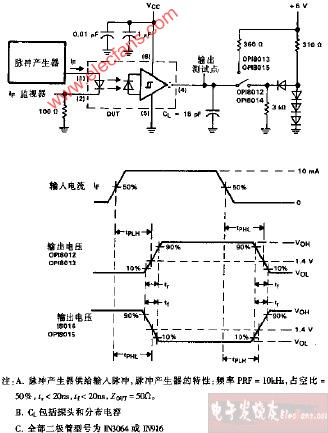

OPI812-OP1815開關時序電路及波形電路圖

2009-07-01 11:22:24 962

962

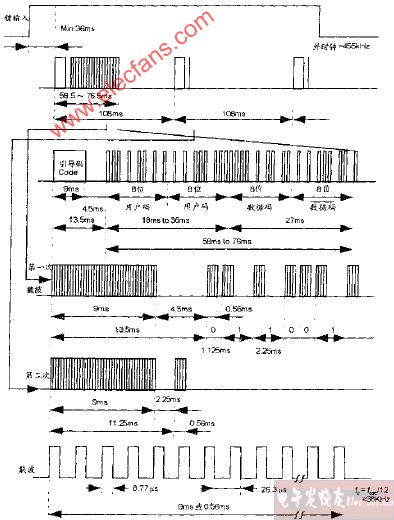

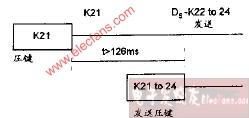

BLO508 A1輸出波形,單鍵操作時序電路圖

2009-07-02 10:54:11 542

542

BLO508 A1型雙鍵操作時序電路圖

2009-07-02 10:56:00 526

526

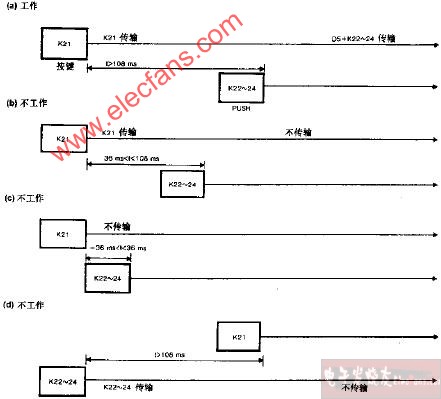

GM3043雙鍵工作時序電路圖

2009-07-02 11:07:30 424

424

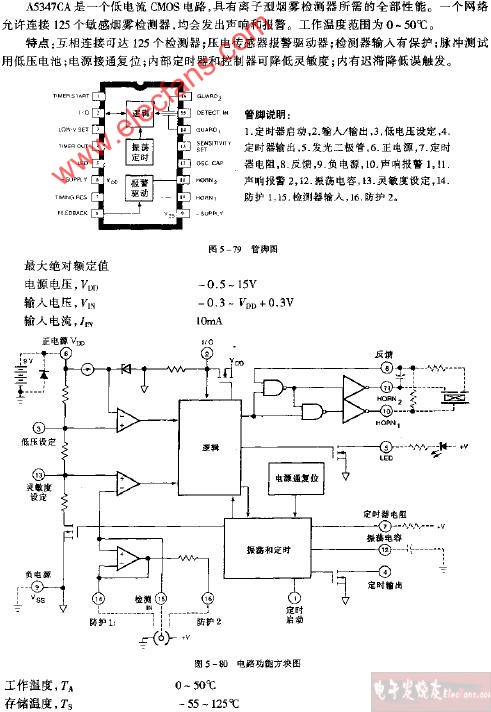

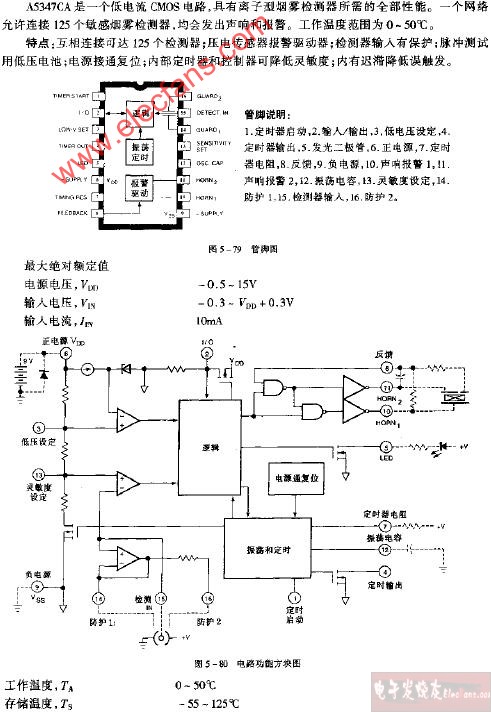

A5347電路功能方塊電路圖

2009-07-03 12:04:02 513

513

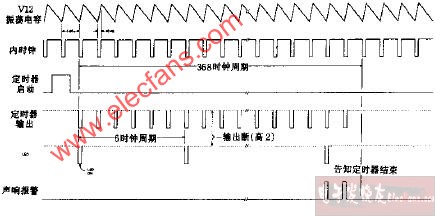

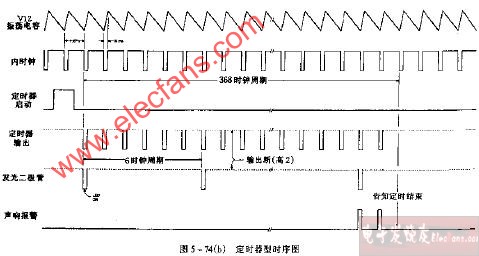

A5347定時器型時序電路圖

2009-07-03 12:09:08 546

546

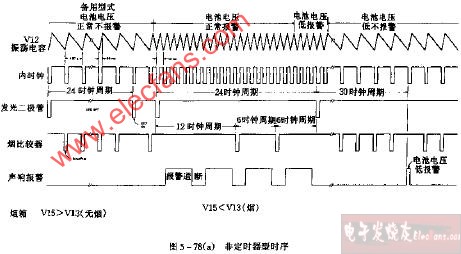

A5347非定時器型時序電路圖

2009-07-03 12:09:32 450

450

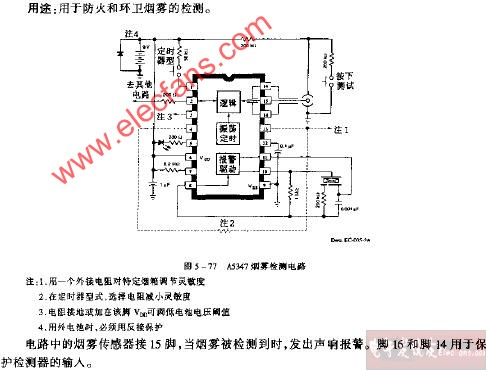

A5347管腳電路圖

2009-07-03 12:10:06 686

686

A5347煙霧檢測電路圖

2009-07-03 12:10:40 1026

1026

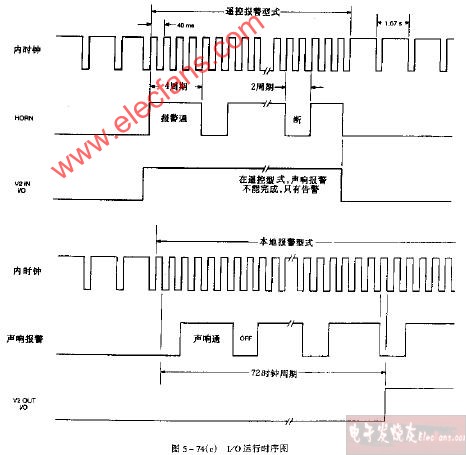

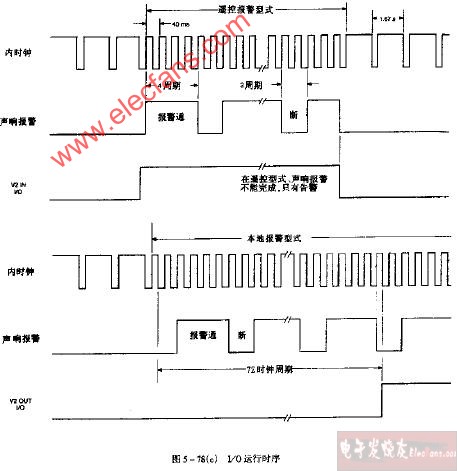

A5348 IO運行時序電路圖

2009-07-03 12:11:10 393

393

0

A5348定時器型時序電路圖

2009-07-03 12:12:17 413

413

A5348非定時器型時序電路圖

2009-07-03 12:12:59 453

453

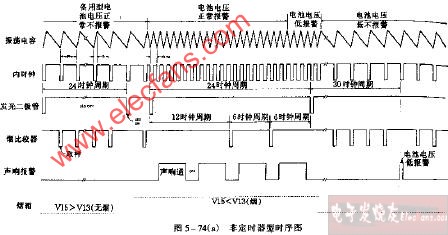

A5349 VO運行方式時序電路圖

2009-07-03 12:14:37 603

603

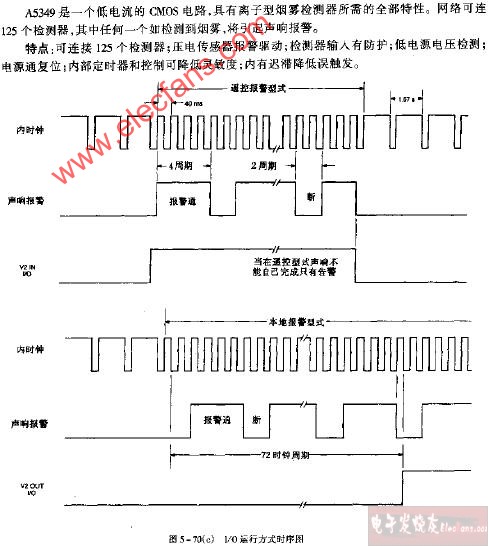

A5349定時器型式時序電路圖

2009-07-03 12:18:14 443

443

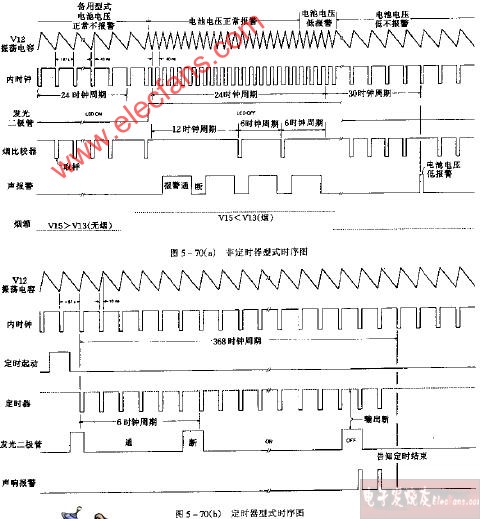

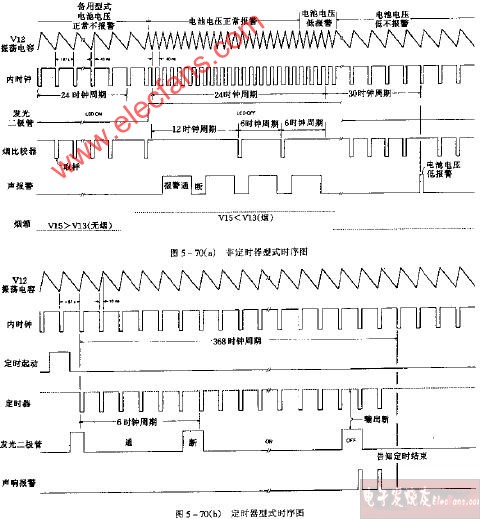

A5349非定時器型式時序電路圖

2009-07-03 12:18:51 461

461

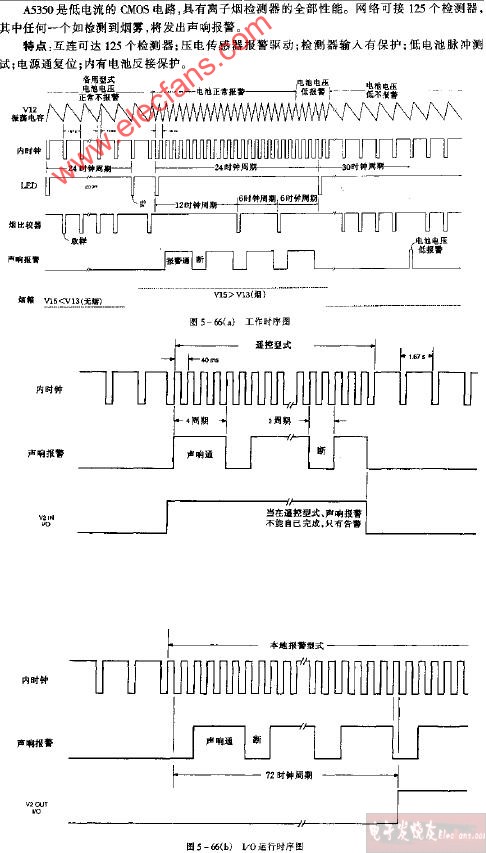

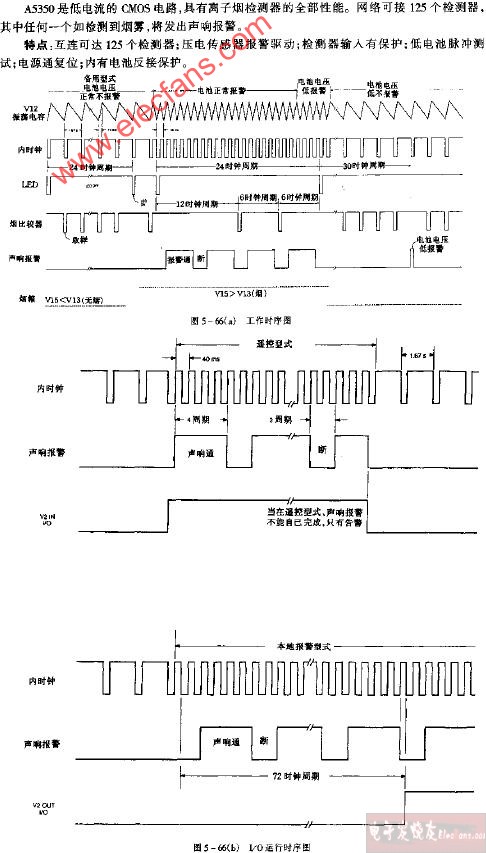

A5350 IO運行時序電路圖

2009-07-03 12:20:26 484

484

A5350工作時序電路圖

2009-07-03 12:22:16 652

652

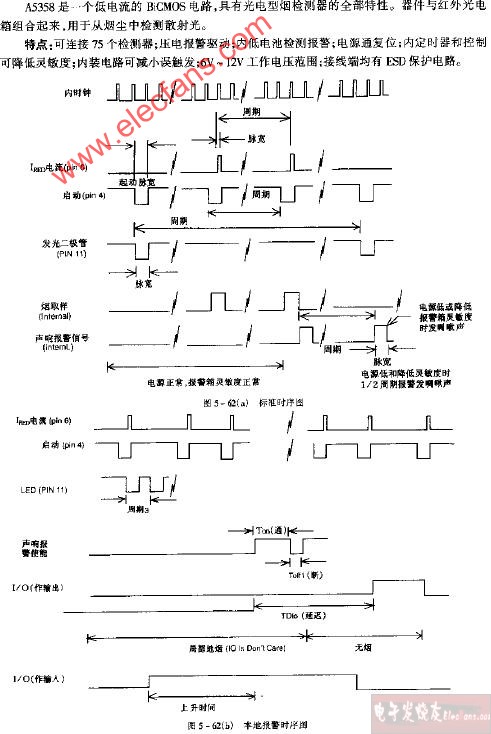

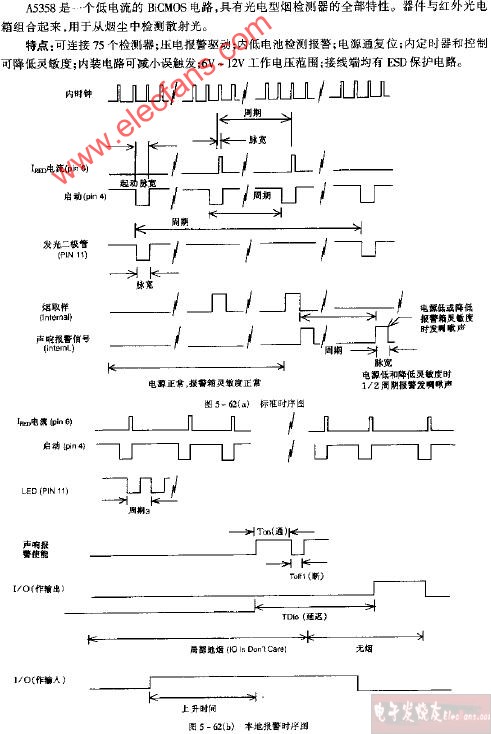

A5358本地報警時序電路圖

2009-07-03 12:23:28 944

944

A5358標準時序電路圖

2009-07-03 12:30:49 806

806

鍋爐低負荷運行時注意事項

為了滿足機組調峰,運行工況變動的需要,保證鍋爐安全、經濟運行,特制訂本措施。1、當鍋爐在低負

2009-11-13 18:22:03 2334

2334 同步時序電路

4.2.1 同步時序電路的結構和代數法描述

2010-01-12 13:31:55 4672

4672

什么是時序電路

任意時刻的穩定輸出,不僅與該時刻的輸入有關,而且還

2010-01-12 13:23:14 8109

8109

為了實現時序電路狀態驗證和故障檢測,需要事先設計一個輸入測試序列。基于二叉樹節點和樹枝的特性,建立時序電路狀態二叉樹,按照電路二叉樹節點(狀態)與樹枝(輸入)的層次邏輯

2012-07-12 13:57:40 0

0 C語言教程之顯示程序運行時間,很好的C語言資料,快來學習吧。

2016-04-25 16:09:48 0

0 解決PADS 9.5中文語言下修改零件標號提示“發生嚴重的運行時錯誤”并退出的問題。

2016-09-27 14:46:39 0

0 FPGA運行時重構的延遲隱藏機制研究與實現_劉偉

2017-01-07 19:08:43 0

0 1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。

2、了解同步計數器,異步計數器的使用方法。

3、了解同步計數器通過清零阻塞法和預顯數法得到循環任意進制

2022-07-10 14:37:37 15

15 運行時組態是組態軟件新近提出的新的概念。運行時組態是在運行環境下對已有工程進行修改,添加新的功能。它不同于在線組態,在線組態是在工程運行的同時,進入組態環境,在組態環境中對工程進行修改。而運行時組態是在運行環境中直接修改工程。

2017-10-13 16:17:11 2

2 在傳統設計中,所有計算機運算(算法邏輯和存儲進程) 都參考時鐘同步執行,時鐘增加了設計中的時序電路數量。在這個電池供電設備大行其道的移動時代,為了節省每一毫瓦(mW) 的功耗,廠商間展開了殘酷的競爭

2017-10-25 15:41:59 25

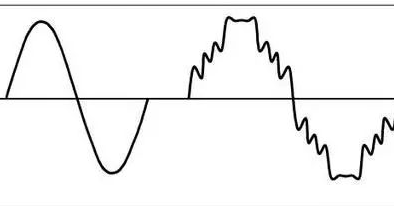

25 在電源的運行過程中,諧波干擾是最常見的,工程師們往往需要不斷的升級PFC電路來改進自家的電源產品,如何定位電源運行時的每一次諧波值和頻率呢,本文給出答案。

2017-10-27 15:31:18 6128

6128

“時鐘是時序電路的控制者” 這句話太經典了,可以說是FPGA設計的圣言。FPGA的設計主要是以時序電路為主,因為組合邏輯電路再怎么復雜也變不出太多花樣,理解起來也不沒太多困難。但是時序電路就不

2018-07-21 10:55:37 4504

4504 組合電路和時序電路是計算機原理的基礎課,組合電路描述的是單一的函數功能,函數輸出只與當前的函數輸入相關;時序電路則引入了時間維度,時序電路在通電的情況下,能夠保持狀態,電路的輸出不僅與當前的輸入有關,而且與前一時刻的電路狀態相關,如我們個人PC中的內存和CPU中的寄存器,均為時序電路。

2018-09-25 09:50:00 24779

24779 關鍵詞:時序電路 , 同步 同步時序電路設計 1.建立原始狀態圖. 建立原始狀態圖的方法是: 確定輸入、輸出和系統的狀態函數(用字母表示). 根據設計要求,確定每一狀態在規定條件下的狀態遷移方向

2018-10-31 18:14:01 1097

1097 時序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質的區別在于時序電路具有記憶功能。

2019-09-27 07:10:00 2169

2169

時序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質的區別在于時序電路具有記憶功能。

2019-09-23 07:08:00 2067

2067

前幾天有個學員咨詢一個程序設計的問題,程序的控制要求如下:需要控制5臺電機的運行,每臺電機運行時需要記錄運行時間,電機啟動運行時,根據記錄的運行時間,從小到大,每個2s依次啟動電機的運行。

2019-07-19 08:57:19 6401

6401

本文檔的主要內容詳細介紹的是數碼管與分析儀的時序電路原理圖免費下載。

2019-12-13 15:17:11 8

8 時序電路是數字電路的基本電路,也是FPGA設計中不可缺少的設計模塊之一。

2020-09-08 14:21:22 6067

6067

時間的重要性不言而喻,加上時間這個維度就如同X-Y的平面加上了一個Z軸,如同打開了一個新的世界。所以今天我們就要來聊聊時序電路。 在時序電路中,電路任何時刻的穩定狀態輸出不僅取決于當前的輸入,還與

2021-01-06 17:07:22 4371

4371 ,最終可能會引起運行時間方面的問題。這在項目后期需要大量的時間和金錢來解決。如果不能掌握系統的運行狀態,則很難發現系統內缺陷的根源。 解決方案 將TA軟件工具套件與VX1000測量標定硬件相結合,可同步分析 ECU內部運行時序和外部總

2021-10-28 11:05:43 1806

1806 前言 ????測試代碼的運行時間的兩種方法: 使用單片機內部定時器,在待測程序段的開始啟動定時器,在待測程序段的結尾關閉定時器。為了測量的準確性,要進行多次測量,并進行平均取值。 借助示波器的方法

2021-11-09 09:52:04 3320

3320

組合邏輯和時序邏輯電路是數字系統設計的奠基石,其中組合電路包括多路復用器、解復用器、編碼器、解碼器等,而時序電路包括鎖存器、觸發器、計數器、寄存器等。 在本文中,小編簡單介紹關于時序電路的類型和特點等相關內容。

2022-09-12 16:44:00 7234

7234

讀出S7-1500 CPU的運行時間有多種方式,下面分別介紹這幾種方式。

2022-10-09 14:20:54 2440

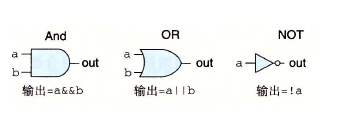

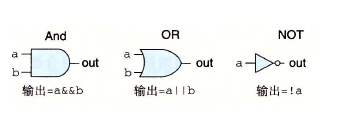

2440 從今天開始新的一章-Circuits,包括基本邏輯電路、時序電路、組合電路等。

2022-10-10 15:39:01 875

875 了解如何讓您的汽車電池更穩定、運行時間更長

2022-11-01 08:27:33 0

0 自 2018 年以來,Go GC,以及更廣泛的 Go 運行時,一直在穩步改進。近日,Go 社區總結了 4 年來 Go 運行時的一些重要變化。

2022-11-30 16:21:38 493

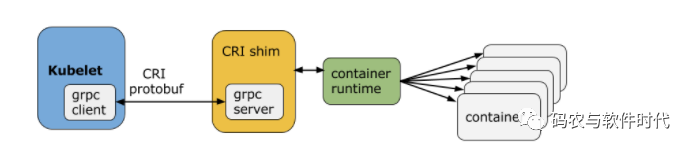

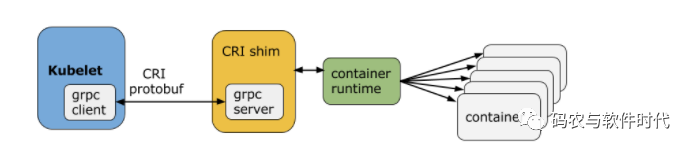

493 起初,Docker是事實上的容器技術標準,Kubernetes v1.5之前的代碼中直接調用Docker API,實現容器運行時的相關操作。

2023-02-20 16:22:33 979

979

那么,如何才能將過去的輸入狀態反映到現在的輸出上呢?「時序電路」到底需要些什么呢?人類總是根據過去的經驗,決定現在的行動,這時我們需要的就是—記憶。同樣,「時序電路」也需要這樣的功能。這種能夠實現人類記憶功能的元器件就是觸發器。

2023-03-24 10:48:58 818

818

同步和異步時序電路都是使用反饋來產生下一代輸出的時序電路。根據這種反饋的類型,可以區分這兩種電路。時序電路的輸出取決于當前和過去的輸入。時序電路分為同步時序電路和異步時序電路是根據它們的觸發器來完成的。

2023-03-25 17:29:52 17511

17511

電力電容器運行中,會因為各種因素出現故障。在電力電容器運行時遇到的故障中,出現滲油和漏油的概率非常大。那么如何避免電力電容器運行時漏油呢?庫克庫伯電氣會在接下來的文章中,針對電力電容器漏油的原因進行分析,提出解決電容器漏油的方法。

2023-04-07 16:01:40 519

519 說一下 JVM 運行時數據區吧,都有哪些區?分別是干什么的?

2023-08-19 14:35:34 393

393

ch32v307記錄程序運行時間 在程序開發中,很重要的一項任務就是對程序的運行時間進行評估。對于大型的程序系統來說,它們通常需要處理大量的數據或進行復雜的計算操作。因此,如果程序的運行時間過長

2023-08-22 15:53:37 407

407 電子發燒友網站提供《Xilinx運行時(XRT)發行說明.pdf》資料免費下載

2023-09-14 10:01:21 0

0 緊密耦合的容器運行時繼承了主機操作系統的安全態勢和攻擊面。運行時或主機內核中的任何漏洞及其利用都會成為攻擊者的潛在切入點。

2023-11-03 15:24:55 260

260 當RUN信號為TRUE時,開始計時,為FALSE時停止計時,單次運行時間清零,長按RESET為5秒時,單次和總運行時間都清零。

2023-11-27 09:59:37 577

577

JVM是Java Virtual Machine(Java虛擬機)的縮寫,它是Java編程語言的運行環境。JVM的主要功能是將Java源代碼轉換為機器代碼,并且在運行時管理Java程序的內存。JVM

2023-12-05 14:08:10 212

212 時序電路是由觸發器等時序元件組成的數字電路,用于處理時序信號,實現時序邏輯功能。根據時序元件的類型和組合方式的不同,時序電路可以分為同步時序電路和異步時序電路。本文將從這兩個方面詳細介紹時序電路

2024-02-06 11:22:30 291

291 時序電路是一種能夠按照特定的順序進行操作的電路。它以時鐘信號為基準,根據輸入信號的狀態和過去的狀態來確定輸出信號的狀態。時序電路廣泛應用于計算機、通信系統、數字信號處理等領域。根據不同的分類標準

2024-02-06 11:25:21 399

399 時序電路基本原理是指電路中的輸出信號與輸入信號的時間相關性。簡單來說,就是電路的輸出信號要依賴于其輸入信號的順序和時間間隔。 時序電路由時鐘信號、觸發器和組合邏輯電路組成。時鐘信號是時序電路的重要

2024-02-06 11:30:00 344

344

電子發燒友App

電子發燒友App

硬聲App

硬聲App

18171

18171

13596

13596

3998

3998

6297

6297

14544

14544

19

19 6

6 0

0 5733

5733

2023

2023

0

0 15

15 2

2 25

25 6128

6128

4504

4504 24779

24779 1097

1097 2169

2169

2067

2067

6401

6401

4371

4371 1806

1806 3320

3320

7234

7234

493

493 979

979

818

818

17511

17511

519

519 407

407 577

577

212

212 291

291 399

399 344

344

評論