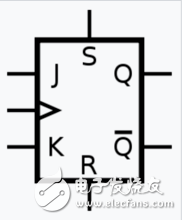

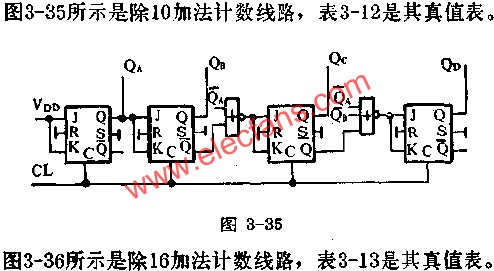

J-K觸發器電路圖

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網>電子技術應用>電子技術>電路圖>數字電路圖>J-K觸發器電路圖

相關推薦

2572

2572 1874

1874 16964

16964

5720

5720

2

2 6

6 40171

40171

13

13 1916

1916

57

57 15449

15449 44

44 290

290 2249

2249

評論