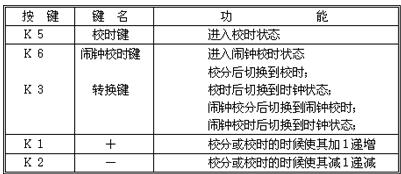

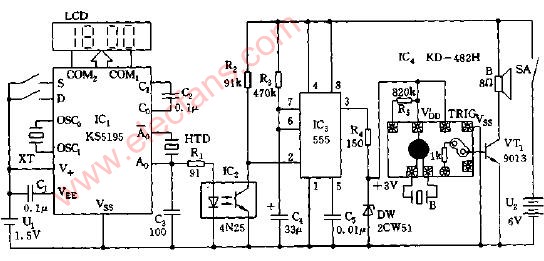

LCD數字鐘整點語音報時電路圖

- 數字鐘(31004)

相關推薦

數字鐘綜合實驗及原理

數字鐘綜合實驗及原理 一、設計要求(數字鐘的功能)1、具有時、分、秒計數顯示功能,以二十四小時循環計時。2、具有清零,調節小時,分鐘的功能。3、具有整點報時同時LED燈花樣顯示

2009-10-10 11:49:14

PIC16F887 單片機 創意數字鐘 DS1302

題目:創意數字鐘基本要求:創意性設計;溫度顯示;日歷顯示;設置信息帶記憶功能。/*題目:創意數字鐘基本要求:創意性設計;溫度顯示;日歷顯示;設置信息帶記憶功能。創意:鬧鐘 整點報時記憶:設置的鬧鐘會被記憶下來*/...

2021-11-16 13:21:01 13

13

13

13簡易數字鐘設計

簡易數字鐘設計一、摘要信息時代,時間觀念深入人心,所以掌握數字鐘的設計具有一定的時代意義,并且使用Multisim進行分立元件設計數字鐘,可以大大提升個人數字電路的素養。設計思路是從上至下,先進行數字鐘

2021-11-06 19:06:01 45

45

45

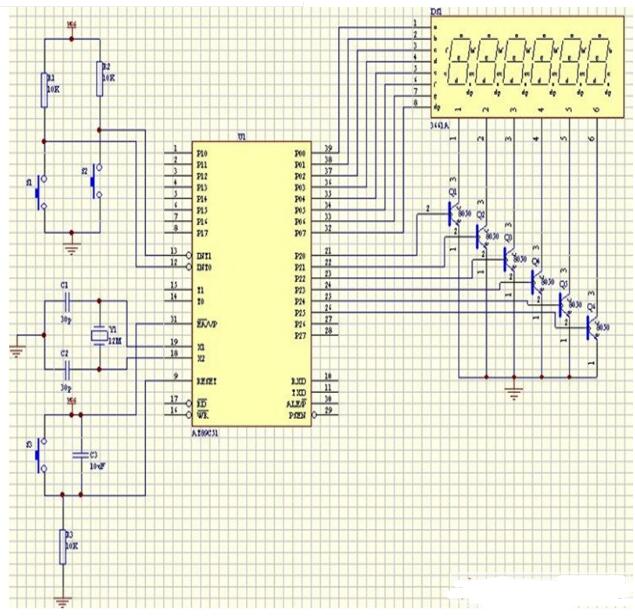

45基于51單片機的數字鐘設計

利用定時器實現數字鐘設計選用芯片:AT89S52功能:能校時和校分,具有整點報時功能(四低一高)。我在設計的時候,想設計出那種四低一高的整點報時,剛開始想的時候確實費了點腦子,在網上搜也沒相關的代碼

2021-11-04 11:51:00 15

15

15

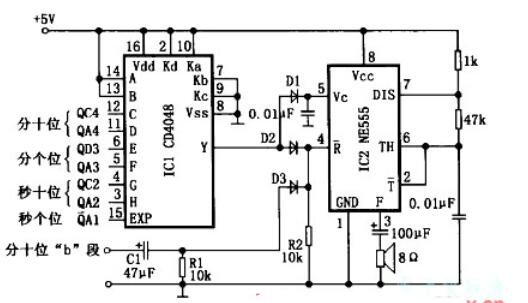

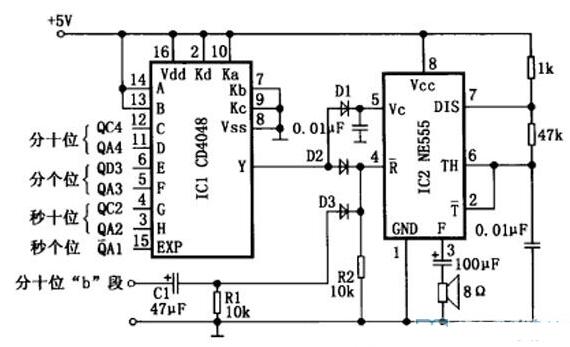

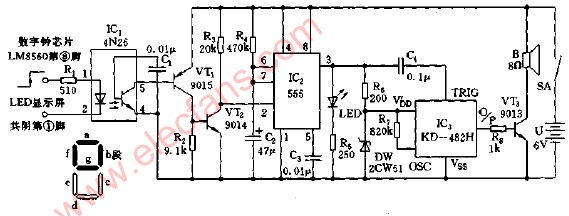

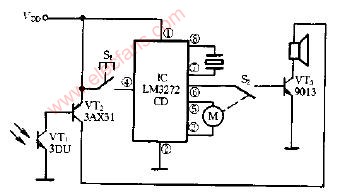

15CD4048制作模擬電臺報時電路

該電路每當數字鐘走到“59分50秒”時開始報時,在秒個位顯示“0、2、4、6、8”的時間鳴叫“嘟”,其叫五聲,在顯示“00分00秒”時鳴叫一聲“嘀”。

2021-05-01 16:37:00 2365

2365

2365

2365

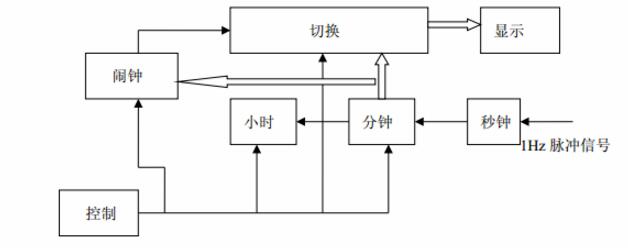

使用verilog實現多功能數字時鐘的設計資料說明

多功能數字鐘是采用數字電路實現用數字顯示時間的計時裝置。主要由振蕩器、分頻器、計時器、譯碼顯示及擴展電路幾部分構成。具有時間顯示、校時校分及鬧鐘設置、整點報時等擴展功能并且具有走時準確、顯示直觀、穩定等優點深受人們喜愛。

2020-11-05 17:35:14 23

23

23

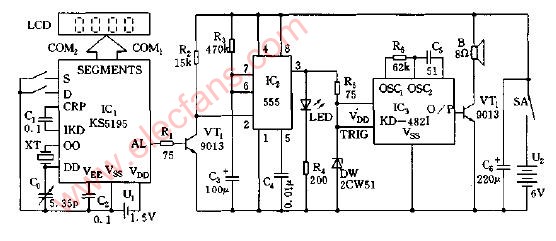

23簡單的模擬電臺報時電路圖

這款電路如下圖所示,該電路每當數字鐘走到“59分50秒”時開始報時,在秒個位顯示“0、2、4、6、8”的時間鳴叫“嘟”,其叫五聲,在顯示“00分00秒”時鳴叫一聲“嘀”。

2020-03-23 16:36:07 4166

4166

4166

4166

設計具有整點報時和可校時帶鬧鐘數字鐘的數字電路實驗資料免費下載

數字鐘實際上是一個對標準頻率進行計數的計數電路。它的計時周期是24小時,由于計數器的起始時間不可能與標準時間(如北京時間)一致所以采用校準功能和報時功能。

2019-08-29 08:00:00 29

29

29

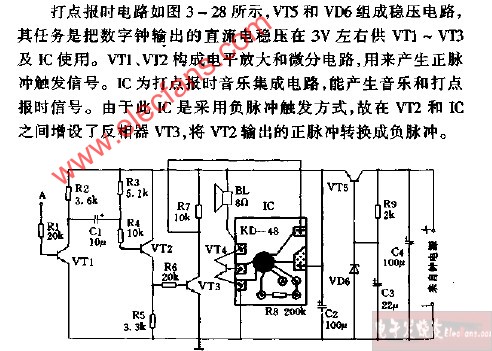

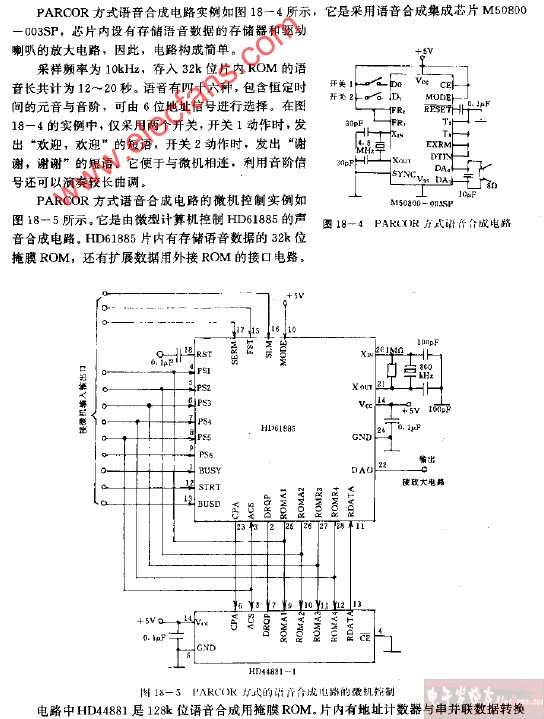

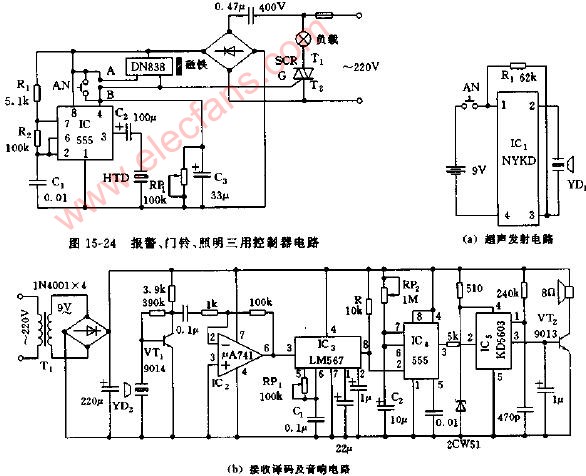

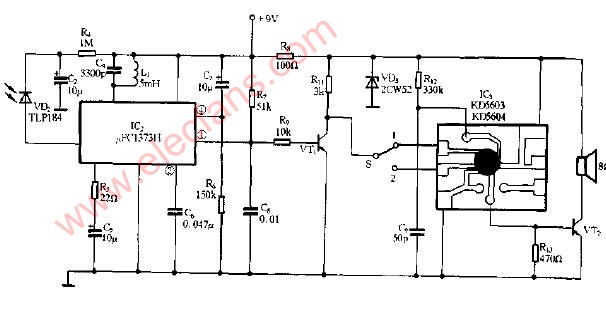

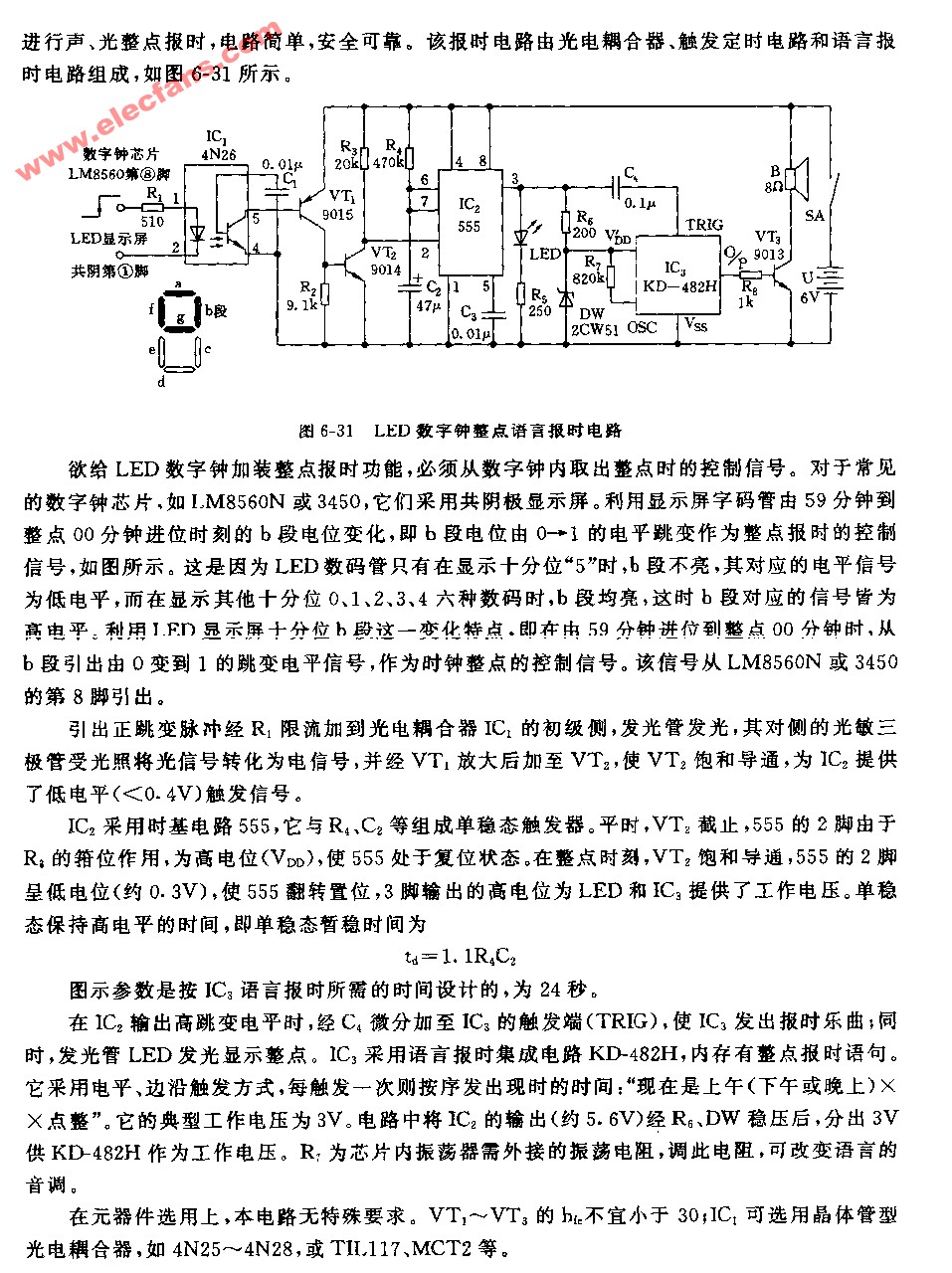

29LED數字鐘語言報時電路

關鍵詞:LED , 數字鐘 , 語言報時 一般動態LED數字鐘都無報時功能,這里只要增加一個簡單的電路就能使它實現整點報時功能。所采用的集成電路本身具有程控靜音功能,從晚上11點到凌晨5點不報時

2018-11-09 11:15:02 654

654

654

654數字時鐘設計電路圖匯總(七款數字時鐘電路圖)

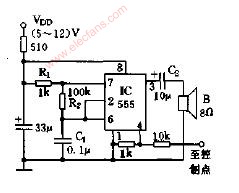

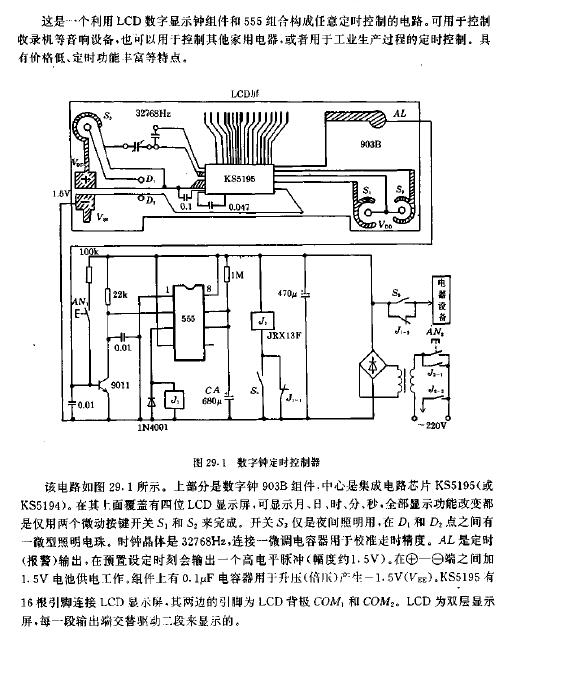

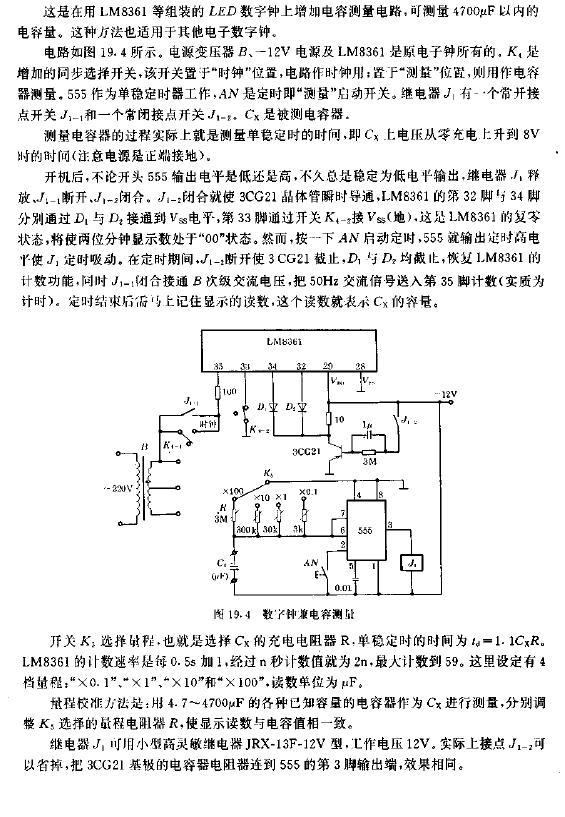

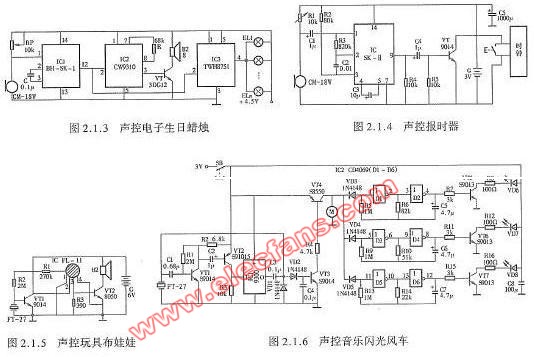

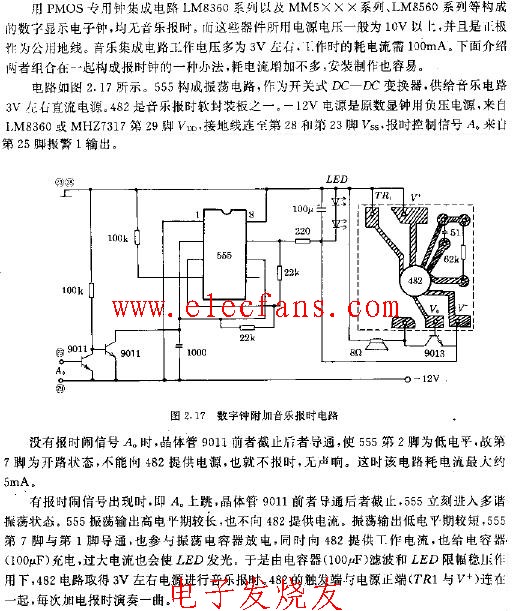

本文主要介紹了七款數字時鐘設計電路圖。數字鐘是一種用數字電路技術實現時、分、秒計時的鐘表。與機械鐘相比具有更高的準確性和直觀性,具有更長的使用壽命,已得到廣泛的使用。

2018-01-26 11:14:30 155285

155285

155285

155285

簡單數字鐘仿真電路圖大全(五款數字鐘仿真電路圖)

本文詳細介紹了五款數字鐘仿真電路圖。數字鐘實際上是一個對標準頻率(1HZ)進行計數的計數電路。由于計數的起始時間不可能與標準時間(如北京時間)一致,故需要在電路上加一個校時電路,同時標準的1HZ時間信號必須做到準確穩定。通常使用石英晶體振蕩器電路構成數字鐘。

2018-01-26 10:44:56 96265

96265

96265

96265

基于Quartus II平臺的多功能數字鐘的設計

文中簡要介紹了一種基于FPCJA的多功能數字鐘設計方案。在實現數字鐘計時、校時和整點報時等基本功能的基礎上增加世界時鐘功能,能夠將北京時間快速轉換為格林威治標準時。該方案采用VHDL和原理圖相結合

2017-11-30 14:57:28 131

131

131

131數字鐘工作原理及基于EDA技術的數字鐘設計

為使數字鐘從電路設計、性能分析到設計出PCB版f即印制電路版)圖的整個過程能夠在計算機上自動處理完成,從而縮短設計周期、提高設計效率、減小設計風險。本系統基于EDA技術的設計方法,提出一種采用

2017-11-29 11:06:51 48

48

48

48基于STC89C51單片機帶整點報時與鬧鐘功能的數字鐘設計

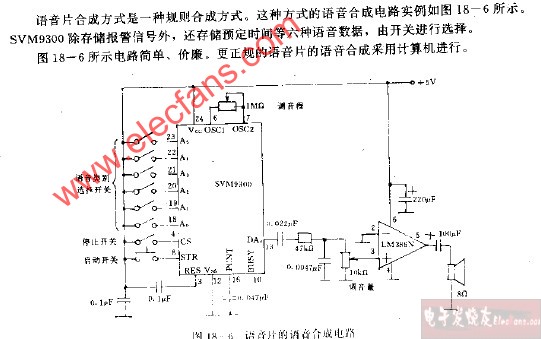

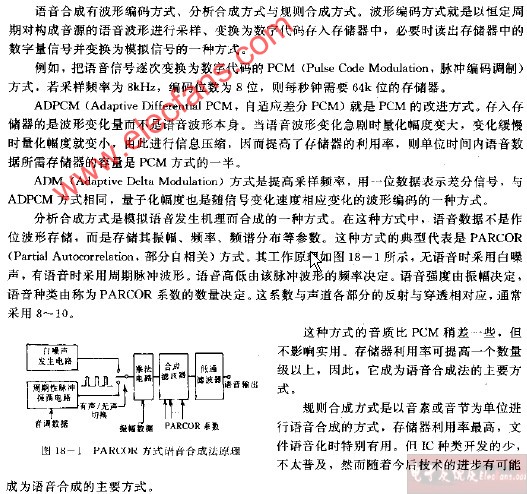

數字鐘的所有計時都要由軟件控制實現。用軟件對幾個按鍵所得信號進行相應改變,以控制時鐘與鬧鐘的顯示。通過軟件對鬧鐘與時鐘進行比較,當時鐘所顯示時間與鬧鐘一樣時,要啟動報時模塊。 在眾多的語音芯片

2017-11-29 10:35:18 58

58

58

58基于AT89C51與語音芯片ISD1110的語音報時數字鐘的設計

快捷、便利的生活。 本文采用 AT89C51 單片機為核心構成的語音報時功能的數字鐘。該系統操作簡單,方便,可隨時調節時間,制定時間報時。系統采用語音芯片 ISD1110和米頭組成了語音錄放模塊;采用時鐘芯片 DS1302 和 32768HZ 晶振組成了時鐘模

2017-11-28 14:41:42 30

30

30

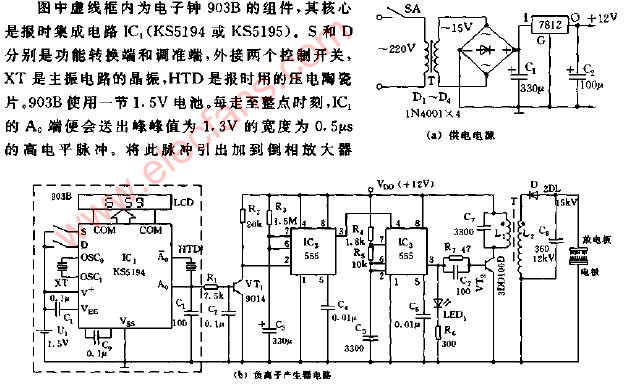

30基于單片機數字電子鐘的計時、整點報時等功能的實現

,且有一個置零功能,可以組成六十進制和二十四進制的計數器。 整點報時模塊電路用的是555芯片和一塊CD4068芯片組成的電路,555芯片可以接成多諧振蕩器,提供交變信號使蜂鳴器發出聲音,而整點報時的控制可以用CD4068實現,CD4068是8輸入與/與非門, 可

2017-11-28 14:24:37 37

37

37

37基于Quartus的多功能數字鐘的工作原理及各模塊的詳細說明

該實驗是利用QuartusII軟件設計一個數字鐘,進行試驗設計和仿真調試,實現了計時,校時,校分,清零,保持和整點報時等多種基本功能,并下載到SmartSOPC實驗系統中進行調試和驗證。此外還添加

2017-11-28 14:18:55 30

30

30

30數字鐘課程設計概述

本次課程設計的題目是設計一個數字鐘,要求具有以下功能:顯示時、分、秒(如23:52:45);可實現手動或自動的對時、分進行校正;計時過程具有報時功能,當時間到達整點前10秒進行報時。本報告就是對這次

2016-10-12 17:42:49 105

105

105

105多功能數字鐘的設計與實現_龐宇擎

本方案設計的多功能數字鐘采用單片機作為控制芯片,用按鍵輸入設置,通過12864液晶屏進行輸出顯示,除了傳統的年月日時分秒顯示時間功能 之外還具有測量溫度,自動背光照明,陰歷節氣顯示,整點報時等功能,具有外觀精美、走時準確的特點,同時電路和程序設計充分體現電子裝置的智能化 優勢。

2016-03-28 14:34:35 23

23

23

23基于FPGA和Quartus II的多功能數字鐘設計與實現

本文以FPGA平臺為基礎,在QuartusⅡ開發環境下設計開發多功能數字鐘。數字鐘實現計時\校時\整點報時\世界時鐘功能.

2012-12-18 11:51:03 32123

32123

32123

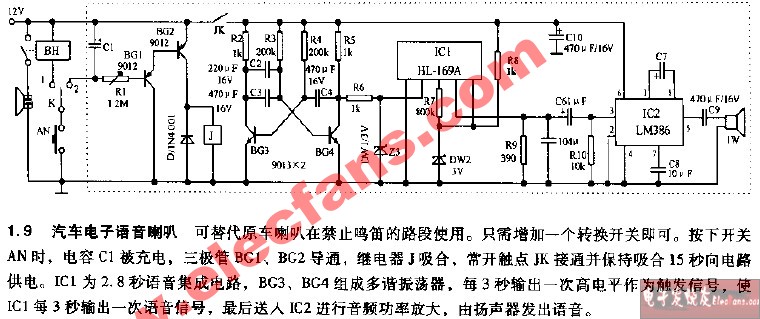

32123帶整點報時與鬧鐘功能的數字鐘

2012-12-15 17:17:39 198

198

198

198STC89C51帶整點報時與鬧鐘功能的數字鐘設計

本設計是以 STC89C51 單片機為核心器件,應用 ISD1420,74HC573 等器件,實現命題要求。經過測試,該數字鐘達到所有命題 所要求的技術指標。在此基礎之上,本設計添加了語音模塊,使設

2012-10-29 17:49:44 365

365

365

365電腦數字鐘硬件原理圖

電腦數字鐘硬件原理圖

為了節約制作硬件的開支,我們利用單片機開發機上的硬件資源,開發了電腦數字鐘的軟件。該數字鐘由8031單片機控制,采用24小時制計時

2009-03-14 15:25:19 1973

1973

1973

1973

電子發燒友App

電子發燒友App

評論