摘要:為了適應機載液晶顯示器向低功耗、高集成度發展的趨勢,提出了一種基于Zynq可擴展處理平臺的圖形生成電路實現方法.該方法以Zynq為核心搭建硬件平臺,使用Zynq集成的ARM 處理器執行圖形生成算法運算,配合可編程邏輯資源,按照一種三緩沖機制對DDR3SDRAM 幀存數據進行緩沖處理,實現圖形的實時生成.采用本設計可以生成多種分辨率的機載圖形畫面.實驗結果表明,當生成分辨率為1024×768的EFIS電子飛行顯示系統畫面時,幀率可達74fps,能夠滿足機載液晶顯示器高性能實時顯示需求。

?

1 引言

在飛機座艙顯示系統中圖形顯示占據重要地位[1].主顯示器尺寸不斷加大,分辨率不斷提高,并日益朝著大屏幕化、綜合化、信息化和智能化方向發展[2].隨著分辨率的提高,要顯示的信息量也大幅增加,座艙圖形綜合顯示系統是一個對實時性要求很高的系統[3],軍用飛機在做戰術動作時,畫面變換速度快,要求圖形的更新速度也必須很快,至少要比幀或場的刷新速度快,才可以避免畫面的斷續[4G5].采用DSP+FPGA 的圖形硬件加速架構,或者使用專用GPU 圖形生成芯片,都可以生成高分辨的機載顯示器圖形,但隨之而來的是產品成本的急劇增加以及功耗的不斷上升[6].為機載圖形顯示系統配置更合理的硬件設計和軟件架構變得尤為迫切。

Xilinx最新平臺Zynq將處理器的軟件可編程能力與FPGA 的硬件可編程能力實現完美結合,以低功耗和低成本等系統優勢實現良好的系統性能、靈活性和可擴展性[7].本文提出一種基于Zynq可擴展處理平臺的實時圖形生成電路,利用Zynq內部集成的ARM 處理器以及可編程邏輯資源,實現了機載顯示器圖形畫面的實時生成與顯示。

2 Zynq簡介

2.1 Zynq構成

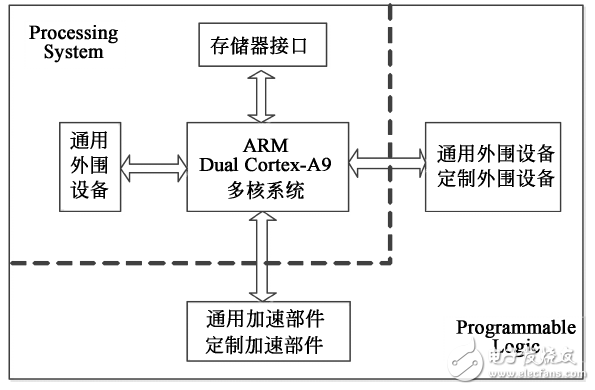

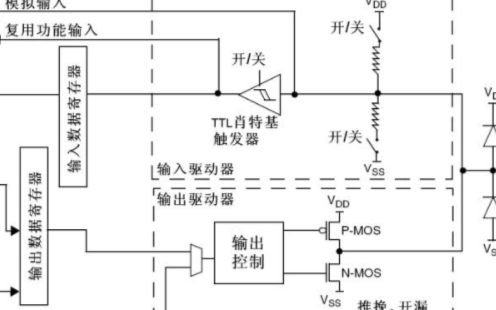

Zynq構架將內部結構分為處理器系統(ProcessingSystem,PS)與可編程邏輯(ProgrammableLogic,PL)兩部分[8].PS部分包括雙ARM CortexGA9內核、存儲器接口以及通用外設接口等資源.PL部分也即常規的FPGA,通過PL生成的IP核可以作為ARM 內核的擴展外圍設備或者ARM 內核的加速部件.Zynq器件內部結構圖如圖1所示。

圖1 Zynq內部結構圖

Zynq架構可以對PL和PS中運行的自定義邏輯和軟件方便地進行管理和規劃,PS和PL的單芯片綜合使其在I/O 數據帶寬、功能耦合、功耗預算等方面的性能表現大大超越了以往ASSP和FPGA 雙芯片解決方案。

PS和PL可以通過多種途徑實現互聯,包括GPIO端口、AXI總線端口、EMIO 端口、中斷、DMA 等等.其中AXI總線是ARM 系統中連接各個模塊的主要通道,各個功能部件通過AXI總線實現互聯.在PL中可以通過工具自動生成帶有AXI接口的IP 核,和PS 端進行高速數據交互。

2.2 DDR Memory控制器

Zynq內部集成的DDR memory控制器支持DDR2、DDR3、LPDDR2等多種存儲器類型,包含了3個主要模塊:AXI存儲器端接口DDRI、帶有傳輸調度機制的中央控制器DDRC 和物理層控制器DDRP[9].DDRmemory控制器框圖如圖2所示。

圖2 DDR Memory控制器框圖

DDRI端口符合AXI總線標準,包含4個64位的同步AXI接口,分別為S0、S1、S2、S3,用于接收多個AXI主端的訪問請求,其中S0和S1端口接收PS部分CPU 的訪問請求;S2和S3端口接收PL部分邏輯端的訪問請求.DDRC對來自多個AXI主端的訪問請求按照其調度策略進行裁決,裁決實施的依據是主控端訪問的優先級、等待時長計數器和緊急信號.DDRP 處理來自于DDRC的讀寫請求,并將其轉換成符合DDR 存儲器時序要求的特定信號。

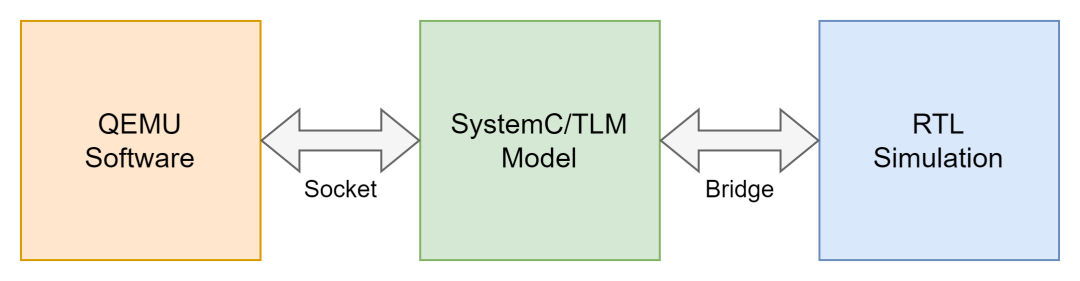

2.3 AXI VDMA

AXI VDMA 是Xilinx公司開發的一個軟核IP,用于在系統存儲器和支持AXI4-Stream 視頻類型的目標IP之間提供一個高速的數據存取通道[10].AXI4-Stream 格式數據流不能直接用于驅動顯示,還需要將數據流以視頻使能信號為界進行分割,配合行場同步信號驅動視頻終端顯示。

該IP 有兩路AXI4-Stream 接口,分別為AXI Memory Map to Stream (MM2S)Stream Master 和AXI4-Stream to Memory Map(S2MM)Stream Slave,其中MM2S為主端口,用于輸出轉換成AXI4-Stream 格式視頻流的系統存儲器中數據.S2MM 為從端口,用于接收AXI4-Stream 格式視頻流轉換成存儲器數據.MM2S和S2MM 彼此相互獨立,可以并行同時工作.PS端的處理器可通過AXI4-Lite總線對其內部的寄存器進行訪問以控制VDMA 工作模式、獲取VDMA 工作狀態。

3 設計實現

3.1 硬件設計

3.1.1 硬件架構

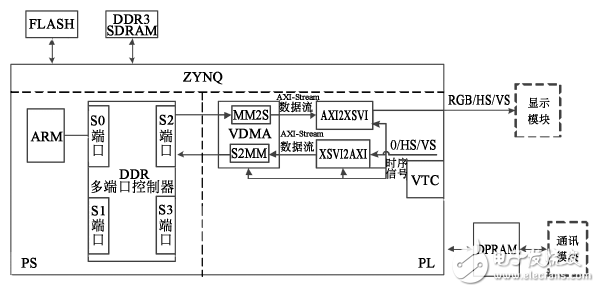

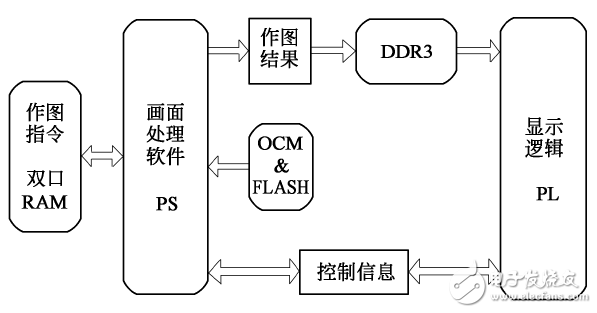

本文通過Zynq完成圖形生成與顯示功能,原理框圖如圖3所示,硬件模塊主要包括Zynq、DDR3SDRAM、FLASH、雙口RAM 等.正常工作時PS中的ARM 內核根據從雙口RAM 中接收到的繪圖指令和參數完成繪圖算法,將圖形數據寫入DDR3SDRAM 存儲器中.PL 從DDR3中讀出圖形數據進行顯示,并對DDR3SDRAM中的圖形數據進行清屏處理。

圖3 Zynq圖形生成原理框圖

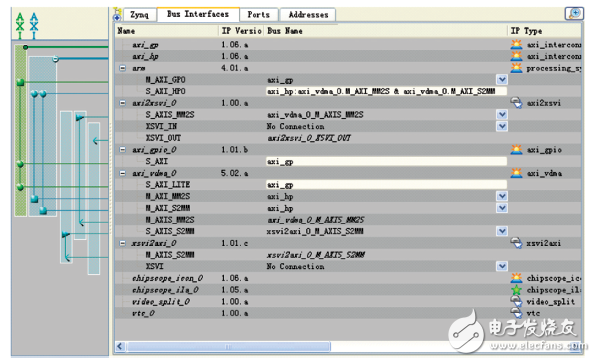

3.1.2 Zynq硬件平臺設計

本文通過Xilinx 的ISE14.2 軟件集成的XPS開發環境完成Zynq圖形生成電路的硬件平臺設計.利用XPS可以快速地對Zynq系統內的各種硬件資源進行定制設計,包括存儲器、外設、ARM 處理器、系統IP和用戶IP等.Zynq硬件平臺結構圖見圖4所示.

圖4 Zynq硬件結構圖

本文在Zynq中的PL 部分應用了VDMA、AXI2XSVI、XSVI2AXI、VTC等幾個IP核,其中VDMA 用于從DDR3SDRAM 中讀出圖形數據,同時向DDR3SDRAM 中寫入全零數據以達到清屏目的.AXI2XSVI用于將AXIGStream 數據流用行、場同步信號進行區隔,供外部顯示模塊進行顯示.XSVI2AXI用于將帶有行場同步信號的視頻數據轉換成AXIGStream 數據流.VTC 用于生成系統運行所需時序信號.對VTC根據顯示時序進行修改,系統即可產生多種分辨率圖形畫面。

3.1.3 圖形緩沖設計

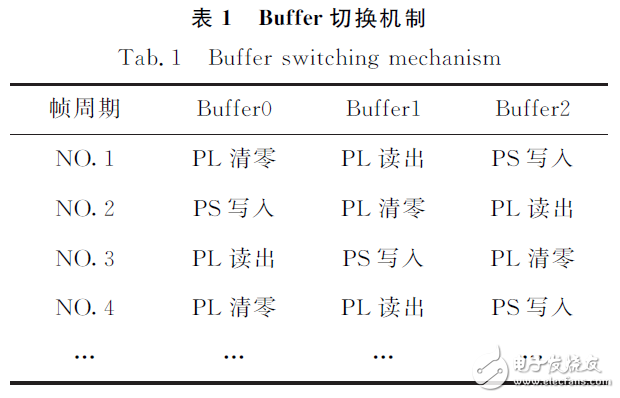

本文中對DDR3SDRAM 幀存的操作包括3種類型:PS寫入、PL讀取、PL清零.清零從本質上說也是一種寫入操作,寫入的是全零數據.讀取和寫入請求通過DDR 控制器中的調度機制和仲裁策略分別在不同時刻得以響應,得益于DDR3SDRAM 的高速高帶寬優勢,外部可以同時進行多個通道的讀寫操作.針對本文中DDR3SDRAM 的3種操作類型,在DDR3幀存中設置了3個緩沖區,分別為buffer0,buffer1,buffer2,相應地,VDMA 中的framebuffer數目也設置為3.buffer的切換機制如表1所示.

這種三緩沖切換機制保證了寫入的都是已清零完成的buffer,清零的都是已讀出完成的buffer,讀出的都是已寫入完成的buffer。

根據buffer切換機制,VDMA 中的S2MM和MM2S通道分別以指定的buffer為操作對象.初始化狀態下為每個buffer指定默認的操作模式,而后在每個幀周期內啟動VDMA 切換buffer操作模式,從而不間斷地輸出圖形數據。

3.2 軟件設計

3.2.1 Zynq系統軟件

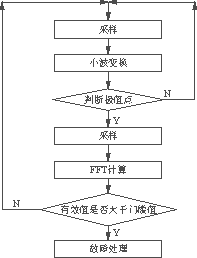

系統繪圖時,根據雙口RAM 提供的畫面內容要求,啟動繪圖任務,并將繪圖結果保存下來.顯示工作完全由PL內部的顯示邏輯負責,顯示邏輯從顯存中讀取顯示數據,按照標準時序送至顯示接口.圖形軟件的接口關系如圖5所示.

圖5 圖形生成軟件接口示意圖

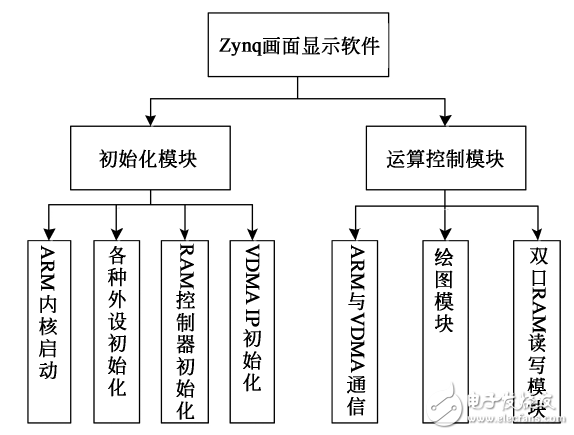

3.2.2 畫面顯示軟件

畫面顯示軟件主要包括初始化模塊和主模塊,結構如圖6所示.初始化模塊完成ARM 內核啟動;外設初始化信息加載;DDR3SDRAM、UART等設備初始化;VDMA 寄存器配置等初始化工作.運算控制模塊由雙口RAM 讀寫模塊;PS、PL 通信模塊以及繪圖模塊3部分組成,其中雙口RAM 讀寫模塊主要負責從雙口RAM中讀取繪圖指令數據,為繪圖模塊提供必要的繪圖參數;PS、PL通信模塊負責ARM 內核與VDMA的通信,切換緩存;繪圖模塊完成分配的繪圖任務,并將相應的計算結果,也即對應的像素點信息寫入DDR3SDRAM 中。

圖6 圖形生成軟件結構圖

4 實驗與對比

4.1 實驗過程

在實驗驗證階段,分別采用自主開發的Zynq圖形生成模塊和DSP圖形生成模塊作為實驗和比較對象.其中,Zynq 圖形生成模塊采用的Zynq器件型號為XC7Z020,集成的ARM 處理器頻率為667MHz,采用的DDR3SDRAM 器件型號為MICRO公司的MT41J128M16,時鐘頻率設置為533MHz.DSP圖形生成模塊采用的DSP器件型號為AD 公司TigerSHARC 系列的TS201,主頻設置為520MHz。

為了全面驗證Zynq平臺的圖形生成性能,本文針對幾種常規分辨率機載顯示器,對兩種平臺的圖形生成時間和幀率分別進行對比測試.機載顯示器常規分辨率有640×480、600×600、1024×768等幾種,每種分辨率下具體圖形生成時間和幀率與圖形內容和復雜度有關,本文選取常用的典型圖形作為測試對象,每幅圖形均包含了直線、圓弧、矩形、字符、數字、符號等內容,如圖7所示。

圖7 測試圖形

以1024×768 分辨率的EFIS 畫面為例,Zynq平臺實時生成圖形數據并送至外部監視器顯示的示意圖如圖8所示.

圖8 Zynq平臺1024×768分辨率圖形生成示例

4.2 實驗結果

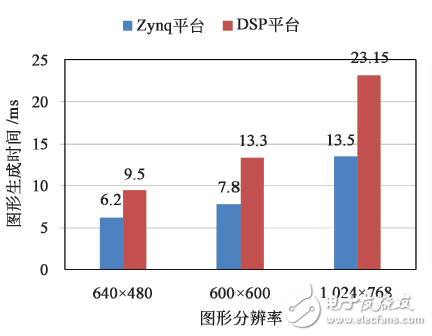

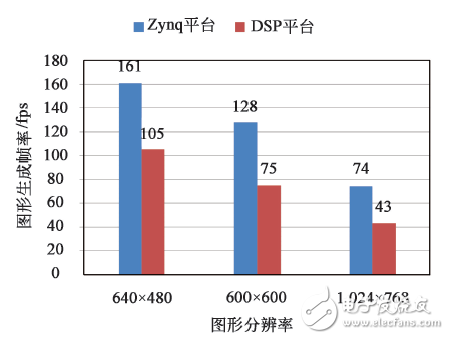

針對3種分辨率典型圖形畫面,Zynq平臺和DSP平臺圖形生成時間和幀率對比分別如圖9和圖10所示.

圖9 圖形生成時間對比

圖10 圖形生成幀率對比

圖形生成時間包括圖形算法運算時間和圖形數據寫幀存時間.在進行圖形運算處理時,針對Zynq平臺的特點采取了一系列的優化算法,圖形運算時間小于DSP平臺.另外,Zynq平臺采用的是DDR3SDRAM 幀存,操作速率遠高于DSP平臺采用的SRAM 幀存,因此寫幀存時間遠小于DSP平臺.由圖9和圖10可見,在繪制分辨率相同的同一圖形時,Zynq平臺圖形生成時間均小于DSP平臺,幀率均高于DSP平臺.在繪制多種分辨率圖形畫面,Zynq平臺幀率均超越60 Hz,滿足了機載顯示器的實時顯示要求。

5 結論

針對機載液晶顯示器低功耗、小型化的應用需求,提出了一種基于Zynq的圖形生成電路.運用Zynq器件集成的ARM CortexGA9內核作為核心繪圖部件,外部高速DDR3存儲器作為圖形幀存,對幀存采取三緩沖機制進行數據緩沖處理,配合可編程邏輯資源,可完成多種分辨率圖形的實時生成.對Zynq平臺和DSP平臺在多種分辨率下典型畫面的圖形生成時間和幀率進行了對比測試,測試結果表明,Zynq平臺性能優于DSP平臺.在生成1024×768分辨率的EFIS圖形畫面時,Zynq平臺圖形幀率可達74fps,滿足機載顯示器實時顯示需求。

電子發燒友App

電子發燒友App

評論