什么是ADC

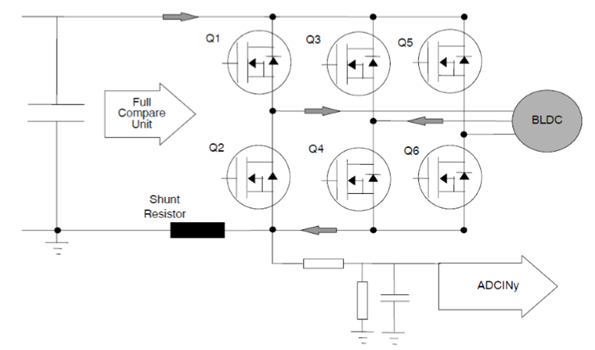

ADC,Analog-to-Digital Converter的縮寫,指模/數(shù)轉(zhuǎn)換器或者模數(shù)轉(zhuǎn)換器。是指將連續(xù)變化的模擬信號轉(zhuǎn)換為離散的數(shù)字信號的器件。真實世界的模擬信號,例如溫度、壓力、聲音或者圖像等,需要轉(zhuǎn)換成更容易儲存、處理和發(fā)射的數(shù)字形式。模/數(shù)轉(zhuǎn)換器可以實現(xiàn)這個功能,在各種不同的產(chǎn)品中都可以找到它的身影。

與之相對應的DAC,Digital-to-Analog Converter,它是ADC模數(shù)轉(zhuǎn)換的逆向過程。

ADC最早用于對無線信號向數(shù)字信號轉(zhuǎn)換。如電視信號,長短播電臺發(fā)接收等。

數(shù)字輸出選擇

1.高端儀表促進了更快的ADC速度和更多的通道數(shù)與密度,設計者必須評估轉(zhuǎn)換器的輸出格式,以及基本的轉(zhuǎn)換性能。

2.主要的輸出選項是CMOS(互補金屬氧化物半導體)、LVDS(低壓差分信令),以及CML(電流模式邏輯)。

3.要考慮的問題包括:功耗、瞬變、數(shù)據(jù)與時鐘的變形,以及對噪聲的抑制能力。

4.對于布局的考慮也是轉(zhuǎn)換輸出選擇中的一個方面,尤其當采用LVDS技術(shù)時。

當設計者有多種ADC選擇時,他們必須考慮采用哪種類型的數(shù)字數(shù)據(jù)輸出:CMOS(互補金屬氧化物半導體)、LVDS(低壓差分信令),還是CML(電流模式邏輯)。ADC中所采用的每種數(shù)字輸出類型都各有優(yōu)缺點,設計者應結(jié)合自己的應用來考慮。這些因素取決于ADC的采樣速率與分辨率、輸出數(shù)據(jù)速率,以及系統(tǒng)設計的功率要求,等等。

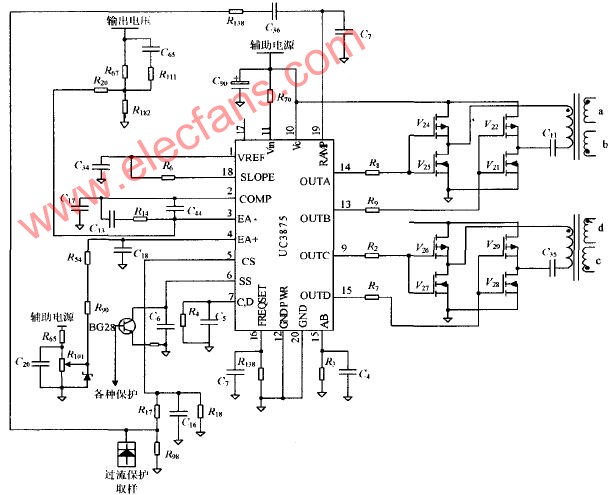

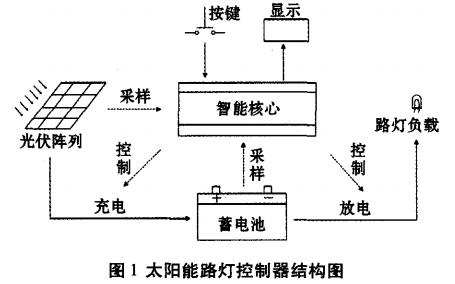

ADC0809采樣控制電路設計

一、實驗目的

學習用狀態(tài)機實現(xiàn)A/D轉(zhuǎn)換器ADC0809的采樣控制電路。

二、實驗內(nèi)容

利用QuartusⅡ?qū)崿F(xiàn)A/D轉(zhuǎn)換器ADC0809的采樣控制電路狀態(tài)機設計;給出仿真波形。最后進行引腳鎖定并進行測試,硬件驗證設計電路對ADC0809的控制功能。

三、實驗儀器與器材

計算機1臺,GW48-PK2S實驗箱1臺,QuartusⅡ6.0 1套。

四、實驗

用VHDL 設計的狀態(tài)機的一般結(jié)構(gòu)有以下幾部分組成:

1. 說明部分

說明部分中有新數(shù)據(jù)類型TYPE 的定義及其狀態(tài)類型(狀態(tài)名)和在此新數(shù)據(jù)類型下定義的狀態(tài)變量。狀態(tài)類型一般用枚舉類型,其中每一個狀態(tài)名可任意選取。但為了便于辨認和含義明確,狀態(tài)名最好有明顯的解釋性意義。狀態(tài)變量應定義為信號,便于信息傳遞。說明部分一般放在ARCHITECTURE 和BEGIN之間。

2. 主控時序進程:

狀態(tài)機是隨外部時鐘信號以同步時序方式工作的,因此狀態(tài)機中必須包含一個對工作時鐘信號敏感的進程作為狀態(tài)機的“驅(qū)動泵”。當時鐘發(fā)生有效跳變時,狀態(tài)機的狀態(tài)才發(fā)生變化。狀態(tài)機的下一狀態(tài)(包括再次進入本狀態(tài))僅僅取決于時鐘信號的到來。一般地,主控時序進程不負責進入的下一狀態(tài)的具體狀態(tài)取值。當時鐘的有效跳變到來時,時序進程只是機械地將代表下一狀態(tài)的信號next_state 中的內(nèi)容送入代表本狀態(tài)的信current_state 中,而信號next_state 中的內(nèi)容完全由其它的進程根據(jù)實際情況來決定。當然此進程中也可以放置一些同步或異步清零、置位方面的控制信號。總體來說,主控時序進程的設計比較固定、單一和簡單。

3. 主控組合進程:

主控組合進程的任務是根據(jù)外部輸入的控制信號(包括來自狀態(tài)機外部的信號和來自狀態(tài)機內(nèi)部其它非主控的組合或時序進程的信號),或(和)當前狀態(tài)的狀態(tài)值確定下一狀態(tài)(next_state)的取向,即next_state的取值內(nèi)容,以及確定對外輸出或?qū)?nèi)部其它組合或時序進程輸出控制信號的內(nèi)容。

4. 普通組合進程

用于配合狀態(tài)機工作的其它組合進程,如為了完成某種算法的進程。

5. 普通時序進程

用于配合狀態(tài)機工作的其它時序進程,如為了穩(wěn)定輸出設置的數(shù)據(jù)鎖存器等。一個狀態(tài)機的最簡結(jié)構(gòu)應至少由兩個進程構(gòu)成(也有單進程狀態(tài)機,但并不常用)即一個主控時序進程和一個主控組合進程,一個進程作“驅(qū)動泵”,描述時序邏輯,包括狀態(tài)寄存器的工作和寄存器狀態(tài)的輸出;另一個進程描述組合邏輯,包括進程間狀態(tài)值的傳遞邏輯以及狀態(tài)轉(zhuǎn)換值的輸出。當然必要時還可以引入第3 個和第4 個進程,以完成其它的邏輯功能。

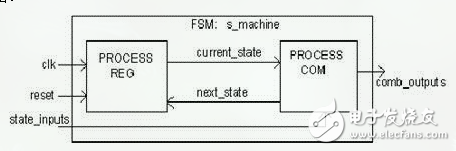

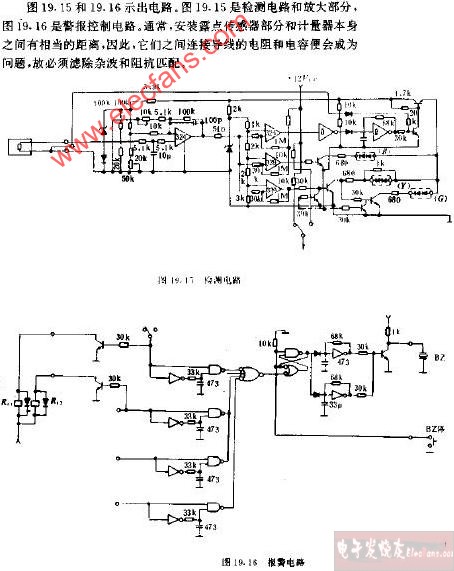

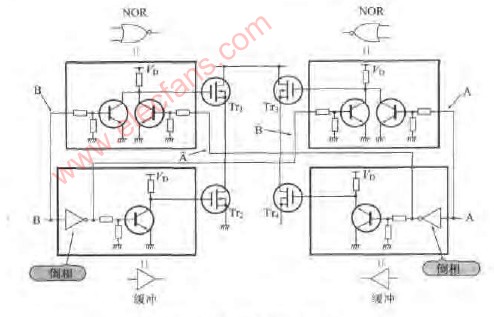

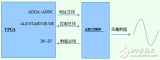

從一般意義上說進程間是并行運行的,但由于敏感信號的設置不同以及電路的延遲,在時序上進程間的動作是有先后的。在設計中,如果希望輸出的信號具有寄存器鎖存功能,則需要為此輸出寫第3 個進程,并把clk 和reset信號放入敏感信號表中。用于進程間信息傳遞的信號current_state 和next_state ,在狀態(tài)機設計中稱為反饋信號。狀態(tài)機運行中,信號傳遞的反饋機制的作用是實現(xiàn)當前狀態(tài)的存儲和下一個狀態(tài)的譯碼設定等功能。在VHDL中可以有兩種方式來創(chuàng)建反饋機制,即使用信號的方式和使用變量的方式,通常傾向于使用信號的方式。附圖8-1為一般狀態(tài)機結(jié)構(gòu)圖。

圖8-1 一般狀態(tài)機結(jié)構(gòu)框圖工作示意圖

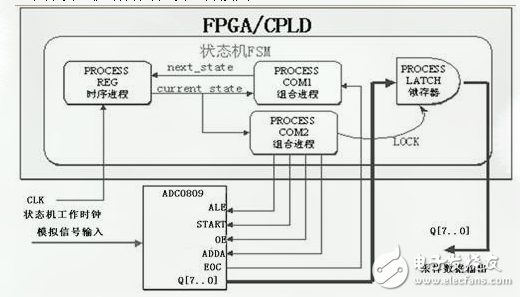

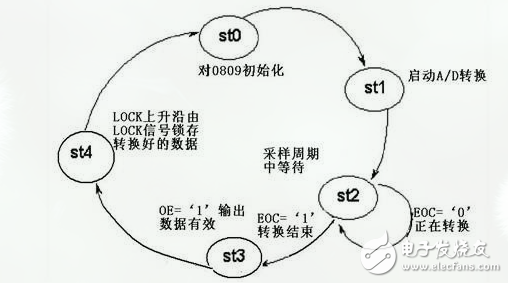

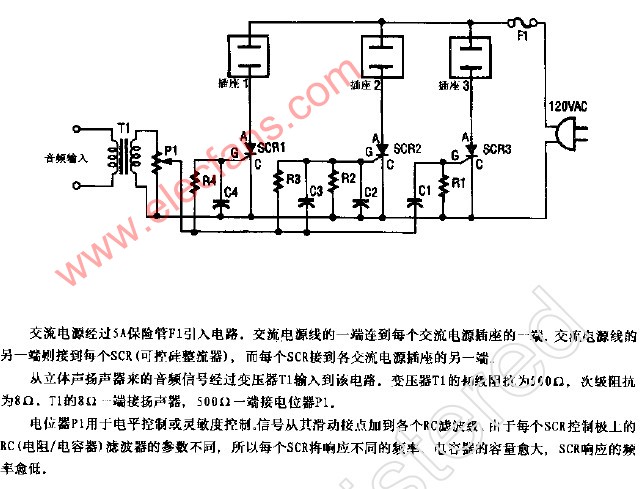

附圖8-2和8-3為控制ADC0809采樣狀態(tài)機結(jié)構(gòu)圖和狀態(tài)轉(zhuǎn)換圖

圖8-2 采樣狀態(tài)機結(jié)構(gòu)框圖

設計提示:

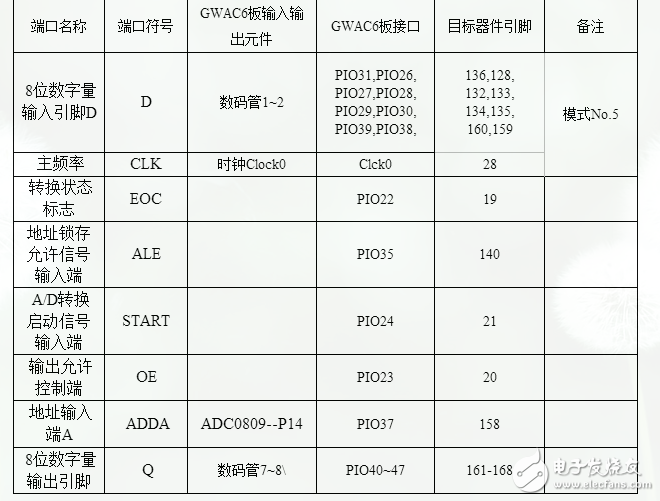

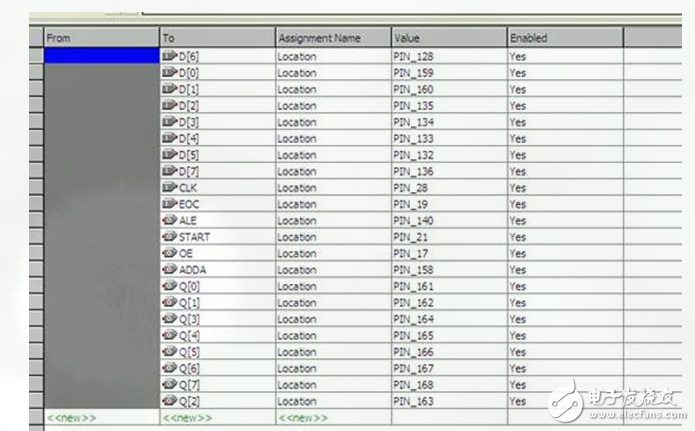

設目標器件是EP1C6Q240C8,建議選擇實驗電路結(jié)構(gòu)圖No.5(即結(jié)構(gòu)圖No.5A,附圖1-14,由該圖可見,ADC0809的轉(zhuǎn)換時鐘CLK已經(jīng)事先接有750KHz的頻率),將實驗系統(tǒng)左下角選擇插針處的“轉(zhuǎn)換結(jié)束”和“A/D使能”用跳線帽短接。下載目標文件后,可用螺絲刀旋轉(zhuǎn)實驗系統(tǒng)左下角的電位器,以便為ADC0809提供變化的待測模擬信號,這時數(shù)碼管8和7將顯示ADC0809采樣輸出并被鎖存的數(shù)字值(16進制)。

圖8-3 控制ADC0809采樣狀態(tài)圖

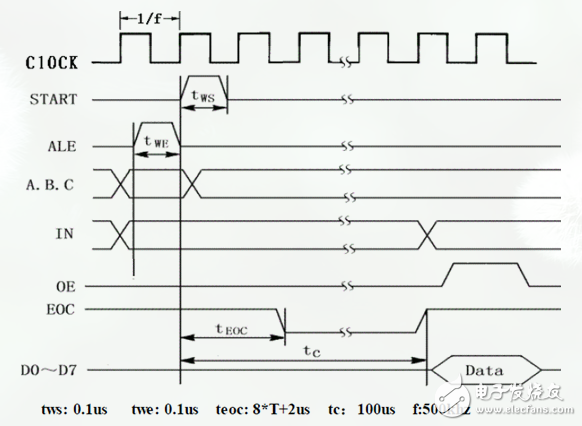

圖8-4 控制ADC0809采樣時序圖

五、實驗要求

根據(jù)以上的實驗內(nèi)容寫出實驗報告,包括程序設計、軟件編譯、仿真分析、硬件測試和實驗過程;設計程序、程序分析報告、仿真波形圖及其分析報告。

1. 設計思路

6. 由題意知,我們要設計一個電路與A/D轉(zhuǎn)換器ADC0809相連,通過接受時鐘輸入來決定狀態(tài),通過對不同狀態(tài)輸出不同的控制信號,實現(xiàn)對ADC0809的采樣控制,最終輸出穩(wěn)定的采樣電壓。本實驗中將設計如下進程。

設置兩個信號Current_State、Next_State,以便實現(xiàn)狀態(tài)的通知。

① 主控時序進程REG

總體設計思想:用REG控制整個采樣控制電路的狀態(tài),是整個電路的總指揮。

通過監(jiān)測ADC0809輸出的信號,實現(xiàn)不同狀態(tài)的轉(zhuǎn)換,進而控制不同不同的進程Process。

主控時序進程REG只輸出狀態(tài),只接收ST1。

當狀態(tài)為ST0的時候,開始新一輪的采樣;

當接收ST1的時候,通知COM2將采樣數(shù)據(jù)鎖存,輸出。

進程REG對信號:CLK、Next_State信號敏感

② 組合進程COM1

總體設計思想:用COM1實現(xiàn)COM2對REG的通知,是整個電路的傳令兵;用COM2控制整個電路,是整個電路狀態(tài)改變的具體執(zhí)行者。

。

當EOC=1的時候,通知REG,以便改變電路狀態(tài)。

進程COM1對信號Current_State和EOC敏感

③ 進程LATCH

總體設計思想:用LATCH來鎖存轉(zhuǎn)換好的數(shù)據(jù),并控制數(shù)據(jù)的輸出。

進程LATCH對信號LOCK,REGL敏感

程序設計

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY ADCINT IS

PORT(D :INSTD_LOGIC_VECTOR(7DOWNTO0);--來自0809轉(zhuǎn)換好的8位數(shù)據(jù)

CLK:INSTD_LOGIC; --狀態(tài)機工作時鐘

EOC:INSTD_LOGIC; --轉(zhuǎn)換狀態(tài)指示,低電平表示正在轉(zhuǎn)換

ALE:OUTSTD_LOGIC; --8個模擬信號通道地址鎖存信號

START:OUTSTD_LOGIC; --轉(zhuǎn)換開始信號

OE:OUTSTD_LOGIC; --數(shù)據(jù)輸出3態(tài)控制信號

ADDA:OUTSTD_LOGIC; --信號通道最低位控制信號

LOCK0:OUTSTD_LOGIC; --觀察數(shù)據(jù)鎖存時鐘

LED:OUTSTD_LOGIC; --用來指示仿真程序是否正確

-- LED2: OUT STD_LOGIC; --2用來指示仿真程序是否正確

Q :OUTSTD_LOGIC_VECTOR(7DOWNTO0)--8位數(shù)據(jù)輸出

);

END ADCINT;

ARCHITECTURE behav OF ADCINT IS

TYPE states IS(st0,st1,st2,st3,st4); --定義各狀態(tài)子類型

SIGNAL current_state , next_state : states := st0;

SIGNAL REGL :STD_LOGIC_VECTOR(7DOWNTO0);

SIGNAL LOCK :STD_LOGIC; --轉(zhuǎn)換后數(shù)據(jù)輸出鎖存時鐘信號

BEGIN

ADDA 《= ‘1’;--當ADDA《=‘0’,模擬信號進入通道IN0,當ADDA《=‘1’,則進入通道IN1

Q 《= REGL; LOCK0 《= LOCK;

------------------進程REG---------------------

--用REG控制整個采樣控制電路的狀態(tài),是整個電路的總指揮。

PROCESS(CLK)

BEGIN

IF CLK=‘1’ and CLK‘eventTHEN -- 檢測時鐘上升沿

--LED《=’0‘;

IF next_state=st0 THEN -- 初始化狀態(tài)機

current_state《=st0;

ELSIF next_state=st1 THEN --開始轉(zhuǎn)換(st1)

current_state《=st1;

ELSIF next_state=st2 THEN --等待轉(zhuǎn)化完畢,檢測EOC是否為高電平

current_state《=st2;

ELSIF next_state=st3 THEN

-- LED《=’1‘;

current_state《=st3;

ELSIF next_state=st4 THEN

current_state《=st4;

ENDIF;

ENDIF;

ENDPROCESS;

------------------進程COM2---------------------

--用COM2控制整個電路,是整個電路狀態(tài)改變的具體執(zhí)行者。

PROCESS(current_state,EOC)

VARIABLE First_EOC :STD_LOGIC;

BEGIN

--LED2《=’0‘;

IF current_state=st0 THEN -- 初始化狀態(tài)機

ALE《=’1‘;

START《=’0‘;

OE《=’0‘;

LOCK《=’0‘;

next_state《=st1;

ELSIF current_state=st1 THEN --開始轉(zhuǎn)換(st1)

START《=’1‘;

ALE《=’0‘;

--IF EOC=’0‘ THEN -- 轉(zhuǎn)換結(jié)束

next_state《=st2;

First_EOC:=EOC;--在狀態(tài)1記錄EOC,以便后面判斷AD是否開始轉(zhuǎn)換

--END IF;

ELSIF current_state=st2 THEN --等待轉(zhuǎn)化完畢,檢測EOC是否為高電平

START《=’0‘;

OE《=’0‘;

if ’1‘=(First_EOC XOR EOC)then

IF EOC=’1‘ THEN

-- IF EOC=’1‘ THEN

next_state《=st3;

-- END IF;

-- else

-- next_state《=st2;

ENDIF;

else

next_state《=st2;

ENDIF;

ELSIF current_state=st3 THEN

--LED2《=’1‘;

IF EOC=’1‘ THEN -- 轉(zhuǎn)換結(jié)束

OE《=’1‘;

next_state《=st4;

ELSE

OE《=’0‘;

ENDIF;

ELSIF current_state=st4 THEN

OE《=’0‘;

LOCK《=’1‘;

next_state《=st0; --開啟下一輪新的轉(zhuǎn)換

ENDIF;

ENDPROCESS;

------------------進程LATCH---------------------

--用來控制電路的輸出

PROCESS(LOCK,REGL)

VARIABLE cq :std_logic_vector(7DOWNTO0);--用來保存數(shù)值

BEGIN

IF LOCK=’0‘ THEN

cq:=D;

ELSIF LOCK=’1‘ THEN

REGL《=cq;

ENDIF;

ENDPROCESS;

ENDARCHITECTURE behav;

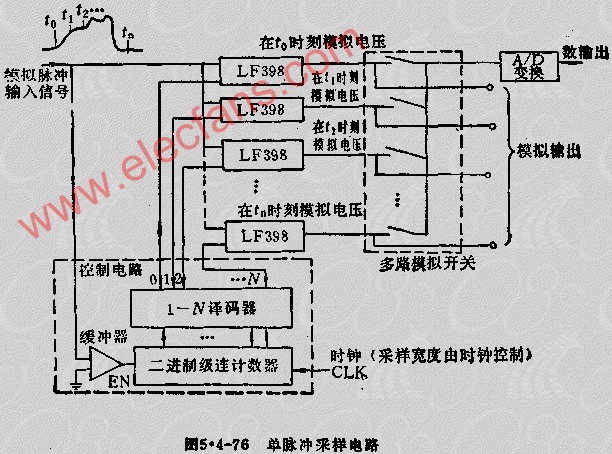

2. 仿真分析

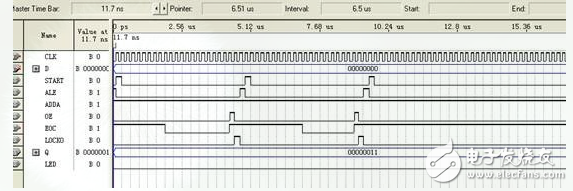

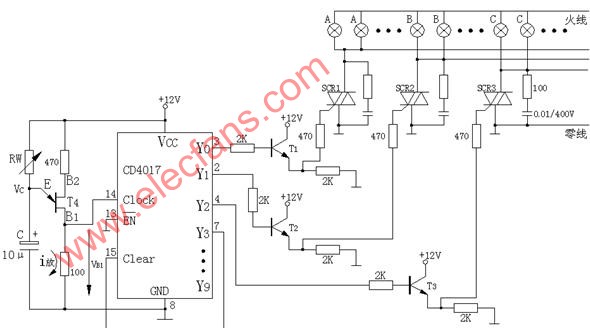

圖8-5 仿真波形圖

由8-5可知,仿真波形和圖8-4控制ADC0809采樣時序圖一致。

3. 硬件測試和實驗過程

表1-1 ADCINT在GWAC6板上目標芯片EP1C6Q240C8的引腳鎖定信息

電子發(fā)燒友App

電子發(fā)燒友App

評論