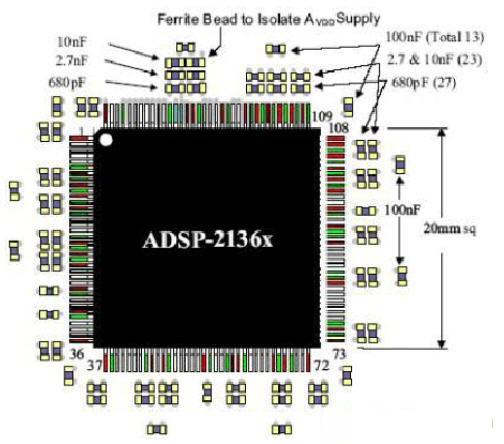

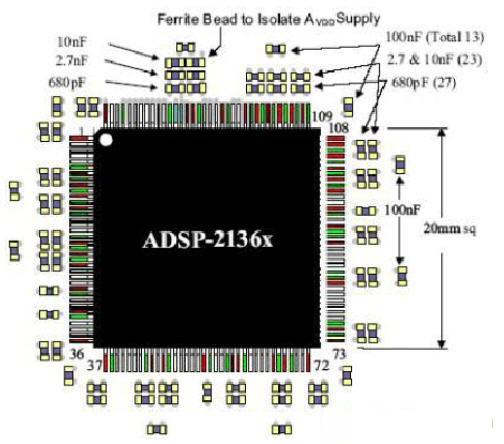

對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠,最外層放置容值最大的。但是,所有對該芯片去耦的電容都盡量靠近芯片。

2017-02-09 09:36:54 8586

8586

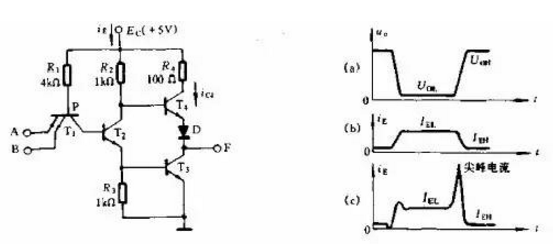

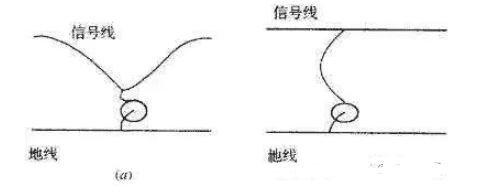

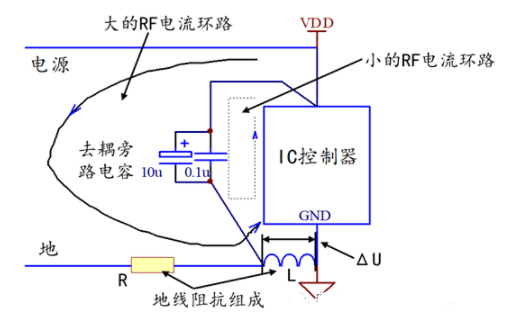

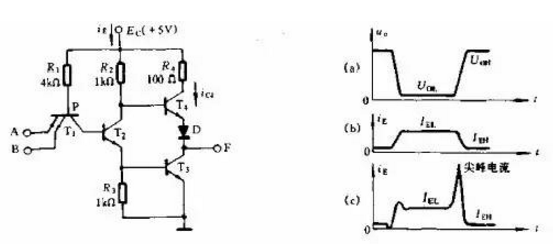

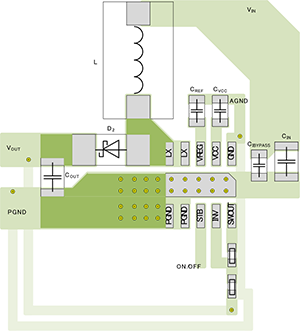

圖(a)所示,理論上電源電流的波形如右圖(b),而實際的電源電流保險如右圖(c)。由圖(c)可以看出在輸出由低電平轉換到高電平時電源電流有一個短暫而幅度很大的尖峰。尖峰電源電流的波形隨所用器件的類型和輸出端所接的電容負載而異。 產生尖峰電流的主

2018-01-12 09:05:20 6951

6951

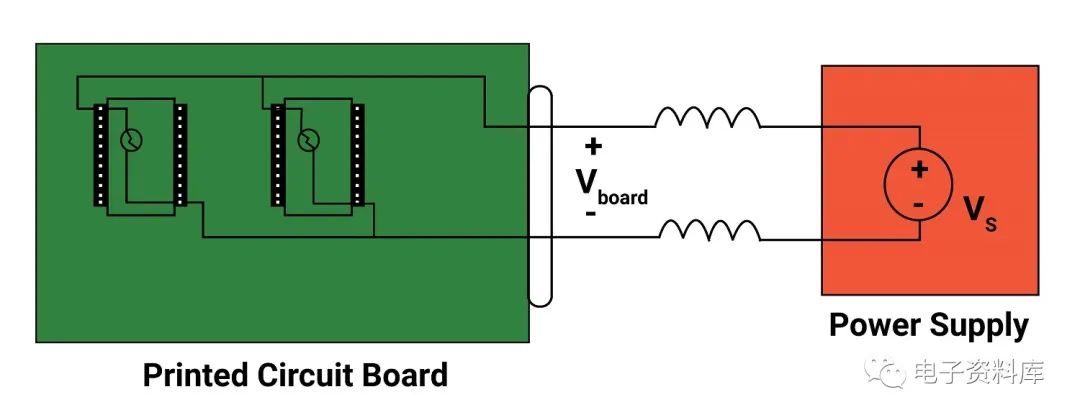

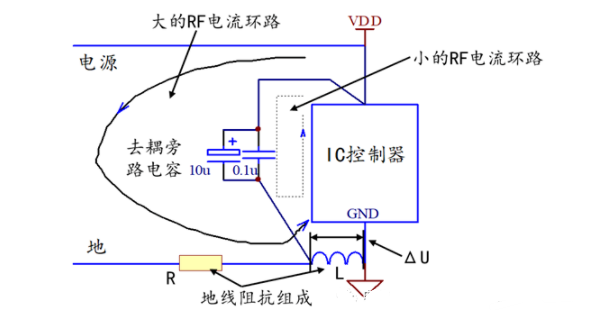

我們知道濾波電容被放在電源和地之間,主要有兩個作用:(1)為處于快速開關狀態下的IC供電;(2)減小電源和地之間的噪聲 。所有濾波電容選擇的策略都會采用梯次電容值配置,大電容有足量電量儲備,而小電容

2021-04-04 10:57:00 3006

3006

去耦是一種基于頻率從復合信號中分離信號分量的方法。因此,了解應該隔離哪個頻率范圍對于準確地在系統中放置電容器很重要。

2023-09-28 14:21:01 639

639

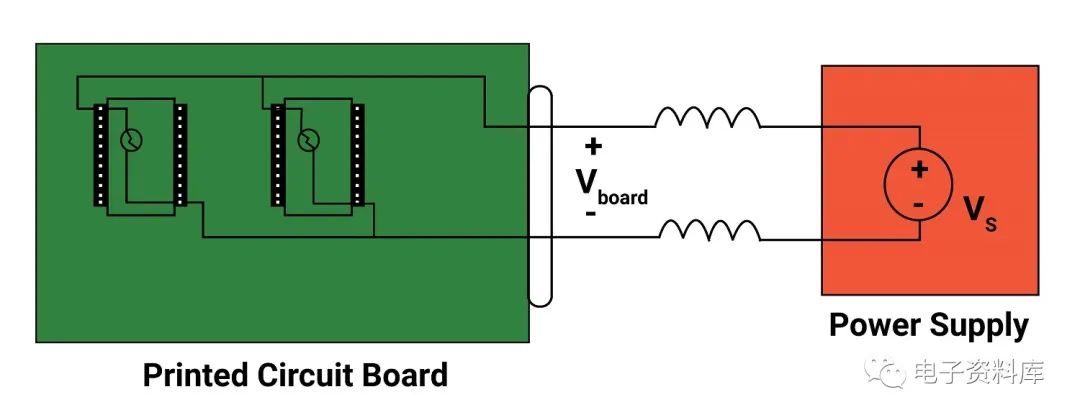

我們都知道,完整的電源系統包括了VRM、PCB、去耦電容器件、封裝寄生參數和Sink的寄生參數。

2024-02-23 10:04:32 240

240

為什么設計PCB電容要就近擺放呢,等看了資料后就能了解一些,可是網上的資料很雜散,很少能找到一個很全方面講解的。下面這些內容是我轉載的一篇關于電容去耦半徑的講解,相信你看了之后可以很牛x的回答和避免類似問題的發生。

2016-07-26 11:30:51 5597

5597 濾波電容:用在電源整流電路中,用來濾除交流成分,使輸出的直流更平滑。去耦電容:用在放大電路中不需要交流的地方,用來消除自激,使放大器穩定工作?旁路電容:用在有電阻連接時,接在電阻兩端使交流信號順利

2019-08-26 09:41:50

PCB PDN design guidelines (PCB電源完整性設計指導) ------PCB平面圖指南一、 不帶電源平面1.為每個有源設備至少提供一個“本地”去耦電容器,并為板上分布的每個

2021-12-28 06:07:45

較大,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的 PCB 層疊,有助于將因電路的電流需求而產生的電壓紋波降至最低。例如,根據所用的去耦策略,如果系統設計的開關電流為

2020-11-18 09:18:02

,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的 PCB 層疊,有助于將因電路的電流需求而產生的電壓紋波降至最低。例如,根據所用的去耦策略,如果系統設計的開關電流為 1

2022-05-07 11:30:38

對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠,最外層放置容值最大的。但是,所有對該芯片去耦的電容都盡量

2018-09-18 15:56:26

的傳播速度為166ps/inch,則波長為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于2.4厘米。 本例中的電容只能對它周圍2.4厘米范圍內的電源噪聲進行補償,即它的去耦半徑

2018-08-28 14:41:28

等于2.4厘米。 本例中的電容只能對它周圍2.4厘米范圍內的電源噪聲進行補償,即它的去耦半徑2.4厘米。不同的電容,諧振頻率不同,去耦半徑也不同。對于大電容,因為其諧振頻率很低,對應的波長非常長,因而去耦

2018-09-12 10:46:08

上的傳播速度為166ps/inch,則波長為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于2.4厘米。 本例中的電容只能對它周圍2.4厘米范圍內的電源噪聲進行補償,即它的去耦半徑

2018-09-17 17:40:22

PCB抗干擾設計,電源線、地線、去耦電容如何配置?

2021-03-17 07:04:11

什么是PCB中的板級去耦呢?如何設計板級去耦。

2021-01-22 06:28:39

電容在集成電路電源和地之間的有兩個作用:一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲。數字電路中典型的去耦電容值是 0.1μF。這個電容的分布電感的典型值是 5μH。0.1μF 的去耦

2011-02-24 14:30:32

7.95ps。假設信號在電路板上的傳播速度為166ps/inch,則波長為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于2.4厘米。 本例中的電容只能對它周圍2.4厘米范圍內的電源噪聲

2023-04-11 16:26:00

旁路電容是把電源或者輸入信號中的交流分量的干擾作為濾除對象;去耦電容是芯片的電源管腳,兩者有啥區別了?詳細請看附件(內有福利哦~~)

2021-09-08 10:02:18

` 本帖最后由 eehome 于 2013-1-5 10:08 編輯

去耦電容和旁路電容的區別`

2012-08-14 11:49:42

信號完整性之去耦電容與旁路電容

2019-11-19 14:52:05

去耦電容分為哪幾種?如何去放置去耦電容呢?在設計中如何防止上電及正常工作時出現總線沖突呢?

2021-11-03 07:17:04

的有兩個作用:一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲。數字電路中典型的去耦電容值是 0.1μF。這個電容的分布電感的典型值是5μH。0.1μF的去耦電容有5μH的分布電感,它的并行

2012-03-08 23:42:09

去耦電容和旁路電容的區別詳解

2017-01-19 09:06:12

電子線路中的同一個電容,有時候會稱它去耦電容,有時候又會稱它為旁路電容。 電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,但是,當我們從不同的角度去看時,它所起的作用是不同的,所以才有

2021-05-25 06:14:19

的電感很小。在暫態過程中,該電容器可在非常短的時間內向器件提供超大量的電流。 未采用去耦電容的器件無法提供暫態電流,因此放大器的內部節點會下垂(通常稱為干擾)。無去耦電容的器件其內部電源干擾會導致器件

2018-09-20 15:44:35

問題。圖 1:采用去耦和不采用去耦的緩沖電路(測量結果)圖 2 闡述了為什么去耦非常重要。需要注意的是,電源線跡的電感將限制暫態電流。 去耦電容與器件非常接近,因此電流路徑的電感很小。在暫態過程中,該電容

2018-12-26 14:19:56

去耦電容在PCB板設計中的應用在板設計中應充分考慮電磁兼容方面的問題,合理地使用去耦電容在PCB板防止電磁干擾中具有重要作用, 本文就去耦電容的容量及其具體應用作了較為全面、詳細的敘述,同時還介紹了增強去耦電容效果的一些實用方法。[hide][/hide]

2009-12-09 14:08:29

去耦電容的有效使用方法之一是用多個(而非1個)電容進行去耦。使用多個電容時,使用相同容值的電容時和交織使用不同容值的電容時,效果是不同的。

2019-08-02 06:56:29

去耦和旁路概述:旁路:空載時為了得到想要的輸出信號而加的電容。去耦:帶載時為了不讓負載對前級信號產生影響而加的電容。 耦合的產生:電路中總是存在驅動的源和被驅動的負載。如果負載電容比較大,驅動電路

2015-08-26 21:56:00

何為去耦技術?正確去耦有何必要性?去耦電容有哪些類型?不良去耦技術對性能的影響是什么

2021-03-11 08:14:14

1.電源附近去耦電容的選擇很多IC管腳的VCC會增加一個0.1uf的去耦電容,因為電容的濾波曲線在谷底最低的位置濾波效果最好。當IC內部的邏輯門頻率是是10MHz-50MHz的時候,0.1uf電容

2021-12-31 07:29:16

在高速時鐘電路中,尤其要注意元件的RF去耦問題。究其原因,主要是因為元件會把一部分能量耦合到電源/地系統之中。這些能量以共模或差模RF的形式傳播到其他部件中。陶瓷片電容需要比時鐘電路要求的自激

2018-11-27 15:19:23

請問去耦電容的選擇按照這個圖上的規則來選對嗎

2018-11-19 11:21:51

一個原型設計電路板省去了比較麻煩的去耦電容器;但獲得的任何結果都無法與預期結果相匹配。最后,添加一個去耦電容器,問題解決了。什么我們需要使用去耦電容器?它的作用到底是什么?

2021-04-02 07:46:38

在做高速電路設計的時候,為什么要有那么多去耦電容?到底什么是去耦?到底需要多大的去耦電容呢?為什么是很多個小電容并聯而不是用一個大電容(值是一樣大的啊)?為什么說小電容要靠近電源管腳而大電容可以

2019-05-07 06:22:23

去耦旁路電路,不同規格的電容在PCB布局時該怎么擺

2021-03-17 07:33:04

。 旁路電容,也叫bypass,是把輸入信號中的高頻成分作為濾除對象。 去耦電容,也叫decoupling,也稱退耦電容,是把輸出信號的干擾作為濾除對象。 可以看到,旁路電容和去耦電容的作用都是濾波

2021-01-11 16:31:51

電容在高速 PCB 設計中起著重要的作用,通常也是 PCB 上用得最多的器件。在 PCB 中,電容通 常分為濾波電容、去耦電容、儲能電容等。 1 電源輸出電容,濾波電容 我們通常把電源模塊

2023-04-20 10:32:14

對于已經知道了電容的具體特性和適用范圍,以及去耦原理,那么就知道了去耦的具體方法了嗎?不是的,下面我們將講解一下,具體安裝到電路板上之后的去耦原理以及具體如何防止電容的準則!

2021-03-04 08:11:41

現在在畫一個ColdFire54455的板子,DDR2去耦電容這里有幾個不明白的問題,還望大家不吝賜教,萬分感激。DDR2我用的是MT47H32M16,官方Demo原理圖用的MT47H64M8,用了

2016-12-13 09:34:14

`各位大神,請問FPGA去耦電容如何布局、布線?1.根據文檔,一般去耦電容的數量都少于電源引腳,那么去耦電容要放到哪些管腳旁邊呢?2.以下三種方案哪種好?2.1電容放在PCB top層FPGA外圍

2017-08-22 14:57:10

想為cyclone V 系列的5CEFA7F27這款FPGA設計去耦電容電路,但是不知道該如何下手。參考了altera公司的一塊開發板,給出的FPGA的去耦電容電路如下所示,但是感覺這個去耦電容電路

2016-07-09 10:11:21

親愛的先生/女士,我們在我們的調制解調器板上使用兩個xc7k160t-1ffgi,基于我們使用xpe進行功率估算的邏輯利用率。根據UG483(PCB設計指南)遵循每個組的去耦電容器數量)。第17頁表

2020-08-17 10:48:12

概念層次,而旁路則只是一種途徑,一種手段,一種方法。二、如何判斷電路中的電容是去耦還是旁路?比如以下電路圖中的電容C1、C2、C3,你分得出誰是去耦電容,誰是旁路電容嗎?我們可以分別從電源模塊、IC1

2022-11-04 22:29:20

什么是PCB中的板級去耦呢?如何設計板級去耦?

2021-01-25 06:33:18

`關于去耦電容旁路電容的總結`

2012-08-20 14:01:15

的影響。形成懸浮地或是懸浮電源,在復雜的系統中完成各部分地線或是電源的協調匹配,有源器件在開關時產生的高頻開關噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個局部的直流電源給有源器件,以減少開關噪聲在

2020-12-02 09:34:28

怎么分清濾波電容、去耦電容、旁路電容?其實并不難~

2021-01-22 07:53:58

Walt Kester在上篇文章中,我們介紹了去耦的基礎知識及其在實現集成電路(IC)期望性能方面的重要性。在本篇文章中,我們將詳細探討用于去耦的基本電路元件——電容。實際電容及其寄生效應圖1所示為

2018-10-19 10:58:00

”和“去耦電容”:(有點抄百度的節奏) 一.定義和區別旁路(bypass)電容:是把輸入信號中的高頻成分作為濾除對象;去耦(decoupling)電容:也稱退耦電容,是把輸出信號的干擾作為濾除對象。去

2018-12-07 09:39:59

旁路電容是把輸入信號中的干擾作為濾除對象,而去耦電容是把輸出信號的干擾作為濾除對象,防止干擾信號返回電源。這應該是他們的本質區別。去耦電容相當于電池,避免由于電流的突變而使電壓下降,相當于濾紋波

2019-05-23 06:37:11

`經常有朋友搞不清這幾種電容的作用,看到一篇不錯的文章,特意和大家分享濾波電容、去耦電容、旁路電容作用濾波電容用在電源整流電路中,用來濾除交流成分。使輸出的直流更平滑。 去耦電容用在放大電路中不需要

2013-03-08 16:33:18

濾波電容用在電源整流電路中,用來濾除交流成分。使輸出的直流更平滑。 : 去耦電容用在放大電路中不需要交流的地方,用來消除自激,使放大器穩定工作。 旁路電容用在有電阻連接時,接在電阻兩端使交流信號順利

2012-04-04 23:29:40

在ug373“Virtex-6 FPGA PCB設計指南”v1.3中,不需要用于Vccaux和Vcco的去耦電容(表2-1至2-2),而在我讀過的早期版本中,數字并非都是零(我不記得確切的數字)。這些0與ug373以及ML605原理圖中的以下描述相矛盾。對此有什么正確的答案?

2020-06-08 11:03:50

瓷片電容、鉭電容、電解電容區別---電源設計中的去耦電容應用實例轉自:張飛實戰電子電源往往是我們在電路設計過程中最容易忽略的環節。其實,作為一款優秀的設計,電源設計應當是很重要的,它很大程度影響了

2021-11-11 08:12:14

。假設信號在電路板上的傳播速度為166ps/inch,則波長為47.9英寸。電容去耦半徑為47.9/50=0.958英寸,大約等于2.4厘米。 本例中的電容只能對它周圍2.4厘米范圍內的電源噪聲進行

2019-09-06 18:13:24

電容在集成電路電源和地之間的有兩個作用: 一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲。 數字電路中典型的去耦電容值是0.1μF。這個電容的分布電感的典型值是5μH。 0.1μF的去耦

2017-05-04 10:48:07

我知道在電源設計中,電源輸入與輸出都要濾波和去耦合,請問下怎么叫去耦電容?什么叫旁路電容啊??我知道概念,它們兩者區別在于:旁路電容是把輸入信號中的干擾信號去掉,而去耦電容是把輸出信號中的干擾信號去掉;但是我不知道具體怎么區分?難道左邊的是旁路電容,右邊的是去耦電容嗎?

2018-10-23 09:32:13

今天簡單跟大家講講PCB抄板的電阻與電容的電氣設計因素,導線電阻,通常導線的電流負載能力不成為什么問題;但是當導線很長而且電壓調節要求很嚴格時,歐姆電阻也許就是一個問題了

2011-06-23 11:18:19 1025

1025 2012-06-03 16:43:46 0

0 輸出級的T3、T4管短設計內同時導通。在與非門由輸出低電平轉向高電平的過程中,輸入電壓的負跳變在T2和T3的基極回路內產生很大的反向驅動電流,由于T3的飽和深度設計得比T2大,反向驅動電流將使T2首先脫離飽和而截止。

2017-11-27 16:08:38 5089

5089

數字電路輸出高電平時從電源拉出的電流Ioh和低電平輸出時灌入的電流Iol的大小一般是不同的,即:Iol>Ioh。以下圖的TTL與非門為例說明尖峰電流的形成。

2018-01-08 10:45:48 4383

4383

對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。

2018-12-28 13:53:33 4333

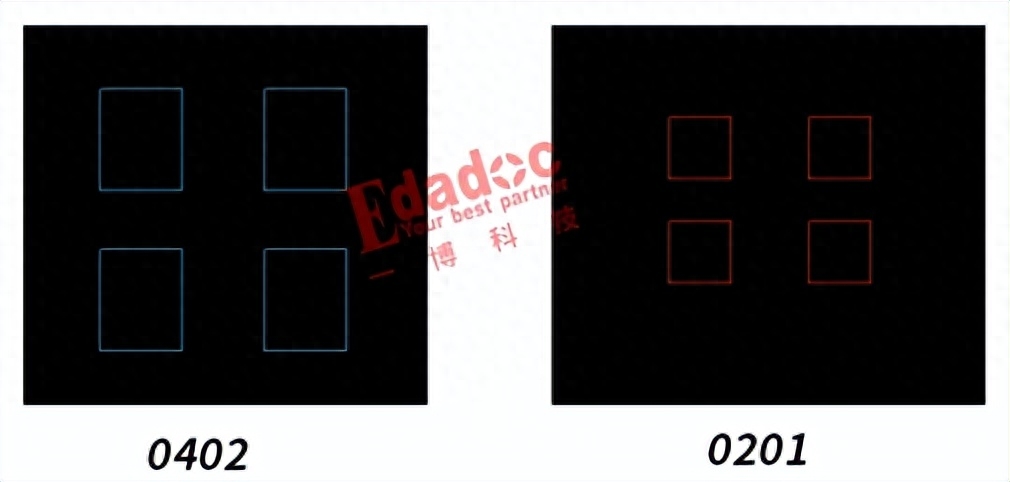

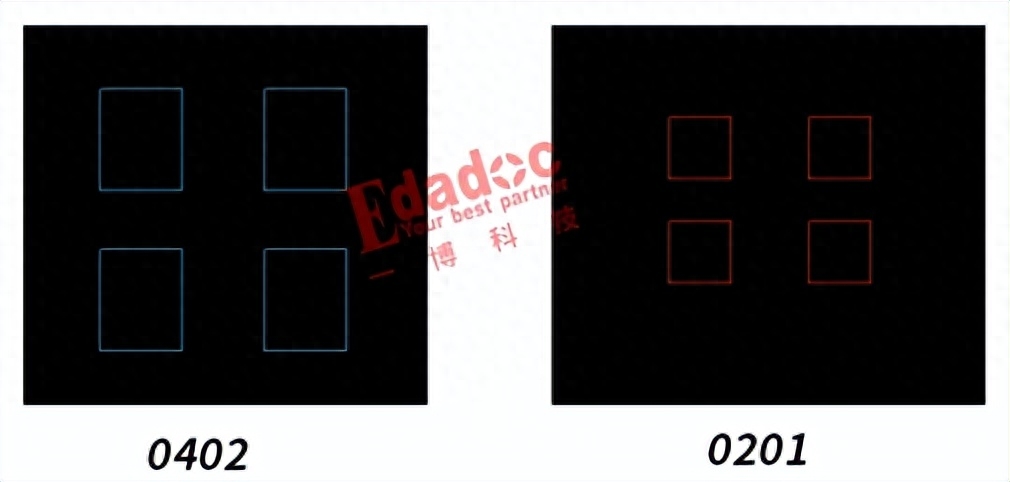

4333 在進行高速多層PCB設計時,關于電阻電容等器件的封裝的選擇的,主要依據是什么?

2019-05-24 16:36:07 2715

2715 需要考慮工作頻率,I/O的開關數量,每個Pin腳的容性負載,走線的特征阻抗, 結點的溫度,芯片內部的運算。

2019-06-14 11:55:36 4156

4156

我們使用的電容器我們的PCB設計與教室內置的電容有些不同。在設計電路板時,了解電容器類型的特性有助于規劃和設計。在使用通孔和表面貼裝設計時,您可以使用設計庫根據包括電容,介電類型,標稱值容差,額定電壓和溫度系數在內的屬性組合來選擇電容器。

2019-07-28 10:32:30 1358

1358 尖峰電流的形成是因為數字電路輸出高電平時從電源拉出的電流Ioh和低電平輸出時灌入的電流Iol的大小一般是不同的,即:Iol>Ioh。

2019-08-26 10:15:16 337

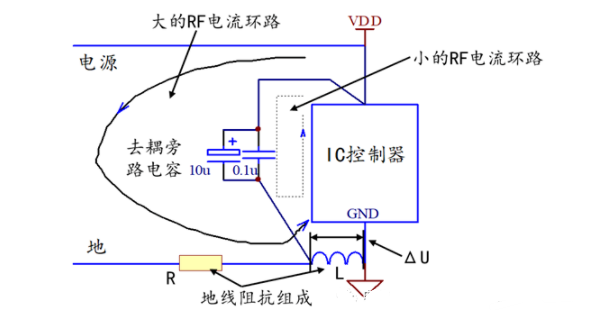

337 能量從高頻器件的電源端泄放到電源分配網絡。去耦電容也為器件和元件提供一個局部的直流源,這對減小電流在板上傳播浪涌尖峰很有作用。 在數字電路及IC控制器電路中,必須要進行電源去耦。當元件開關消耗直流能量時,沒有去

2021-01-07 14:30:28 2486

2486

電子發燒友網為你提供PCB布局指南:旁路電容,接地,焊盤資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:44:28 17

17 數字電路輸出高電平時從電源拉出的電流Ioh和低電平輸出時灌入的電流Iol的大小一般是不同的,即:Iol>Ioh。

2022-02-09 10:47:44 4

4 對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠,最外層放置容值最大的。但是,所有對該芯片去耦的電容都盡量

2022-02-10 12:05:02 19

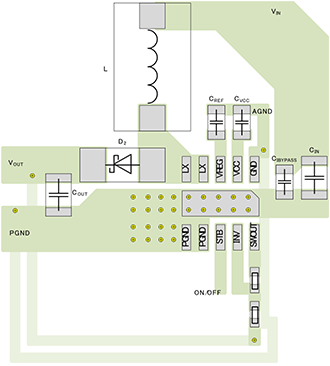

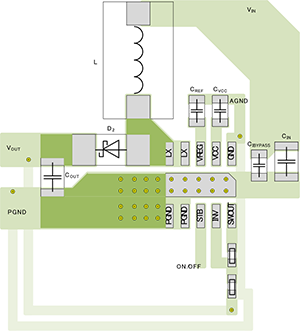

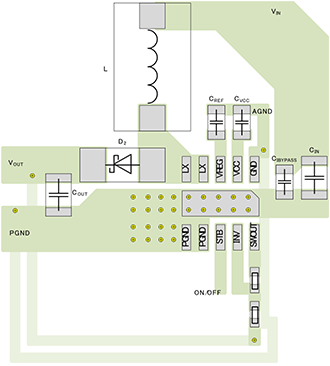

19 從本文開始,我們將對升壓型DC/DC轉換器的PCB板布局的各個元器件的配置及其要點進行說明。上一篇文章所述的升壓型DC/DC轉換器的PCB板布局的步驟是決定元器件配置的順序,如果升壓型DC/DC轉換器的PCB板布局基本可以按照這個順序進行設計,則可以提高設計效率。

2023-02-22 16:41:08 652

652

繼上一篇文章針對升壓型DC/DC轉換器的輸入電容器之后,接下來將對升壓型DC/DC轉換器的重要元器件--輸出電容器和續流二極管進行配置。

2023-02-22 16:41:09 832

832

在PCB的設計中,使用去偶電容能夠有效濾除電源中包含的噪聲,電容的擺放是根據容值大小確定,電容的去耦作用是有一定的距離要求,滿足去耦半徑問題

2023-03-08 15:15:00 1288

1288 自諧振頻率點是區分電容器是容性還是感性的分界點,低于諧振頻率時電容表現為電容特性,高于諧振頻率是電容表現為電感特性。

2023-03-09 12:23:56 440

440 前向串音作為PCB設計中的學習難點,一直以來會影響到電路的正常運行,經常被電子工程師來處理電子電路上的串音問題,這其中離不開前向串音的電容特性,所以今天來學習前向串音的電容特性。

2023-03-09 15:25:47 283

283 工作時產生的ΔI噪聲電流,保證工作電源電壓的穩定。它的大小為PCB上所有負載電容和的50~100倍。它應放置在緊靠PCB外接電源線和地線的地方,印制線密度很高的地方。這不僅不會減小低頻去耦,而且還會為PCB上布置關鍵性的印制線提供空間。

2023-06-15 18:04:01 1420

1420

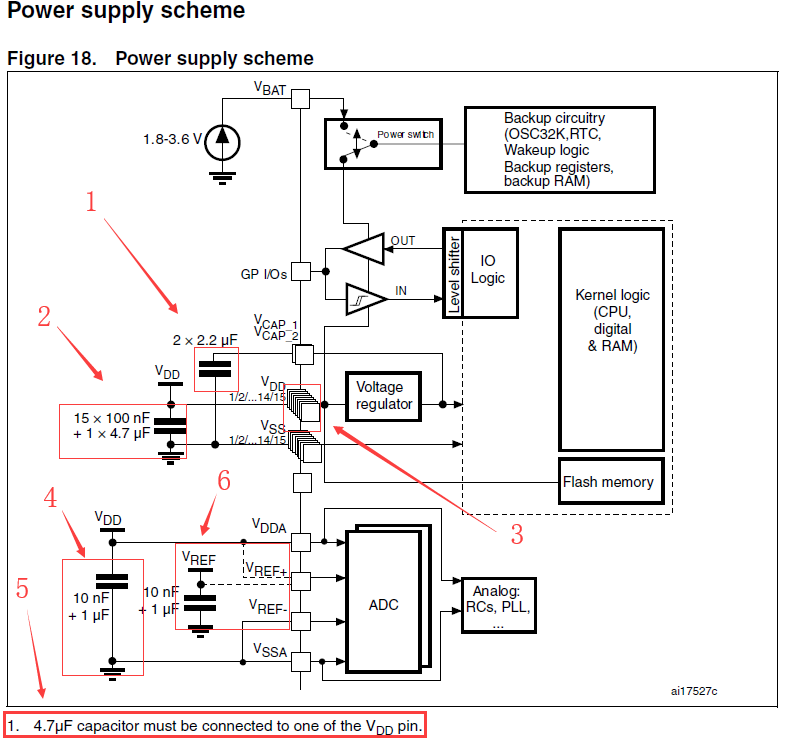

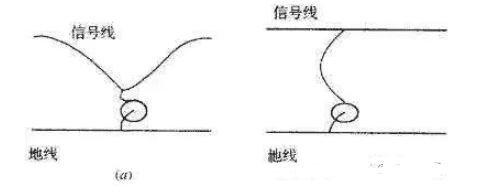

表示VDD1到VDD15接上VDD電源,再接電容,接地。Vss接地。PCB布局,盡量把電容離管腳近;

2023-07-11 15:15:12 854

854

PCB 結構中至關重要的兩個組件是電阻器和元件。他們的角色對于開發最優質的工業 PCB 來實現各方面安全、無縫的電子性能至關重要。如果我們依賴有故障的元件,包括電阻器和電容器,那么PCB完全故障的可能性就更大。

2023-07-31 12:08:11 964

964 數字電路輸出高電平時從電源拉出的電流Ioh和低電平輸出時灌入的電流Iol的大小一般是不同的,即:Iol>Ioh。以下圖的TTL與非門為例說明尖峰電流的形成:

2023-08-14 11:52:12 503

503

pcb連線寄生電容一般多少 隨著電子產品制造技術的成熟和發展,隨之而來的是布線技術的迅速發展。不同的 PCB 布線技術對于電路性能的影響不同,而其中最常見的問題之一就是 PCB 連線寄生電容。這種

2023-08-27 16:19:44 1606

1606 不同PCB封裝大小的電容體本身大小肯定是不同;那如果問你,PCB封裝相同的電容體就是一樣大的嗎?通俗說就是0402封裝的電容會比0201的大,如果都是0402封裝的電容之間來比呢?

2023-10-17 16:42:13 331

331

一站式PCBA智造廠家今天為大家講講PCB設計時電容如何擺放?PCB設計過程中電容作用及擺放位置。PCB設計為什么電容要就近擺放呢?因為它有有效半徑,放的遠了失效。電容去耦的一個重要問題是電容

2023-10-20 09:17:36 495

495 理解去耦半徑的辦法就是考察噪聲源和電容補償電流之間的相位關系。當芯片對電流的需求發生變化時,會在電源平面的一個很小的局部區域內產生電壓擾動,電容要補償這一電流(或電壓),就必須先感知到這個電壓擾動。信號在介質中傳播需要一定的時間,因此從發生局部電壓擾動到電容感知到這一擾動之間有一個時間延遲。

2023-11-22 15:39:23 105

105 波峰焊面,陰影效應區域為0.8mm(垂直于PCB傳送方向)和1.2mm(平行于PCB傳送方向),鉭電容在前為2.5mm,以焊盤間距判別。

2024-03-01 10:51:38 116

116

電子發燒友App

電子發燒友App

評論