1.1?PCB板上預劃分數(shù)字、模擬、DAA信號布線區(qū)域。?

1.2?數(shù)字、模擬元器件及相應走線盡量分開并放置於各自的布線區(qū)域內(nèi)。?

1.3?高速數(shù)字信號走線盡量短。?

1.4?敏感模擬信號走線盡量短。?

1.5?合理分配電源和地。?

1.6?DGND、AGND、實地分開。?

1.7?電源及臨界信號走線使用寬線。?

1.8?數(shù)字電路放置於并行總線/串行DTE接口附近,DAA電路放置於電話線接口附近。?

2.?元器件放置?

2.1?在系統(tǒng)電路原理圖中:?

a)?劃分數(shù)字、模擬、DAA電路及其相關(guān)電路;?

b)?在各個電路中劃分數(shù)字、模擬、混合數(shù)字/模擬元器件;?

c)?注意各IC芯片電源和信號引腳的定位。?

2.2?初步劃分數(shù)字、模擬、DAA電路在PCB板上的布線區(qū)域(一般比例2/1/1),數(shù)字、模擬元器件及其相應走線盡量遠離并限定在各自的布線區(qū)域內(nèi)。?

Note:當DAA電路占較大比重時,會有較多控制/狀態(tài)信號走線穿越其布線區(qū)域,可根據(jù)當?shù)匾?guī)則限定做調(diào)整,如元器件間距、高壓抑制、電流限制等。?

2.3?初步劃分完畢後,從Connector和Jack開始放置元器件:?

a)?Connector和Jack周圍留出插件的位置;?

b)?元器件周圍留出電源和地走線的空間;?

c)?Socket周圍留出相應插件的位置。?

2.4?首先放置混合型元器件(如Modem器件、A/D、D/A轉(zhuǎn)換芯片等):?

a)?確定元器件放置方向,盡量使數(shù)字信號及模擬信號引腳朝向各自布線區(qū)域;?

b)?將元器件放置在數(shù)字和模擬信號布線區(qū)域的交界處。?

2.5?放置所有的模擬器件:?

a)?放置模擬電路元器件,包括DAA電路;?

b)?模擬器件相互靠近且放置在PCB上包含TXA1、TXA2、RIN、VC、VREF信號走線的一面;?

c)?TXA1、TXA2、RIN、VC、VREF信號走線周圍避免放置高噪聲元器件;?

d)?對於串行DTE模塊,DTE?EIA/TIA-232-E?

系列接口信號的接收/驅(qū)動器盡量靠近Connector并遠離高頻時鐘信號走線,以減少/避免每條線上增加的噪聲抑制器件,如阻流圈和電容等。?

2.6?放置數(shù)字元器件及去耦電容:?

a)?數(shù)字元器件集中放置以減少走線長度;?

b)?在IC的電源/地間放置0.1uF的去耦電容,連接走線盡量短約跣?MI;?

c)?對并行總線模塊,元器件緊靠?

Connector邊緣放置,以符合應用總線接口標準,如ISA總線走線長度限定在2.5in;?

d)?對串行DTE模塊,接口電路靠近Connector;?

e)?晶振電路盡量靠近其驅(qū)動器件。?

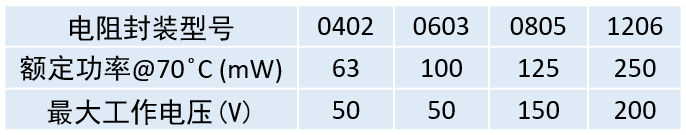

2.7?各區(qū)域的地線,通常用0?Ohm電阻或bead在一點或多點相連。?

3.?信號走線?

3.1?Modem信號走線中,易產(chǎn)生噪聲的信號線和易受干擾的信號線盡量遠離,如無法避免時要用中性信號線隔離。?

Modem易產(chǎn)生噪聲的信號引腳、中性信號引腳、易受干擾的信號引腳如下表所示:?

===============================================================?

|?Noise?Source?|?neutral?|?noise?

sensitive?

-----------+----------------+----------------+-----------------?

VDD,GND,?AGND?|?|?31,38,34,37?|?

-----------+----------------+----------------+-----------------?

Crystal?|?52,53?|?|?

-----------+----------------+----------------+-----------------?

Reset?|?|?35?|?

-----------+----------------+----------------+-----------------?

Memory?BUS|?1-6,9-10,12-13?|?|?

|?43-50,58-68?|?|?

-----------+----------------+----------------+-----------------?

NVRAM?|?|?39,42?|?

-----------+----------------+----------------+-----------------?

Telephone?|?|?7-8,36,51,54?|?24-25,30,32-33?

-----------+----------------+----------------+-----------------?

Audio?|?|?|?23,26-29?

-----------+----------------+----------------+-----------------?

串行DTE?|?40-41?|?11,14-22,55-57?|?

===============================================================?

===============================================================?

|?Noise?Source?|?neutral?|?noise?

sensitive?

-----------+----------------+----------------+-----------------?

VDD,GND,?AGND?|?|?31,38,34,37?|?

-----------+----------------+----------------+-----------------?

Crystal?|?52,53?|?|?

-----------+----------------+----------------+-----------------?

Reset?|?|?35?|?

-----------+----------------+----------------+-----------------?

Memory?BUS|?1-6,9-10,12-13?|?|?

|?43-50,58-68?|?|?

-----------+----------------+----------------+-----------------?

NVRAM?|?|?39,42?|?

-----------+----------------+----------------+-----------------?

Telephone?|?|?7-8,36,51,54?|?24-25,30,32-33?

-----------+----------------+----------------+-----------------?

Audio?|?|?|?23,26-29?

-----------+----------------+----------------+-----------------?

并行總線?|?11,14-22,40-41?|?|?

|?55-57?|?|?

===============================================================?

3.2?數(shù)字信號走線盡量放置在數(shù)字信號布線區(qū)域內(nèi);?

模擬信號走線盡量放置在模擬信號布線區(qū)域內(nèi);?

(可預先放置隔離走線加以限定,以防走線布出布線區(qū)域)?

數(shù)字信號走線和模擬信號走線垂直以減小交叉耦合。?

3.3?使用隔離走線(通常為地)將模擬信號走線限定在模擬信號布線區(qū)域。?

a)?模擬區(qū)隔離地走線環(huán)繞模擬信號布線區(qū)域布在PCB板兩面,線寬50-100mil;?

b)?數(shù)字區(qū)隔離地走線環(huán)繞數(shù)字信號布線區(qū)域布在PCB板兩面,線寬50-100mil,其中一面PCB板邊應布200mil寬度。?

3.4?并行總線接口信號走線線寬>10mil(一般為12-15mil),如/HCS、/HRD、/HWT、/RESET。?

3.5?模擬信號走線線寬>10mil(一般為12-15mil),如MICM、MICV、SPKV、VC、VREF、TXA1、TXA2、RXA、TELIN、TELOUT。?

3.6?所有其它信號走線盡量寬,線寬>5mil(一般為?10mil),元器件間走線盡量短(放置器件時應預先考慮)。?

3.7?旁路電容到相應IC的走線線寬>25mil,并盡量避免使用過孔。?

3.8?通過不同區(qū)域的信號線(如典型的低速控制/狀態(tài)信號)應在一點(首選)或兩點通過隔離地線。如果走線只位於一面,?隔離地線可走到PCB的另一面以跳過信號走線而保持連續(xù)。?

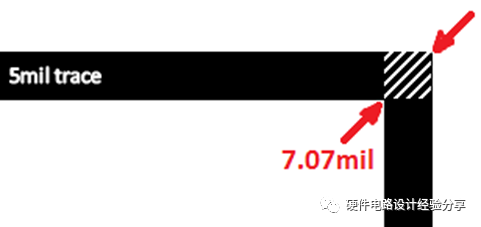

3.9?高頻信號走線避免使用90度角彎轉(zhuǎn),應使用平滑圓弧或45度角。?

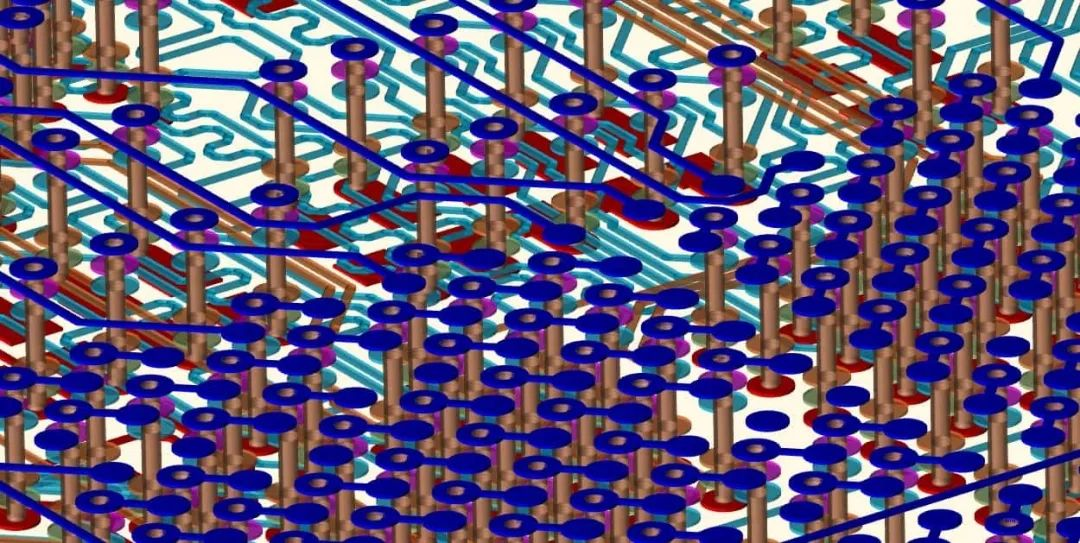

3.10?高頻信號走線應減少使用過孔連接。?

3.11?所有信號走線遠離晶振電路。?

3.12?對高頻信號走線應采用單一連續(xù)走線,避免出現(xiàn)從一點延伸出幾段走線的情況。?

3.13?DAA電路中,穿孔周圍(所有層面)留出至少60mil的空間。?

3.14?清除地線環(huán)路,以防意外電流回饋影響電源。

4.?電源?

4.1?確定電源連接關(guān)系。?

4.2?數(shù)字信號布線區(qū)域中,用10uF電解電容或鉭電容與0.1uF瓷片電容并聯(lián)後接在電源/地之間.在PCB板電源入口端和最遠端各放置一處,以防電源尖峰脈沖引發(fā)的噪聲干擾。?

4.3?對雙面板,在用電電路相同層面中,用兩邊線寬為?200mil的電源走線環(huán)繞該電路。(另一面須用數(shù)字地做相同處理)?

4.4?一般地,先布電源走線,再布信號走線。?

5.?地?

5.1雙面板中,數(shù)字和模擬元器件(除DAA)周圍及下方未使用之區(qū)域用數(shù)字地或模擬地區(qū)域填充,各層面同類地區(qū)域連接在一起,不同層面同類地區(qū)域通過多個過孔相連:Modem?DGND引腳接至數(shù)字地區(qū)域,AGND引腳接至模擬地區(qū)域;數(shù)字地區(qū)域和模擬地區(qū)域用一條直的空隙隔開。?

5.2?四層板中,使用數(shù)字和模擬地區(qū)域覆蓋數(shù)字和模擬元器件(除DAA);Modem?DGND引腳接至數(shù)字地區(qū)域,AGND引腳接至模擬地區(qū)域;數(shù)字地區(qū)域和模擬地區(qū)域用一條直的空隙隔開。?

5.3?如設(shè)計中須EMI過濾器,應在接口插座端預留一定空間,絕大多數(shù)EMI器件(Bead/電容)均可放置在該區(qū)域;未使用之區(qū)域用地區(qū)域填充,如有屏蔽外殼也須與之相連。?

5.4?每個功能模塊電源應分開。功能模塊可分為:并行總線接口、顯示、數(shù)字電路(SRAM、EPROM、Modem)和DAA等,每個功能模塊的電源/地只能在電源/地的源點相連。?

5.5?對串行DTE模塊,使用去耦電容減少電源耦合,對電話線也可做相同處理。?

5.6?地線通過一點相連,如可能,使用Bead;如抑制EMI需要,允許地線在其它地方相連。?

5.7?所有地線走線盡量寬,25-50mil。?

5.8?所有IC電源/地間的電容走線盡量短,并不要使用過孔。?

6.?晶振電路?

6.1?所有連到晶振輸入/輸出端(如XTLI、XTLO)的走線盡量短,以減少噪聲干擾及分布電容對Crystal的影響。XTLO走線盡量短,且彎轉(zhuǎn)角度不小於45度。(因XTLO連接至上升時間快,大電流之驅(qū)動器)?

6.2?雙面板中沒有地線層,晶振電容地線應使用盡量寬的短線連接至器件上離晶振最近的DGND引腳,且盡量減少過孔。?

6.3?如可能,晶振外殼接地。?

6.4?在XTLO引腳與晶振/電容節(jié)點處接一個100?Ohm電阻。?

6.5?晶振電容的地直接連接至?Modem的GND引腳,不要使用地線區(qū)域或地線走線來連接電容和Modem的GND引腳。

?

7.?使用EIA/TIA-232接口的獨立Modem設(shè)計?

7.1?使用金屬外殼。?如果須用塑料外殼,應在內(nèi)部貼金屬箔片或噴導電物質(zhì)以減小EMI。?

7.2?各電源線上放置相同模式的Choke。?

7.3?元器件放置在一起并緊靠EIA/TIA-232接口的Connector。?

7.4?所有EIA/TIA-232器件從電源源點單獨連接電源/地。電源/地的源點應為板上電源輸入端或調(diào)壓芯片的輸出端。?

7.5?EIA/TIA-232電纜信號地接至數(shù)字地。?

7.6?以下情況EIA/TIA-232電纜屏蔽不用接至Modem外殼;空接;通過Bead接到數(shù)字地;EIA/TIA-232電纜靠近Modem外殼處放置一磁環(huán)時直接連到數(shù)字地。?

8.?VC及VREF電路電容走線盡量短,且位於中性區(qū)域。?

8.1?10uF?VC電解電容正極與0.1uF?VC電容的連接端通過獨立走線連至Modem的VC引腳(PIN24)。?

8.2?10uF?VC電解電容負極與0.1uF?VC電容的連接端通過Bead後用獨立走線連至Modem的AGND引腳(PIN34)。?

8.3?10uF?VREF電解電容正極與0.1uF?VC電容的連接端通過獨立走線連至Modem的VREF引腳(PIN25)。?

8.4?10uF?VREF電解電容負極與0.1uF?VC電容的連接端通過獨立走線連至Modem的VC引腳(PIN24);注意與8.1走線相獨立。?

VREF?------+--------+?

┿?10u?┿?0.1u?

VC?------+--------+?

┿?10u?┿?0.1u?

+--------+-----~~~~~---+?AGND?

使用之Bead應滿足:?

100MHz時,阻抗=70W;;?

額定電流=200mA;;?

最大電阻=0.5W。?

9.?電話和Handset接口?

9.1?Tip和Ring線接口處放置Choke。?

9.2?電話線的去耦方法與電源去耦類似,使用增加電感組合體、Choke、電容等方法。但電話線的去耦比電源去耦更困難也更值得注意,?一般做法是預留這些器件的位置,以便性能/EMI測試認證時調(diào)整。?

9.3?Tip和Ring線到數(shù)字地間放置耐壓高的濾波電容(0.001uF/1KV)。

- pcb(383717)

- ut指南(5317)

相關(guān)推薦

PCB Layout的第一次經(jīng)歷分享

PCB Layout的第一次經(jīng)歷分享

試著layout一回,使用的軟件是PADS layout 2005 sp1。據(jù)同事說這個軟件不算穩(wěn)定,用時心里也有點虛,不過上手的時候用的就是這個版本,就沒

2010-01-16 16:59:57 2485

2485

2485

2485PCB layout中的走線設(shè)計

PCB layout需要豐富的經(jīng)驗和扎實的理論基礎(chǔ)支持,還要多踩幾個坑,多做幾個仿真加深對走線的理解,才能形成閉環(huán)的走線設(shè)計。

2022-07-19 15:10:41 3170

3170

3170

3170PCB Layout的設(shè)計要點

在集成電路應用設(shè)計中,項目原理圖設(shè)計完成之后,就需要進行PCB布板的設(shè)計。 PCB設(shè)計是一個至關(guān)重要的環(huán)節(jié)。 設(shè)計結(jié)果的優(yōu)劣直接影響整個設(shè)計功能。 因此,合理高效的PCB Layout是芯片電路設(shè)計調(diào)試成功中至關(guān)重要的一步。 本次我們就來簡單講一講PCB Layout的設(shè)計要點。

2023-05-22 10:59:17 734

734

734

734

PCB Layout設(shè)計要點與技巧

在集成電路應用設(shè)計中,項目原理圖設(shè)計完成之后,就需要進行PCB布板的設(shè)計。PCB設(shè)計是一個至關(guān)重要的環(huán)節(jié)。設(shè)計結(jié)果的優(yōu)劣直接影響整個設(shè)計功能。因此,合理高效的PCB Layout是芯片電路設(shè)計調(diào)試成功中至關(guān)重要的一步。本次我們就來簡單講一講PCB Layout的設(shè)計要點。

2023-05-31 10:52:56 936

936

936

936

pcb layout中IC常用封裝介紹

本內(nèi)容介紹了pcb layout中IC常用封裝,了解這些常識對PCB LAYOUT是有幫助的。下面還將介紹幾種IC封裝。

2011-11-09 15:52:07 8229

8229

8229

8229PCB layout軟件該如何學習和PCB設(shè)計需要注意的問題

的常見布線規(guī)則、注意事項掌握PCB的常見布線規(guī)則、注意事項。10常用快捷鍵介紹Pads原理圖、Layout常用快捷鍵熟練掌握Pads原理圖、Layout常用快捷鍵的使用11高級Layout指南介紹較復雜

2014-09-16 19:35:45

PCB layout 服務(wù)

本人從事PCB layout工作已多年,熟悉1-20層板的設(shè)計,應用PADS9.3,allegro16.3軟件設(shè)計PCB板,能夠?qū)敫鞣N軟件的原理圖,做過GPS,雷達模擬器等產(chǎn)品,有FPGA

2012-10-02 00:06:44

PCB及PCB LAYOUT設(shè)計

PCB及PCB LAYOUT設(shè)計工程師歡迎下載分享本人主要做LED驅(qū)動IC 產(chǎn)品QQ2892715427望認識各位工程師朋友互相學習技術(shù)探討方案資料太大還沒有分享完有需要的工程朋友 可以回帖[hide][/hide]

2015-11-19 15:24:21

layout與PCB有何關(guān)系

精辟!一文看懂layout與PCB的關(guān)系由于開關(guān)電源的開關(guān)特性, 容易使得開關(guān)電源產(chǎn)生極大的電磁兼容方面的干擾,作為一個電源工程師、電磁兼容工程師,或則一個 PCB layout 工程師必須了解

2021-08-06 08:46:28

BK3432Q/BK3432 開發(fā)應用指南& PCB LAYOUT指南,專業(yè)技術(shù)支持

我司是上海博通BK芯片一級代理,主要產(chǎn)品有藍牙、2.4G芯片和藍牙模組公司有強大的研發(fā)團隊不僅可以為您提供最好的技術(shù)支持,還可以為您提供一站式物聯(lián)網(wǎng)解決方案。詳詢:劉 ***qq506710311二.藍牙模塊1. BLE藍牙芯片系列:BK3431Q:低功耗藍牙4.2BLE,SOC芯片,Flash版本,ARM9內(nèi)核,QFN48和QFN32封裝,64KRAM, 500K Flash,RX5.2mA,TX5.0mA,休眠2uA適用于藍牙電子秤、藍牙防丟、藍牙手環(huán)、智能穿戴設(shè)備、藍牙智能家居APP控制等低功耗藍牙產(chǎn)品BK3432:低功耗藍牙4.2BLE+3.0雙模,SOC芯片,Flash版本,ARM9內(nèi)核,QFN32封裝,20K RAM, 160K Flash,RX5.1mA,TX4.8mA,休眠1.8uA,資源相對BK3431Q做了精簡,兼容性更好,性價比更好,適用于做標準透傳類等簡單的應用開發(fā)。BK3266: 低功耗藍牙音頻雙模芯片耳機3266, qfn32 4*4 (主推)4Mflash (傳統(tǒng)藍牙BL、 tws/AI)、 8Mflash(數(shù)據(jù)大,多國語言,OTA,來電報號)AI耳機 :開放數(shù)據(jù)接口,對接云,(小米,百度,阿里(主要),亞馬遜(下半年))40pin5*5:8M和16M16GPIO產(chǎn)品:入耳,單邊,頭戴,tws,線控,提供:參考設(shè)計,Tws,,彈窗、自動開機,雙邊通話,敲擊喚醒UA287Q標準透傳模塊?功耗極低,休眠電流在2微安,TX發(fā)射電流為5mA,RX接受電流為5.2mA。?性價比高?資源豐富,內(nèi)置500K Flash,有64kRAM可供客戶二次開發(fā)?支持藍牙4.2,可做主機模式或從機模式?支持微信AirSync廣泛應于電子稱、手環(huán),鍵鼠,血壓計,血糖儀、pos機等低功耗產(chǎn)品支持二次開發(fā),滿足客戶訂制化應用。三.BK上海博通2.4G芯片1. 2.4G無線射頻系列:1)BK2425:單RF,有裸片和QFN20兩種封裝,適用于遙控器、無線鍵鼠、手柄、玩具和無線周邊設(shè)備。2)BK2535:SOC芯片,F(xiàn)lash版本,51核+RF2.4G,有QFN32和QFN56兩種封裝,IO口多,功耗最低,可用于無線鍵鼠,鼠標,智能遙控器,無線數(shù)據(jù)傳輸,安防產(chǎn)品,數(shù)據(jù)采集系統(tǒng)等3)BK2451:SOC芯片,OTP版本,51核+RF2.4G,SOP20和QFN20封裝,支持USB2.0,常用于USB接收端4)BK2461:SOC芯片,OTP版本,ARM9+RF2.4G,內(nèi)置PA,最大可輸出功率12dBm,5PWM,有SOP16、SOP20和QFN24三種封裝,適用于遠距離控制產(chǎn)品,如飛控,燈控,各類遙控器、空鼠和玩具等5)BK2452:SOC芯片,OTP版本,51核+RF2.4G,SOP16和QFN32封裝6)BK2471:SOC芯片,F(xiàn)lash版本,ARM9+RF2.4G,有QFN32和QFN56封裝,常用于無人機等飛控產(chǎn)品作為接收端四、wifi芯片系列(藍牙+wifi二合一芯片)7)BK7231S 數(shù)傳wifi芯片8)BK7231U 藍牙+wifi雙模,支持圖傳,無人機應用9)BK7251藍牙+wifi音頻 支持音頻解碼,可用于故事機,播報機等●其中以上多款芯片可以根據(jù)不同的產(chǎn)品進行搭配,實現(xiàn)利益最大化。

2019-05-13 09:59:54

PADS 高速PCB layout設(shè)計手機layout視頻教程下載地址

PADS 高速PCB layout設(shè)計手機layout視頻教程下載地址Cadence DDR3 PCBlayout視頻教程:

2015-04-05 22:13:08

UltraScale架構(gòu)用于閃存的PCB布局指南是什么

什么是閃存的布局指南,如長度要求?我在文檔中看不到任何信息:UG583-UltraScale架構(gòu)PCB設(shè)計和引腳規(guī)劃用戶指南_ 1.1謝謝以上來自于谷歌翻譯以下為原文What's

2019-04-16 06:06:39

[分享]PCB Layout指南(上)

本帖最后由 eehome 于 2013-1-5 10:03 編輯

<p>PCB Layout指南(上)&nbsp;&nbsp

2009-05-31 11:03:19

[分享]PCB Layout指南(下)

本帖最后由 eehome 于 2013-1-5 09:53 編輯

<p>PCB Layout指南(下)&nbsp;&nbsp

2009-05-31 11:04:10

專業(yè)承接PCB Layout設(shè)計~

本人有6年PCB layout設(shè)計經(jīng)驗,長期從事數(shù)碼產(chǎn)品的PCB layout及EMC設(shè)計整改工作!熟悉ORCAD和PADS設(shè)計軟體精通PCB布局走線設(shè)計及設(shè)計過程的EMC考量!現(xiàn)愿承接PCB

2014-02-23 15:59:44

專業(yè)承接PCB layout設(shè)計~

本人有6年PCB layout設(shè)計經(jīng)驗,長期從事數(shù)碼產(chǎn)品的PCB layout及EMC設(shè)計整改工作!熟悉ORCAD和PADS設(shè)計軟體精通PCB布局走線設(shè)計及設(shè)計過程的EMC考量!現(xiàn)愿承接PCB

2014-02-23 16:02:10

關(guān)于PCB LAYOUT

我在學PCB LAYOUT ,可是關(guān)于別人作品中畫的很好的大塊銅皮是怎么畫的(不是全局敷銅那種),希望能得到詳細點的說明和指導

2017-02-04 09:17:45

承接pcb layout 兼職

本帖最后由 pcb兼職 于 2017-3-9 20:30 編輯

本人從事PCB Layout設(shè)計有5年的工作經(jīng)驗,能獨立處理工作。期間Layout做過電腦主板,工控主板,醫(yī)療儀器。曾在

2017-03-04 21:25:12

承接pcb layout 兼職

`本人從事PCB Layout設(shè)計有5年的工作經(jīng)驗,能獨立處理工作。期間Layout做過電腦主板,工控主板,醫(yī)療儀器。曾在外包公司派到華為現(xiàn)場辦公,做過的產(chǎn)品有電源板,數(shù)模混合,路由器,融合網(wǎng)關(guān)

2017-06-13 22:39:40

承接電路、PCB設(shè)計,PCB Layout !

本人有多年的硬件及PCB layout設(shè)計經(jīng)驗,深厚的電子專業(yè)水平和硬件設(shè)計能力,熟悉產(chǎn)品開發(fā)流程,現(xiàn)想利用業(yè)余時間承接電路設(shè)計,PCB 設(shè)計,PCB layout。設(shè)計軟件有pads

2015-05-16 19:16:35

接電路設(shè)計,PCB設(shè)計,PCB Layout

本人有多年的硬件及PCB layout設(shè)計經(jīng)驗,深厚的電子專業(yè)水平和硬件設(shè)計能力,熟悉產(chǎn)品開發(fā)流程,現(xiàn)想利用業(yè)余時間承接電路設(shè)計,PCB 設(shè)計,PCB layout。設(shè)計軟件有pads

2015-05-16 19:18:22

pcb設(shè)計教程 (收藏多年的經(jīng)典知識)

pcb設(shè)計教程內(nèi)容有:高速PCB設(shè)計指南之一 高速PCB設(shè)計指南之二 PCB Layout指南(上) PCB Layout指南(下) PCB設(shè)計的一般原則 PCB設(shè)計基礎(chǔ)知識 PCB設(shè)計基本概念 pcb設(shè)計注意

2009-01-18 13:08:07 0

0

0

0(四)通過優(yōu)化PCB layout 有效降低EMI

PCB設(shè)計LayoutPcb layout行業(yè)芯事經(jīng)驗分享

硬件小哥哥發(fā)布于 2022-06-28 14:53:04

PCB LAYOUT基本規(guī)范

為確保產(chǎn)品之製造性, R&D在設(shè)計階段必須遵循Layout相關(guān)規(guī)範, 以利製造單位能順利生產(chǎn), 確保產(chǎn)品良率, 降低因設(shè)計而重工之浪費. “PCB Layout Rule” Rev1.60 (發(fā)文字號: MT-8-2-0029)發(fā)

2009-10-17 10:59:02 235

235

235

235PCB設(shè)計基礎(chǔ)教程手冊

PCB設(shè)計基礎(chǔ)教程

此教程包括:

高速PCB設(shè)計指南之一 高速PCB設(shè)計指南之二 PCB Layout指南(上) PCB Layout指南(下) PCB設(shè)計的一般原則 PCB設(shè)計基礎(chǔ)知識 PCB設(shè)計

2010-03-15 14:22:26 0

0

0

0PCB Layout中的走線策略

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速PC

2010-06-11 15:41:21 0

0

0

0XL-BST PCB LAYOUT智能工具

XL-BST PCB LAYOUT智能工具是一款架構(gòu)于Xpedition,結(jié)合設(shè)計師實際應用場景,由解決多項實際應用操作組成的智能工具。通過XL-BST,在設(shè)計操作層面,設(shè)計師能快速

2024-03-18 17:55:31

PCB LAYOUT設(shè)計規(guī)范手冊

PCB Layout Rule Rev1.70, 規(guī)範內(nèi)容如附件所示, 其中分為:

(1) ”PCB LAYOUT 基本規(guī)範”:為R&D Layout時必須遵守的事項, 否則SMT,DIP,裁板時無法生產(chǎn).

(2) “錫偷LAYOUT

2010-11-01 16:59:45 0

0

0

0PCB LAYOUT術(shù)語解釋

PCB LAYOUT術(shù)語解釋

PCB LAYOUT 術(shù)語解釋(TERMS)1. COMPONENT SIDE(零件面、正面)︰大多數(shù)零件放置之面。2. SOLDER SIDE(焊錫面、反面)。3. SOLDER M

2008-07-18 12:31:05 2320

2320

2320

2320pcb layout是什么

pcb layout是什么

PCB是印刷電路板(即Printed Circuit Board)的簡稱。印刷電路板是組裝電子零件用的基板,是在通用基材上按預定設(shè)計形成點

2009-09-30 08:52:24 15959

15959

15959

15959PCB Layout經(jīng)驗分享

PCB Layout經(jīng)驗分享

試著layout一回,使用的軟件是PADS layout 2005 sp1。據(jù)同事說這個軟

2010-03-21 18:06:30 5552

5552

5552

5552PCB和PCB LAYOUT相關(guān)詞匯全解

本內(nèi)容詳細解釋了PCB和PCB LAYOUT的相關(guān)術(shù)語,為PCB LAYOUT設(shè)計人員提供了方便

2011-11-09 16:01:29 3185

3185

3185

3185pcb layout基礎(chǔ)學習

本專題詳細講解了什么是pcb layout,pcb layout基礎(chǔ)知識的學習及pcb layout工程師需要注意的事項,還有pcb layout設(shè)計的一些經(jīng)驗分享。

2011-11-21 14:04:34

PCB Layout指南

2012-03-08 03:20:38 0

0

0

0PCB layout電路設(shè)計七大法寶!

PCB Layout設(shè)計規(guī)則檢查 能夠應用和生產(chǎn),繼而成為一個正式的有效的產(chǎn)品才是PCB layout最終目的,layout的工作才算告一個段落。那么在layout的時候,應該注意哪些常規(guī)的要點

2018-03-23 14:56:00 2652

2652

2652

2652常用pcb layout軟件有哪些

本文開始借介紹了pcb layout的概念和特性,其次介紹了pcb layout設(shè)計流程,最后介紹了幾款pcb layout的常用軟件與發(fā)展趨勢。

2018-04-09 15:40:43 17025

17025

17025

17025

PCB layout工程師的7個好習慣

作為一名優(yōu)秀的PCB layout工程師,好的工作習慣會使你的設(shè)計更合理,性能更好,生產(chǎn)更容易。本文羅列了PCB layout工程師的7個好習慣,來看看你都占了幾個吧!

2022-02-16 15:46:31 2616

2616

2616

2616PCB LAYOUT的直角走線、差分走線、蛇形線資料下載

電子發(fā)燒友網(wǎng)為你提供PCB LAYOUT的直角走線、差分走線、蛇形線資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:41:16 17

17

17

17layout與PCB的29個基本關(guān)系資料下載

電子發(fā)燒友網(wǎng)為你提供layout與PCB的29個基本關(guān)系資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:44:58 7

7

7

7PCB 指南:快速理解高速layout設(shè)計資料下載

電子發(fā)燒友網(wǎng)為你提供PCB 指南:快速理解高速layout設(shè)計資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:49:21 25

25

25

25PCB Layout pcb布局的基本原則

PCB Layout即PCB布局,要使電子電路獲得最佳性能,電子元器件的布局及導線的布線是非常關(guān)鍵的環(huán)節(jié)。要使PCB質(zhì)量好,造價低,性能高,應將設(shè)計重點放在布局環(huán)節(jié)。以下是PCB布局的原則:

2021-07-21 16:44:24 14234

14234

14234

14234干貨分享:PCB Layout的設(shè)計要點

在集成電路應用設(shè)計中,項目原理圖設(shè)計完成之后,就需要進行PCB布板的設(shè)計。PCB設(shè)計是一個至關(guān)重要的環(huán)節(jié)。設(shè)計結(jié)果的優(yōu)劣直接影響整個設(shè)計功能。因此,合理高效的PCB Layout是芯片電路...

2021-12-16 16:54:04 15

15

15

15干貨分享:PCB Layout 的設(shè)計要點

在集成電路應用設(shè)計中,項目原理圖設(shè)計完成之后,就需要進行PCB布板的設(shè)計。PCB設(shè)計是一個至關(guān)重要的環(huán)節(jié)。設(shè)計結(jié)果的優(yōu)劣直接影響整個設(shè)計功能。因此,合理高效的PCB Layout是芯片電路...

2021-12-29 18:52:46 22

22

22

22PCB Layout中的走線策略

布線(Layout)是PCB設(shè)計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統(tǒng)的性能,大多數(shù)高速的設(shè)計理論也要最終經(jīng)過Layout得以實現(xiàn)并驗證,由此可見,布線在高速PCB設(shè)計中是至關(guān)重要的。

2022-08-12 14:38:39 1322

1322

1322

1322BK3432典型應用電路硬件參考設(shè)計PCB Layout指南

本章節(jié)描述了用 BK3432 如何簡單快速地設(shè)計原理圖及 PCB layout.

2022-10-27 09:28:13 4221

4221

4221

4221PCB Layout的設(shè)計要點及技巧

在集成電路應用設(shè)計中,項目原理圖設(shè)計完成之后,就需要進行PCB布板的設(shè)計。PCB設(shè)計是一個至關(guān)重要的環(huán)節(jié)。設(shè)計結(jié)果的優(yōu)劣直接影響整個設(shè)計功能。因此,合理高效的PCB Layout是芯片電路設(shè)計調(diào)試成功中至關(guān)重要的一步。本次我們就來簡單講一講PCB Layout的設(shè)計要點

2023-04-27 15:16:40 910

910

910

910

PCB layout在布線上的設(shè)計規(guī)范有哪些?

一站式PCBA智造廠家今天為大家講講pcb layout設(shè)計需要注意哪些細節(jié)?pcb layout設(shè)計規(guī)范。Printed Circuit Board (PCB)是一種電子零件,它是連接

2024-02-23 09:19:41 142

142

142

142 電子發(fā)燒友App

電子發(fā)燒友App

評論