本文將討論影響SNR損失(由信號縮放引入)的主要因素,如何對其進(jìn)行定量分析,以及更重要的是:如何把這種影響降至最低。

2012-05-02 09:25:22 1022

1022

要找到能和模擬輸入范圍一致,同時具有適量輸入、大小符合所需和正確采樣速度的模擬數(shù)字轉(zhuǎn)換器(ADC)往往相當(dāng)困難

2013-06-15 15:26:07 1165

1165

模/數(shù)轉(zhuǎn)換器(ADC)電路設(shè)計中,特別是當(dāng)系統(tǒng)設(shè)計人員需要處理各種擺幅的電壓信號時,很容易產(chǎn)生的一個誤區(qū)是縮小輸入信號范圍,以適應(yīng)ADC的滿量程范圍,這將大大降低信噪比(SNR)。綜合來看,低壓

2013-09-22 12:12:56 3874

3874

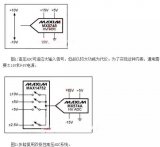

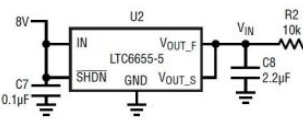

要獲得 ADC 的最佳 SNR 性能并不僅僅是給 ADC 輸入提供低噪聲信號,提供一個低噪聲基準(zhǔn)電壓是同等重要。

2017-10-19 13:51:25 11076

11076

獲得ADC的最佳SNR性能并不僅僅是給ADC輸入提供低噪聲信號的問題,提供一個低噪聲基準(zhǔn)電壓是同等重要。雖然基準(zhǔn)噪聲在零標(biāo)度沒有影響,但是在全標(biāo)度,基準(zhǔn)上的任何噪聲在輸出代碼中都將是可見的。對于某個

2022-07-13 09:17:27 1039

1039 昨天有小伙伴在課程群里問關(guān)于ADC的最小輸入電平怎么算,唉,又激起了我的痛點(diǎn)。

2024-01-05 18:18:46 813

813

大家好,我正在嘗試使用33210A信號發(fā)生器來確定PCB布局不佳的ADC的SNR損耗。來自數(shù)據(jù)表的ADC的SNR為85dB,我的測量結(jié)果為70dB。我需要確定ADC側(cè)的15dB差異以及mych如何來

2019-05-29 12:29:57

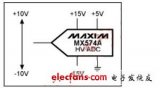

深入分析吧!ADC 輸入的過驅(qū)一般發(fā)生于驅(qū)動放大器電軌遠(yuǎn)遠(yuǎn)大于 ADC 最大輸入范圍時,例如,放大器采用±15 V 供電,而 ADC 輸入為 0 至 5V。高壓電軌用于接受±10 V 輸入,同時給

2021-02-22 09:29:39

架構(gòu)的類型,ADC供應(yīng)商會在數(shù)據(jù)手冊或產(chǎn)品頁面上提供這一數(shù)據(jù)。電壓駐波比(VWSR)與輸入阻抗密切相關(guān),衡量目標(biāo)帶寬內(nèi)反射到負(fù)載中的功率量。該參數(shù)設(shè)置實(shí)現(xiàn)ADC滿量程輸入所需的輸入驅(qū)動電平,因此很重

2023-12-18 06:13:51

(),因此噪聲將始終折疊在帶寬的頻帶中。然后我們可以使用公式3計算噪聲密度:其中F S是ADC時鐘舉個例子,讓我們從一個理想的ADC開始,噪聲僅僅是由量化引起的。SNR可以表示為等式4。其中n是位數(shù)

2018-07-24 17:25:11

1.電壓越大,其功率越大。所以高壓伺服的功率可以做到很大,可以達(dá)到幾千幾萬瓦。2.電流越大,電機(jī)的繞組線徑越大,所以在相同功率下,高壓伺服的繞組可以用較小的線徑,定子銅損也會比低壓電機(jī)小;對于較大

2021-06-28 07:33:07

高壓伺服電機(jī)有哪些優(yōu)點(diǎn)及缺點(diǎn)?低壓伺服電機(jī)和高壓伺服電機(jī)有哪些不同之處?

2021-09-30 07:10:06

本帖最后由 liuyongwangzi 于 2018-6-21 09:44 編輯

ADC采樣模擬信號提供表示輸入信號的量化數(shù)字碼。數(shù)字輸出代碼得到后處理,并且結(jié)果可以報告給使用該信息做出決定

2018-06-21 09:42:04

性能要求最終的DAQ/ADC DR規(guī)格通過將輸入范圍的DR貢獻(xiàn)添加至精度DR進(jìn)行確定。總諧波失真(THD)的影響求平均值計算假定AD7779的噪聲隨機(jī)且在頻譜中均勻分布。但是,系統(tǒng)中實(shí)際上還會存在一定

2018-10-17 10:37:13

早些年沒有大電流的電源設(shè)計嗎?答案當(dāng)然是否定的!那么這些年電源設(shè)計的大電流和之前有什么區(qū)別呢?我的總結(jié)是:一個是高壓大電流,一個是低壓大電流。高壓大電流電源的設(shè)計難點(diǎn)時間退回十年或者二十年之前,那個

2017-01-20 17:03:52

1000V、直流1500V為界,可劃分為高壓控制電器和低壓控制電器兩大類。總的來說,低壓電器可以分為配電電器和控制電器兩大類,是成套電氣設(shè)備的基本組成元件。在工業(yè)、農(nóng)業(yè)、交通、國防以及人們用電過程中

2016-07-12 09:45:01

老的設(shè)備在改造中已經(jīng)逐漸被高壓變頻替換掉。高低高型變頻器變頻器為低壓變頻器,采用輸入降壓變壓器和輸出升壓變壓器實(shí)現(xiàn)與高壓電網(wǎng)和電機(jī)的接口,這是當(dāng)時高壓變頻技術(shù)未成熟時的一種過渡技術(shù)。由于低壓變頻器電壓

2018-10-26 11:27:47

哪位大神知道高壓轉(zhuǎn)低壓的元器件大概24轉(zhuǎn)3V,最好是3V以下的?

2017-09-01 17:54:47

AD9226 輸入端電平轉(zhuǎn)換用DAC 實(shí)現(xiàn)是不是可以改善ADC的DNL同時提高SNR

2023-12-15 07:54:49

電路設(shè)計時,將AD9266的VCM端與變壓器的中心抽頭相連了,但是誤把變壓器輸出的信號又進(jìn)行了隔直處理,即模擬輸入的共模電平為0V,輸入峰峰值可到1V左右,即VIN-最低可到-0.5V,請問是否會對

2023-12-21 06:53:34

電路設(shè)計時,將AD9266的VCM端與變壓器的中心抽頭相連了,但是誤把變壓器輸出的信號又進(jìn)行了隔直處理,即模擬輸入的共模電平為0V,輸入峰峰值可到1V左右,即VIN-最低可到-0.5V,請問是否會對

2018-10-30 09:47:09

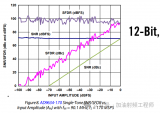

,這些系統(tǒng)在不同的應(yīng)用中各有不同。硅片處理技術(shù)的發(fā)展(65 nm CMOS、28 nm CMOS等)使高速 ADC 得以跨越 GSPS(每秒千兆采樣)門檻,同時提供12位或14位性能。對于系統(tǒng)設(shè)計人

2018-07-27 08:11:10

優(yōu)化信號調(diào)節(jié)時需要考慮的相關(guān)問題。但是,很多人不會預(yù)先考慮的一件事是 SAR ADC 的實(shí)際輸入類型。在本博客中,我將重點(diǎn)介紹三種 SAR 輸入(單端、偽差分與差分輸入)以及如何將其使用在應(yīng)用中。在以后

2022-11-21 06:38:28

輸入范圍”。SNR影響ADC的SNR將信號功率分量與采樣頻率一半以下的噪聲功率進(jìn)行比較,其中不包括諧波和DC。我使用以下等式來計算SNR影響:ADC輸入上的總系統(tǒng)噪聲由兩個分量組成:耦合自信號源以及輸入

2018-09-12 11:25:57

的輸出連接到APX525的輸入上,進(jìn)行頻譜分析,發(fā)現(xiàn)APX525的頻譜圖在靠近100khz的時候確實(shí)是噪底很高!

所以小弟在這里想請教眾大神一個問題,我們在測量某款ADC的SNR的時候,輸入的波形

2023-11-30 08:00:20

正如前面所討論的,在回歸中定義了損失函數(shù)或目標(biāo)函數(shù),其目的是找到使損失最小化的系數(shù)。本節(jié)將介紹如何在 TensorFlow 中定義損失函數(shù),并根據(jù)問題選擇合適的損失函數(shù)。聲明一個損失函數(shù)需要將系數(shù)

2020-07-28 14:38:42

本帖最后由 gk320830 于 2015-3-4 16:57 編輯

如圖做了一個TTL信號控制220v交流電的仿真,可以實(shí)現(xiàn),但是把電路焊出來以后,將負(fù)載Rl換成燈泡,輸入沒有用,一直是亮

2014-11-06 21:35:07

和更為精確地再現(xiàn)輸入信號,對于傳統(tǒng)ADC來講,必須增加位數(shù)。將采樣頻率提高一個過采樣系數(shù)k,即采樣頻率為Kfs,則由 FFT分析顯示噪聲基線降低,SNR值未變,但噪聲能量分散到一個更寬的頻率范圍

2016-08-03 09:02:37

頻譜密度(NSD)及其在目標(biāo)頻段內(nèi)的分布,能夠讓其在數(shù)據(jù)轉(zhuǎn)換過程中更好的被濾除 .。比較在不同速度下工作的系統(tǒng),或者查看軟件定義系統(tǒng)如何處理不同帶寬的信號時,噪聲頻譜密度(NSD)可以說比信噪比(SNR

2020-12-31 09:08:39

所有模數(shù)轉(zhuǎn)換器(ADC)都有一定量的“折合到輸入端噪聲”,可以將其模擬為與無噪聲ADC 輸入串聯(lián)的噪聲源。折合到輸入端噪聲與量化噪聲不同,后者僅在ADC處理交流信號時出 現(xiàn)。多數(shù)情況下,輸入噪聲越低

2023-12-18 08:21:20

嗨,我需要評估從ADC輸出的2V5 180MHz數(shù)字信號是否可以饋入Spartan-3A的LVTTL輸入引腳而不會失去完整性。實(shí)際上我已經(jīng)下載并打開了帶有管理程序的Spartan-3A IBIS

2020-06-12 14:57:56

情況會因設(shè)備和環(huán)境條件(如溫度和濕度)而導(dǎo)致。2. 檢查GPIO輸入的電平 大部分情況下,GPIO輸入的電平必須參照數(shù)據(jù)表中描述中的范圍內(nèi),如DVss或DVcc±300mV。如果GPIO用于ADC輸入

2018-11-19 15:27:59

我在學(xué)習(xí)psoc中遇到一個問題,就是我在使用SNR SNR Measurement的時候選項(xiàng)卡中是灰的。不知道是不是我的設(shè)置不對。我使用的是cy8ckit-145-40xx的開發(fā)板,使用CE210709_CapSense_Linear_Slider_and_Buttons01.cydsn code,下面是軟件截圖和main.c中main函數(shù)代碼。

2024-02-02 16:02:59

正常工作性能。AD9680按照數(shù)據(jù)手冊中的建議進(jìn)行控制,但輸入如圖10所示進(jìn)行修改。模擬輸入頻率變化范圍為10 MHz至2 GHz。CJ0的超低數(shù)值應(yīng)當(dāng)不會對ADC的SNR和SFDR性能造成影響。圖

2018-09-21 14:38:04

中。如何測量和計算NSD?對于理想的ADC:其中N是ADC的分辨率,這將定義ADC的量化噪聲電平。真正的ADC不會達(dá)到這些性能指標(biāo),因?yàn)槠湓O(shè)計中的非線性會將其實(shí)際SNR限制在理想范圍內(nèi)。換一種方式

2018-11-01 11:33:13

單片機(jī)(MCU)和傳感器測控系統(tǒng)中,經(jīng)常遇到需要模擬量傳感器輸入的情況。這種輸入的模擬量,需要由模擬數(shù)字轉(zhuǎn)換器外設(shè),簡稱ADC,來轉(zhuǎn)換為N位數(shù)字量后再由CPU進(jìn)行處理。近年來,隨著智能傳感器技術(shù)和物

2022-04-19 08:00:00

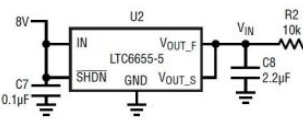

引言要獲得 ADC 的最佳 SNR 性能并不僅僅是給 ADC 輸入提供低噪聲信號,提供一個低噪聲基準(zhǔn)電壓是同等重要。雖然基準(zhǔn)噪聲在零標(biāo)度沒有影響,但是在全標(biāo)度,基準(zhǔn)上的任何噪聲在輸出代碼中都將是可見

2019-07-25 07:15:15

為符合要求的ADC輸入電壓,并且保護(hù)ADC免受過壓影響!在無數(shù)的工業(yè)、汽車、儀器儀表和眾多其他應(yīng)用中,普遍存在著一項(xiàng)挑戰(zhàn),就是如何將微小的傳感器訊號正確連接到ADC,以實(shí)現(xiàn)數(shù)字化和數(shù)據(jù)擷取。傳感器訊號通常很

2021-05-21 07:00:00

,根據(jù)此情況采用不同的試驗(yàn)方法。第二或第三脈沖可用于測量故障距離。與傳統(tǒng)的測試方法相比,第二脈沖法或第三脈沖法具有將脈沖高壓閃絡(luò)法中的復(fù)雜波形簡化為最簡單的低壓脈沖短路故障波形的優(yōu)點(diǎn),因此解釋非常簡單

2019-03-01 14:47:22

)頻譜輸出的載波頻率附近時,電源噪聲會使SFDR降低約10 dB。信噪比(SNR)SFDR取決于頻譜中的最高雜散,而SNR則取決于頻譜內(nèi)的總噪聲。SNR限制模擬信號處理系統(tǒng)識別低振幅信號的能力,并且理論上

2021-11-20 07:00:00

與4 MHz之間,故可相對簡單地應(yīng)用數(shù)字后處理以濾除或拋棄一切高于4 MHz的頻率(僅保留紅框中的內(nèi)容)。這里將需要丟棄7?8噪聲,保留所有信號能量,從而有效SNR改善9 dB。換句話說,如果知道信號

2018-08-06 09:27:37

正常工作性能。AD9680按照數(shù)據(jù)手冊中的建議進(jìn)行控制,但輸入如圖10所示進(jìn)行修改。模擬輸入頻率變化范圍為10 MHz至2 GHz。CJ0的超低數(shù)值應(yīng)當(dāng)不會對ADC的SNR和SFDR性能造成影響。圖

2018-11-01 11:25:01

開關(guān)電源高壓地與低壓地之間為什么要接電容呢?

2023-04-20 15:08:00

影響SNR 損失(由信號縮放引入)的主要因素有哪些,如何對其進(jìn)行定量分析,以及更重要的是:如何把這種影響降至最低。

2021-03-11 06:36:52

過壓情形中可能出現(xiàn)的問題、發(fā)生頻率及潛在的補(bǔ)救措施。ADC輸入的過驅(qū)一般發(fā)生于驅(qū)動放大器電軌遠(yuǎn)遠(yuǎn)大于ADC最大輸入范圍時,例如,放大器采用±15 V供電,而ADC輸入為0至5V。高壓電軌用于接受±10

2018-10-19 09:57:47

0.3V。在電路上可以等效為一個二極管串聯(lián)在輸入電壓管腳和模擬供電電壓管腳上面[1]。 圖(2)絕對最大值限制(TLC4541,ADS7951)隔離輸入電壓由于絕對最大值的限制,圖(1)中的ADC如果要采集

2019-03-15 06:45:05

深入分析吧!ADC 輸入的過驅(qū)一般發(fā)生于驅(qū)動放大器電軌遠(yuǎn)遠(yuǎn)大于 ADC 最大輸入范圍時,例如,放大器采用±15 V 供電,而 ADC 輸入為 0 至 5V。高壓電軌用于接受±10 V 輸入,同時給

2020-10-29 09:19:21

模擬輸入。結(jié)果是圖 1 中的 PScope 數(shù)據(jù),其產(chǎn)生一個 98.247dBFS SNR。圖 1:基線 FFT 顯示:對于 LTC2389-18,SNR 為 98.247dBFS該 SNR 是通過將

2018-07-19 16:23:22

@AD9226 輸入端電平轉(zhuǎn)換用DAC實(shí)現(xiàn)是不是可以改善ADC的DNL同時提高SNR

2018-09-03 14:29:18

1、容量相同,高壓是可以替代低壓的。 如果兩個同類別的CBB電容,容量相同,電壓不一樣,高壓的CBB電容完全可以替代低壓,事實(shí)上,高電壓的CBB電容,由于電壓余量更足,使用起來也會更安全一些

2021-03-16 16:40:42

±10V差分信號如何調(diào)理到差分ADC可以接受的±2.5V的范圍內(nèi)?另外采用差分放大器驅(qū)動差分ADC時,發(fā)現(xiàn)在絕對最大額定值參數(shù)中,有個差分輸入電壓電壓,一般比較小,這個參數(shù)是不是說明只能輸入的差分信號就這么大?

2018-11-16 10:09:29

±10V差分信號如何調(diào)理到差分ADC可以接受的±2.5V的范圍內(nèi)?另外采用差分放大器驅(qū)動差分ADC時,發(fā)現(xiàn)在絕對最大額定值參數(shù)中,有個差分輸入電壓電壓,一般比較小,這個參數(shù)是不是說明只能輸入的差分信號就這么大?

2023-11-27 06:06:36

對于ADC的量化噪聲,有精確的計算公式,即:SNR=6.02*N+1.76db 我有這樣一個應(yīng)用,即是我輸入信號大約1mVpp單頻,但白噪聲在全頻譜范圍內(nèi)積分到100mVpp這個量級實(shí)際的應(yīng)用是

2018-08-19 06:31:10

(SNR) 和無偽波動態(tài)范圍 (SFDR) 比較情況,證明它們的性能相同。主要特色效率從 47% 提升到 83%輸入電流從 620mA 降低到 350mA無需線性穩(wěn)壓器 (LDO) 為 ADC 穩(wěn)定供電保持 12 位性能尺寸小于 LDO 的直流/直流解決方案支持 5V 輸入電壓

2018-09-29 09:51:05

帶來諸多優(yōu)勢。我們首先來看一種常見應(yīng)用,其中需要將高電壓信號源進(jìn)行電平轉(zhuǎn)換,將其轉(zhuǎn)換為所需的 ADC 輸入范圍。圖 1 中的簡單分壓器可用來解決該問題,即將 +/-5V 信號電平轉(zhuǎn)換為 0-5V。該分

2018-09-19 14:45:39

。高低壓一般為什么不能共地,若共地會如何,我們接下來建立一個模型來分析: 上圖是不共地情況下,左邊高壓的正負(fù)端集聚正負(fù)電荷,根據(jù)電子學(xué)基礎(chǔ)理論庫倫定律,對低壓的正負(fù)兩端的作用如上圖,可以看出,當(dāng)兩者距離越遠(yuǎn)

2018-10-26 09:32:11

要找到能和模擬輸入范圍一致,同時具有適量輸入、大小符合所需和正確采樣速度的模擬數(shù)字轉(zhuǎn)換器(ADC)往往相當(dāng)困難。特別是系統(tǒng)設(shè)計師在采用寬電壓波動時,要考慮到縮小驅(qū)動ADC滿量程的輸入訊號將大幅降低

2019-07-29 06:17:57

的類型,ADC供應(yīng)商會在數(shù)據(jù)手冊或產(chǎn)品頁面上提供這一數(shù)據(jù)。電壓駐波比(VWSR)與輸入阻抗密切相關(guān),衡量目標(biāo)帶寬內(nèi)反射到負(fù)載中的功率量。該參數(shù)設(shè)置實(shí)現(xiàn)ADC滿量程輸入所需的輸入驅(qū)動電平,因此很重要。當(dāng)源

2018-09-17 15:48:29

配置下,變壓器原邊能夠?qū)崿F(xiàn)很好的匹配,而變壓器副邊的等效ADC輸入阻抗為4kΩ /3pF。不平衡的副邊阻抗與變壓器的漏感將構(gòu)成諧振電路,在450MHz至550MHz頻率范圍內(nèi)產(chǎn)生增益尖峰頻率(圖1b

2021-10-23 11:10:35

摘要:分析了二階Sigma—Delta ADC(SDADC)量化反饋電平對SNR的影響,提出了自適應(yīng)量化算法及其電路實(shí)現(xiàn).該算法能夠檢測輸入信號的強(qiáng)度、自適應(yīng)調(diào)整量化反饋電平的大小,并在

2010-05-13 09:16:45 23

23 凌力爾特推出16位ADC,可實(shí)現(xiàn)實(shí)現(xiàn)卓越的SNR

不久前,凌力爾特公司(Linear)推出 16 位 SAR ADC LTC2393-16,該器件以高達(dá) 1Msps 的采樣率實(shí)現(xiàn)卓越的 94dB SNR,而且無周期延遲。LTC

2010-01-18 08:35:51 946

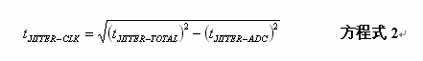

946 您在使用一個高速模數(shù)轉(zhuǎn)換器 (ADC) 時,總是期望性能能夠達(dá)到產(chǎn)品說明書載明的信噪比 (SNR) 值,這是很正常的事情。您在測試 ADC 的 SNR 時,您可能會連接一個低抖動時鐘器

2010-12-25 09:46:42 2870

2870

16位、1Msps SAR ADC實(shí)現(xiàn)94dB SNR、可測量±4.096V的寬輸入范圍

加利福尼亞州米爾皮塔斯 (MILPITAS, CA) – 2010 年 1 月 14 日 – 凌力爾特公司(Line

2010-12-26 15:40:19 1431

1431 您在使用一個高速模數(shù)轉(zhuǎn)換器 (ADC) 時,總是期望性能能夠達(dá)到產(chǎn)品說明書載明的信噪比 (SNR) 值,這是很正常的事情。您在測試 ADC 的 SNR 時,您可能會連接一個低抖動時鐘器件到

2011-01-05 10:44:48 1284

1284 本文設(shè)計一種應(yīng)用于8~-100V電源的電平位移電路。通過在常規(guī)正電源電平位移電路的基礎(chǔ)上改變低壓控制方式來實(shí)現(xiàn)從0~8V低壓邏輯輸入到8~-100V高壓驅(qū)動輸出的轉(zhuǎn)換。

2011-08-22 16:30:38 2197

2197

SNR boost是一種噪聲成型技術(shù),該技術(shù)能夠改變量化噪聲的頻譜

2013-03-14 16:02:01 17

17 如果信號源具有低頻分量,可以設(shè)計濾波器,使放大器能夠容許較大的輸入噪聲(較高的輸入噪聲通常與較低的功耗和成本有關(guān))。如果ADC限制了系統(tǒng)的帶寬,放大器需要具有足夠低的輸入參考噪聲,以便把SNR損失控制在可接受的范圍內(nèi)。

2018-03-09 14:16:08 5089

5089

我們知道,LED洗墻燈有高壓和低壓兩種規(guī)格的產(chǎn)品,那到底要怎么選擇呢?

2020-05-13 11:30:00 2220

2220 輸入共模電壓范圍(Vcm)對于包含了基帶采樣和高速ADC的通信接收機(jī)設(shè)計非常重要,尤其是采用直流耦合輸入、單電源供電的低壓電路。對于單電源供電電路,饋送到放大器和ADC的輸入信號應(yīng)該偏置在Vcm范圍以內(nèi)的直流電平,能夠消除放大器和ADC設(shè)計的一大屏障,因?yàn)椴槐卦?V保持低失真和高線性度。

2020-09-17 10:21:32 5716

5716

在使用模數(shù)轉(zhuǎn)換器(ADC)進(jìn)行設(shè)計時,人們很容易錯誤地認(rèn)為,縮小輸入信號以滿足 ADC 的滿量程范圍,會造成信噪比 (SNR)的明顯降低。需要處理寬電壓擺幅的系統(tǒng)設(shè)計人員對此更是尤為關(guān)注。此外

2020-11-19 15:05:00 18

18 16 位、1Msps SAR ADC 實(shí)現(xiàn) 94dB SNR、可測量 ±4.096V 的寬輸入范圍

2021-03-20 17:46:23 0

0 18 位、2.5Msps、無延遲 SAR ADC可實(shí)現(xiàn) 99.8dB SNR 及靈活的模擬輸入范圍

2021-03-21 01:23:54 0

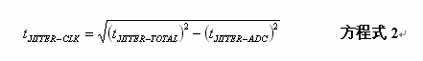

0 前言 :本文我們介紹下ADC采樣時鐘的抖動(Jitter)參數(shù)對ADC采樣的影響,主要介紹以下內(nèi)容: 時鐘抖動的構(gòu)成 時鐘抖動對ADC SNR的影響 如何計算時鐘抖動 如何優(yōu)化時鐘抖動 1.采樣理論

2021-04-07 16:43:45 7378

7378

LTC2337-18:18位,500ksps,±10.24V真雙極全差分輸入ADC,帶100dB SNR數(shù)據(jù)表

2021-04-16 10:14:24 6

6 LTC2336-18:18位,250ksps,±10.24V真雙極全差分輸入ADC,帶100dB SNR數(shù)據(jù)表

2021-04-21 19:17:32 5

5 LTC2338-18:18位,1Msps,±10.24V真雙極全差分輸入ADC,帶100dB SNR數(shù)據(jù)表

2021-04-23 16:17:14 10

10 LTC2389-16:16位,2,5mps SAR-ADC-Confightable模擬輸入Range和96dB SNR數(shù)據(jù)

2021-04-24 20:55:12 6

6 電子發(fā)燒友網(wǎng)為你提供由信號縮小所引起的SNR損失資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-25 08:52:01 13

13 LTC2326-18:18位、250ksps、±10.24V真雙極、偽差分輸入ADC,帶95dB SNR數(shù)據(jù)表

2021-04-29 20:29:50 7

7 LTC2327-18:18位、500ksps、±10.24V真雙極、偽差分輸入ADC,帶95dB SNR數(shù)據(jù)表

2021-05-09 10:23:31 2

2 LTC2328-18:18位、1Msps、±10.24V真雙極、偽差分輸入ADC,帶95dB SNR數(shù)據(jù)表

2021-05-10 18:35:46 3

3 LTC2327-16:16位、500ksps、±10.24V真雙極、偽差分輸入ADC,帶93.5dB SNR數(shù)據(jù)表

2021-05-11 12:34:00 9

9 LTC2326-16:16位、250ksps、±10.24V真雙極、偽差分輸入ADC,帶93.5dB SNR數(shù)據(jù)表

2021-05-11 17:54:57 3

3 LTC2328-16:16位、1Msps、±10.24V真雙極、偽差分輸入ADC,帶93.5dB SNR數(shù)據(jù)表

2021-05-13 15:34:33 2

2 2022-11-17 12:41:57 0

0 ADC的信噪比(SNR)是信號功率與非信號功率的比值。非信號功率包括轉(zhuǎn)換器中的熱噪聲、量化噪聲和其他殘余誤差,以奈奎斯特帶寬(f樣本/2)的 ADC。SNR通常定義為施加到ADC輸入的連續(xù)正弦波信號

2023-02-25 11:05:22 962

962

Cortex-M0處理器允許兩種形式的中斷請求:電平觸發(fā)和脈沖輸入。

2023-03-22 10:33:39 659

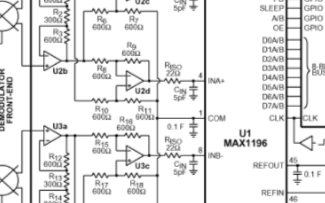

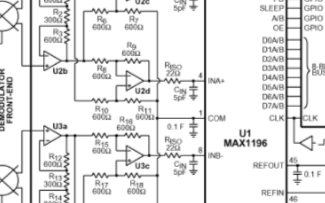

659 數(shù)據(jù)采集和通用測試測量設(shè)備中使用的精密信號鏈必須適應(yīng)寬廣的輸入電平范圍。信號鏈可能需要提供高輸入阻抗,同時支持增益和衰減,并調(diào)整共模電平以確保信號落在ADC的適當(dāng)輸入范圍內(nèi) 。 圖1中的原理圖顯示

2023-07-07 18:40:03 531

531

當(dāng)安裝差壓變送器時,正確的安裝方法對于確保設(shè)備正常運(yùn)行至關(guān)重要。下面我們將詳細(xì)介紹如何安裝差壓變送器的高壓側(cè)和低壓側(cè)。 首先,我們先來了解差壓變送器的工作原理。差壓變送器是一種用于測量流體或氣體壓力

2024-01-18 16:42:45 540

540 低壓變高壓逆變器是一種將低電壓轉(zhuǎn)換為高電壓的電路設(shè)備,常用于電力系統(tǒng)、通信設(shè)備、電子設(shè)備等領(lǐng)域。它的工作原理是通過逆變器電路將輸入的直流電變換為高頻交流電,再通過變壓器將電壓升高。 低壓變高壓逆變器

2024-01-19 10:30:31 465

465

電子發(fā)燒友App

電子發(fā)燒友App

評論