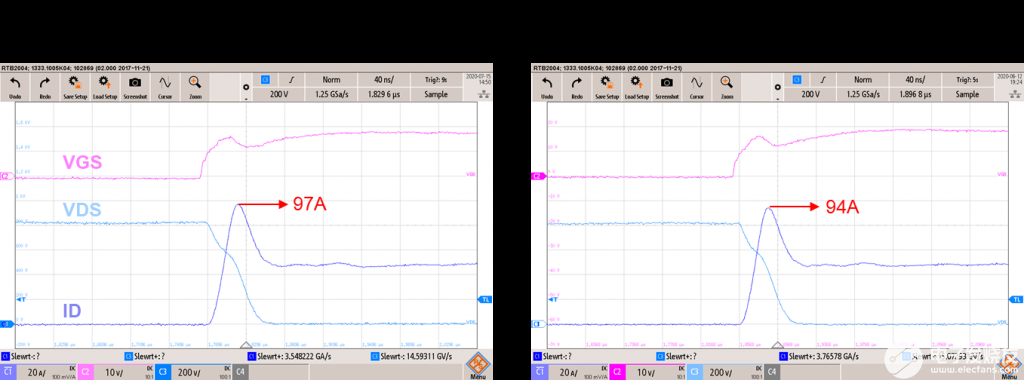

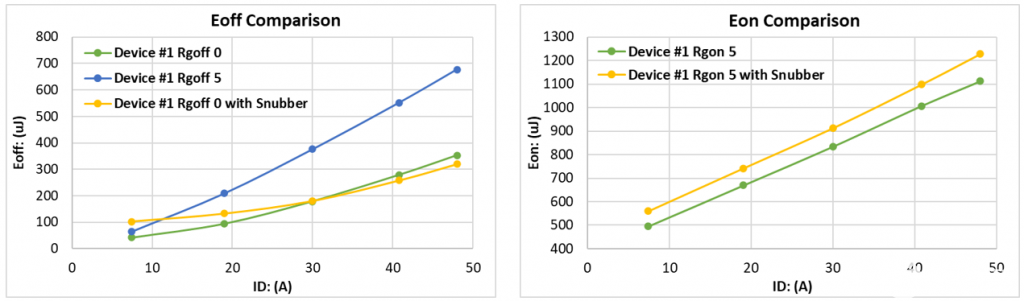

在導通數據中,原本2,742μJ的開關損耗變為1,690μJ,損耗減少了約38%。在關斷數據中也從2,039μJ降至1,462μJ,損耗減少了約30%。

2020-07-17 17:47:44 949

949

MOSFET/IGBT的開關損耗測試是電源調試中非常關鍵的環節,但很多工程師對開關損耗的測量還停留在人工計算的感性認知上,PFC MOSFET的開關損耗更是只能依據口口相傳的經驗反復摸索,那么該如何量化評估呢?

2022-10-19 10:39:23 1504

1504 MOS 管的開關損耗對MOS 管的選型和熱評估有著重要的作用,尤其是在高頻電路中,比如開關電源,逆變電路等。

2023-07-23 14:17:00 1217

1217

在高功率應用中,碳化硅(SiC)MOSFET與硅(Si)IGBT相比具有多項優勢。其中包括更低的傳導和開關損耗以及更好的高溫性能。

2023-09-11 14:55:31 347

347

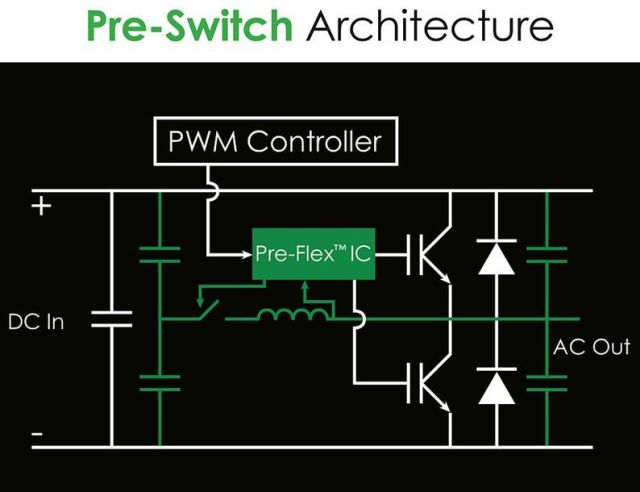

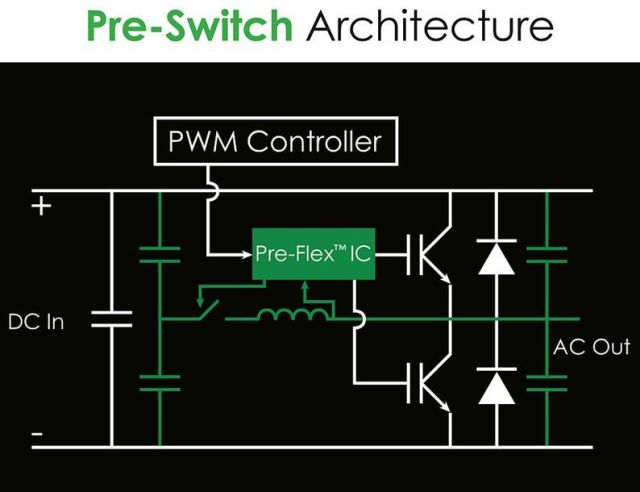

ZVS 架構在最大限度降低開關損耗、最大限度提高效率的同時,還可實現高頻率工作。

2020-03-09 11:50:54 933

933 STPOWER MDmesh K6 新系列超級結晶體管改進多個關鍵參數,最大限度減少系統功率損耗,特別適合基于反激式拓撲的照明應用。

2021-10-26 11:53:38 823

823

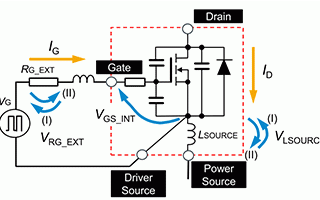

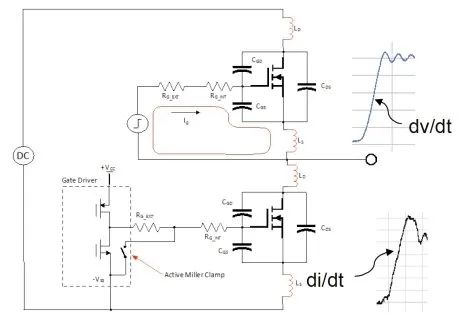

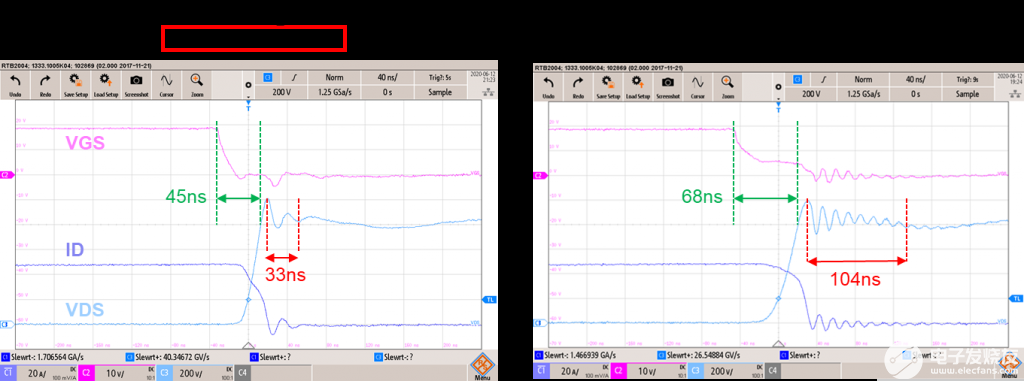

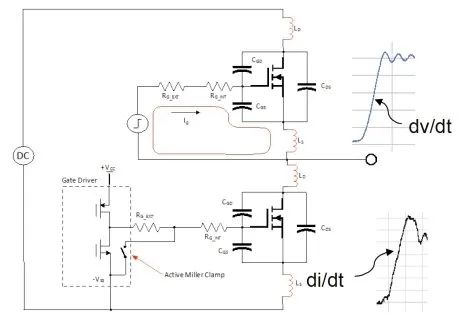

降低傳導和開關損耗)、如何最大限度降低柵極損耗、如何降低系統寄生效應的影響、如何減小導通電阻等問題。首先,考慮到關斷能量、導通能量、米勒效應等都會影響開關行為。通過降低柵極電阻(RG)或者在關閉

2019-07-09 04:20:19

時間trr快(可高速開關)?trr特性沒有溫度依賴性?低VF(第二代SBD)下面介紹這些特征在使用方面發揮的優勢。大幅降低開關損耗SiC-SBD與Si二極管相比,大幅改善了反向恢復時間trr。右側的圖表為

2019-03-27 06:20:11

電流和FRD的恢復電流引起的較大的開關損耗,通過改用SiC功率模塊可以明顯減少,因此具有以下效果:開關損耗的降低,可以帶來電源效率的改善和散熱部件的簡化(例:散熱片的小型化,水冷/強制風冷的自然風冷化

2019-05-06 09:15:52

電流和FRD的恢復電流引起的較大的開關損耗,通過改用SiC功率模塊可以明顯減少,因此具有以下效果:開關損耗的降低,可以帶來電源效率的改善和散熱部件的簡化(例:散熱片的小型化,水冷/強制風冷的自然風冷化

2019-03-25 06:20:09

。將功率 MOSFET 并聯時,設計人員必須更密切地注意如何最大限度降低這些影響,因為器件之間的電流分配不均會影響性能。例如,在開關瞬變過程中,在并聯中增加一個器件會使 di/dt 倍增,從而可能導致

2022-03-24 18:03:24

效率。圖8.將啟動電阻器添加到LMR23630轉換器開關節點的影響。EMI輻射較低,但由于開關損耗較高,因此效率有所降低。圖8顯示了LMR23630 EVM的EMI輻射掃描。對布局進行更改后,將輸入

2019-06-03 00:53:17

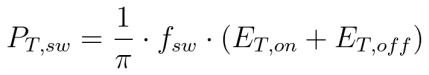

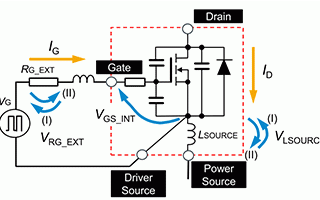

一、開關損耗包括開通損耗和關斷損耗兩種。開通損耗是指功率管從截止到導通時所產生的功率損耗;關斷損耗是指功率管從導通到截止時所產生的功率損耗。二、開關損耗原理分析:(1)、非理想的開關管在開通時,開關

2021-10-29 07:10:32

SiC-MOSFET和SiC-SBD(肖特基勢壘二極管)組成的類型,也有僅以SiC-MOSFET組成的類型。與Si-IGBT功率模塊相比,開關損耗大大降低處理大電流的功率模塊中,Si的IGBT與FRD

2018-12-04 10:14:32

請問如何最大限度的減小在汽車環境中的EMI?

2021-04-13 06:57:09

使用絕緣柵雙極晶體管(IGBT)。但隨著半導體技術的進步,碳化硅 (SiC) 金屬氧化物半導體場效應晶體管 (MOSFET) 能夠以比 IGBT 更高的頻率進行開關,通過降低電阻和開關損耗來提高效率

2022-11-02 12:02:05

如圖片所示,為什么MOS管的開關損耗(開通和關斷過程中)的損耗是這樣算的,那個72pF應該是MOS的輸入電容,2.5A是開關電源限制的平均電流

2018-10-11 10:21:49

本帖最后由 小小的大太陽 于 2017-5-31 10:06 編輯

MOS管的導通損耗影響最大的就是Rds,而開關損耗好像不僅僅和開關的頻率有關,與MOS管的結電容,輸入電容,輸出電容都有關系吧?具體的關系是什么?有沒有具體計算開關損耗的公式?

2017-05-31 10:04:51

本帖最后由 張飛電子學院魯肅 于 2021-1-30 13:21 編輯

本文詳細分析計算功率MOSFET開關損耗,并論述實際狀態下功率MOSFET的開通過程和自然零電壓關斷的過程,從而使電子

2021-01-30 13:20:31

增大,但是高頻化可以使得模塊電源的變壓器磁芯更小,模塊的體積變得更小,所以可以通過開關頻率去優化開通損耗、關斷損耗和驅動損耗,但是高頻化卻會引起嚴重的EMI問題。采用跳頻控制方法,在輕負載情況下,通過降低

2019-09-25 07:00:00

。設計挑戰然而,SiC MOSFET 技術可能是一把雙刃劍,在帶來改進的同時,也帶來了設計挑戰。在諸多挑戰中,工程師必須確保:以最優方式驅動 SiC MOSFET,最大限度降低傳導和開關損耗。最大限度

2017-12-18 13:58:36

的IGBT模塊相比,具有1)可大大降低開關損耗、2)開關頻率越高總體損耗降低程度越顯著 這兩大優勢。下圖是1200V/300A的全SiC功率模塊BSM300D12P2E001與同等IGBT的比較。左圖

2018-11-27 16:37:30

描述PMP9638 參考設計使用具有諧振環谷底開關控制器的 UCC28740 初級側調節 (PSR) 反激式,從通用交流輸入產生雙路直流輸出 12V/2A 和 3.3V/0.5A。此設計可最大限度

2018-08-10 08:38:17

/0.5A。此設計可最大限度減少 FET 中的開關損耗以提供高效率。UCC28740 的電流調節特性可提供精確的電流限制保護。特性通用輸入 85 -264VAC雙路輸出輸出恒定電壓和恒定電流模式輸出保持時間減少開關損耗`

2015-03-16 14:50:16

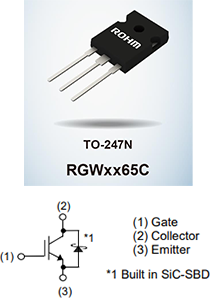

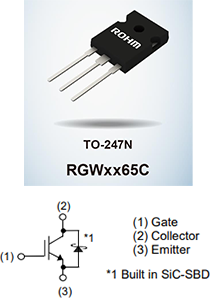

內置SiC肖特基勢壘二極管的IGBT:RGWxx65C系列內置SiC SBD的Hybrid IGBT在FRD+IGBT的車載充電器案例中開關損耗降低67%關鍵詞* ? SiC肖特基勢壘二極管(SiC

2022-07-27 10:27:04

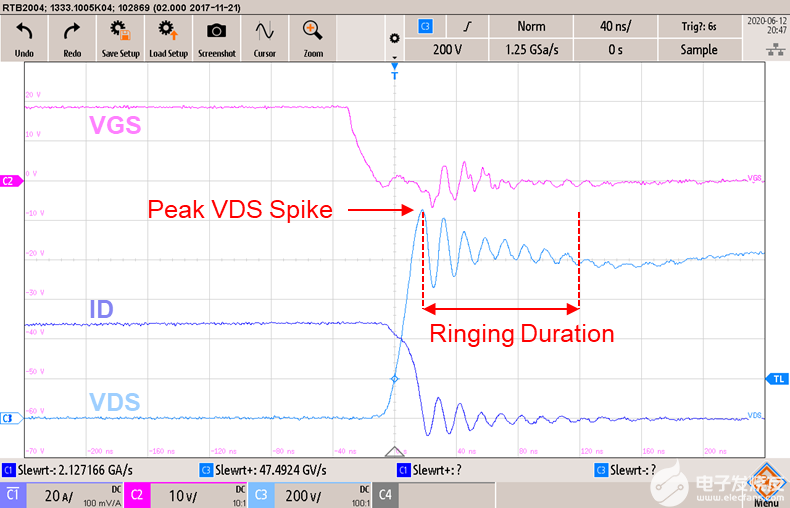

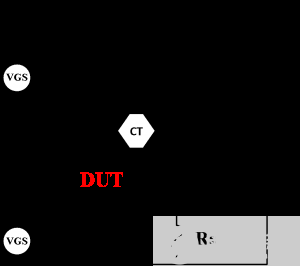

一個高質量的開關電源效率高達95%,而開關電源的損耗大部分來自開關器件(MOSFET和二極管),所以正確的測量開關器件的損耗,對于效率分析是非常關鍵的。那我們該如何準確測量開關損耗呢?一、開關損耗

2021-11-18 07:00:00

開關條件得以改善,降低硬開關的開關損耗和開關噪聲,從而 提高了電路的效率。 圖1 理想狀態下軟開關和硬開關波形比較圖軟開關包括軟開通和軟關斷兩個過程: 理想的軟開通過程是:開關器件兩端的電壓先下

2019-08-27 07:00:00

,提高開關的速度,從而降低開關損耗,但是過高的開關速度會引起EMI的問題。(2)提高柵極驅動電壓也可以提高開關的速度,降低開關損耗。同時,高的柵極驅動電壓會增加驅動損耗,特別是輕載的時候,對效率

2017-03-06 15:19:01

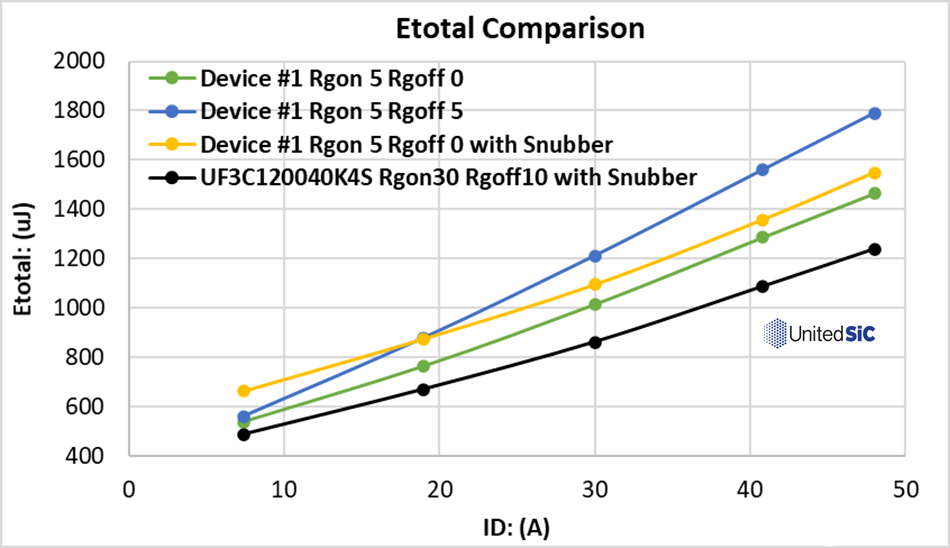

過程中的開關損耗。開關損耗內容將分成二次分別講述開通過程和開通損耗,以及關斷過程和和關斷損耗。功率MOSFET及驅動的等效電路圖如圖1所示,RG1為功率MOSFET外部串聯的柵極電阻,RG2為功率

2017-02-24 15:05:54

描述 此項 25W 的設計在反激式拓撲中使用 UCC28740 來最大限度降低空載待機功耗,并使用 UCC24636同步整流控制器來最大限度減少功率 MOSFET 體二極管傳導時間。此設計還使用來

2022-09-23 06:11:58

的優勢。大幅降低開關損耗SiC-SBD與Si二極管相比,大幅改善了反向恢復時間trr。右側的圖表為SiC-SBD與Si-FRD(快速恢復二極管)的trr比較。恢復的時間trr很短,二極管關斷時的反向電流

2018-12-04 10:26:52

在數字無線通信產品測試中最大限度地降低電源瞬態電壓......

2019-08-19 07:42:24

最大限度提高Σ-Δ ADC驅動器的性能

2021-01-06 07:05:10

如何最大限度的去實現LTE潛力?

2021-05-25 06:12:07

在本文中,我們將解釋針對不同的應用和工作條件仔細選擇IGBT變體如何提高整體系統效率。IGBT模塊中的損耗大致可分為兩類:傳導開關眾所周知,對于特定電壓下的任何給定過程,降低傳導損耗的努力將導致

2023-02-27 09:54:52

和傳導噪聲的擔心。雖然,咱們官網上的應用筆記《isoPower器件的輻射控制建議》提供了最大限度降低輻射的電路和布局指南。實踐證明,通過電路優化(降低負載電流和電源電壓)和使用跨隔離柵拼接電容(通過PCB

2018-10-11 10:40:15

如何更加深入理解MOSFET開關損耗?Coss產生開關損耗與對開關過程有什么影響?

2021-04-07 06:01:07

1394物理層所具備的優勢是什么?如何采用1394技術最大限度地優化安全攝像頭網絡?

2021-05-25 06:25:20

布局電源板以最大限度地降低EMI:第3部分

2019-08-16 06:13:31

布局電源板以最大限度地降低EMI:第1部分

2019-09-05 15:36:07

布局電源板以最大限度地降低EMI:第2部分

2019-09-06 08:49:33

,?uk拓撲也提供開關電流。在圖1中,它們表現為熱回路(藍色)。熱回路指的是一組具有快速di/dt瞬變的軌跡。為了最大限度降低開關電流產生的干擾,以及伴隨的寄生電容,此回路占用的空間面積必須盡可能達到最小

2020-06-20 07:57:28

電流和FRD的恢復電流引起的較大的開關損耗,通過改用SiC功率模塊可以明顯減少,因此具有以下效果:開關損耗的降低,可以帶來電源效率的改善和散熱部件的簡化(例:散熱片的小型化,水冷/強制風冷的自然風冷化

2019-03-12 03:43:18

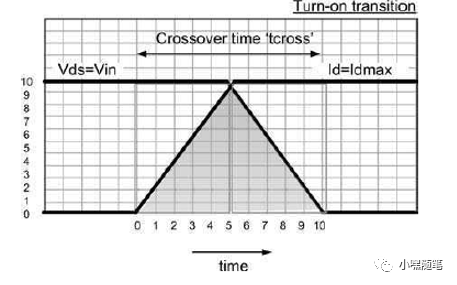

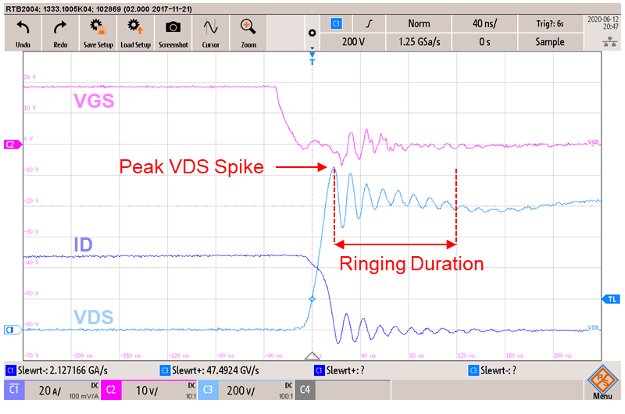

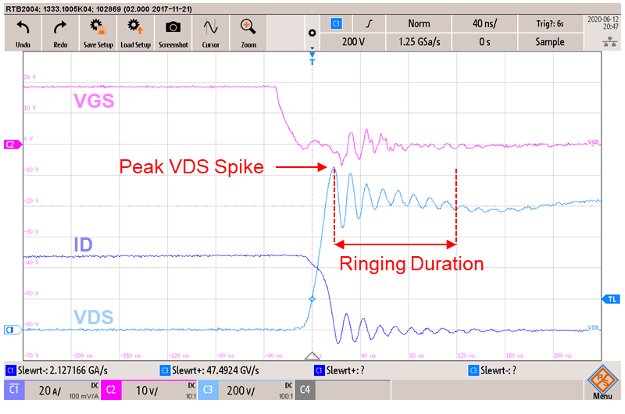

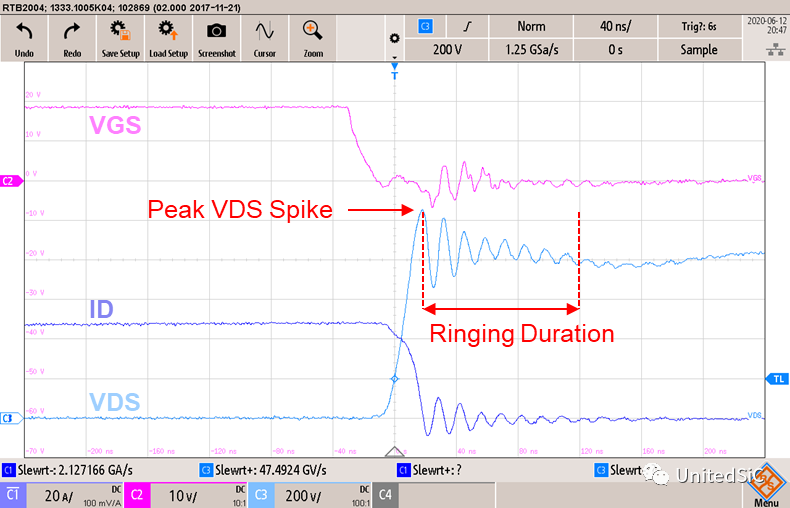

歡迎回到直流/直流轉換器數據表系列。鑒于在上一篇文章中我介紹了系統效率方面的內容,在本文中,我將討論直流/直流穩壓器部件的開關損耗,從第1部分中的圖3(此處為圖1)開始:VDS和ID曲線隨時間變化

2018-08-30 15:47:38

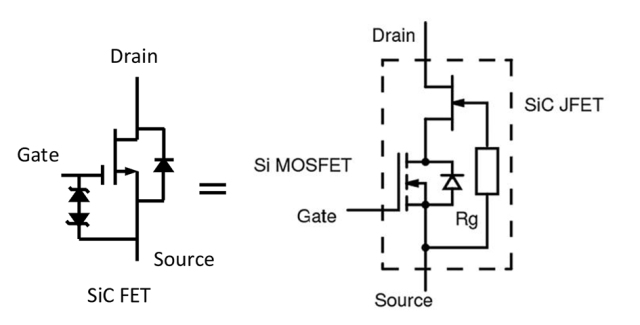

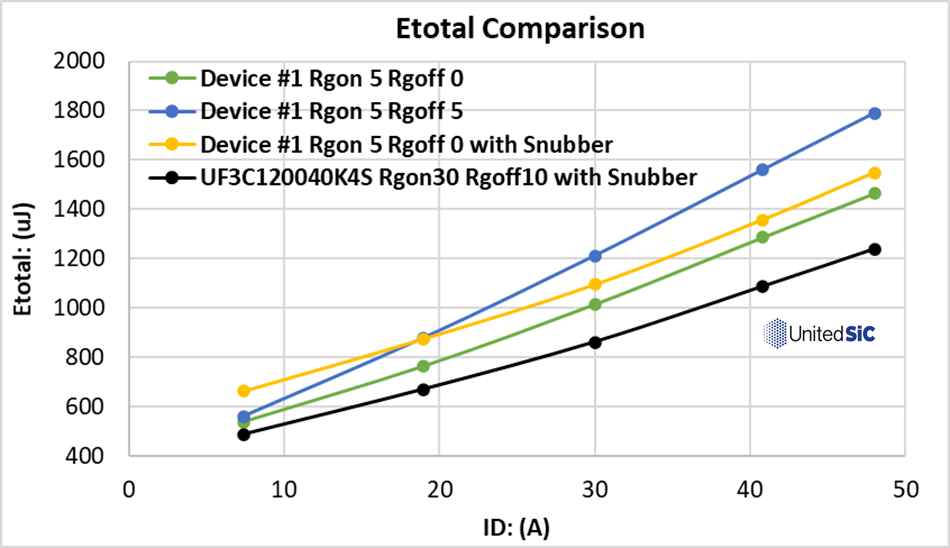

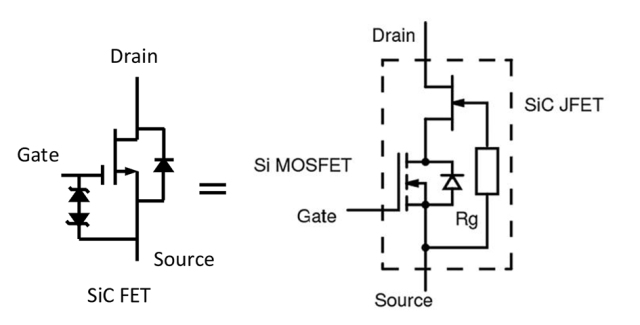

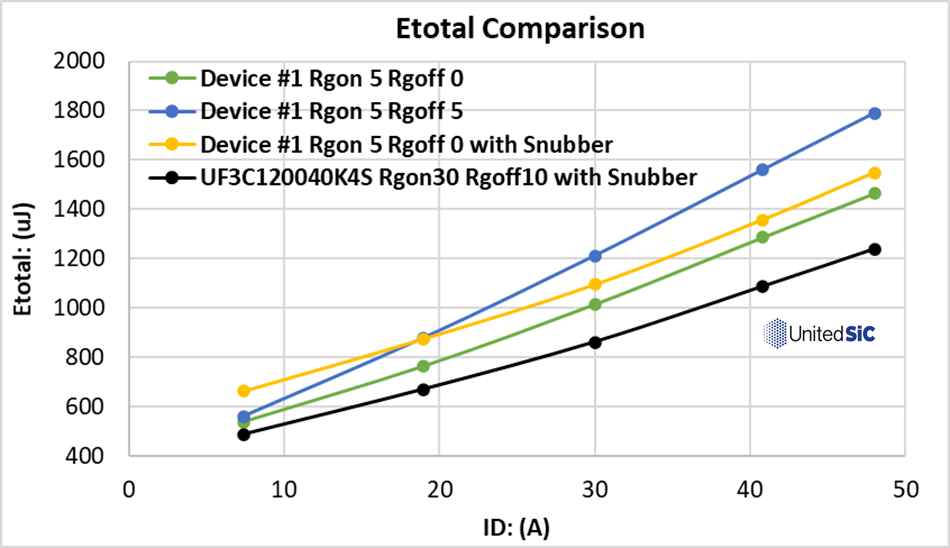

了。 固有優勢加上最新進展 碳化硅的固有優勢有很多,如高臨界擊穿電壓、高溫操作、具有優良的導通電阻/片芯面積和開關損耗、快速開關等。最近,UnitedSiC采用常關型共源共柵的第三代SiC-FET器件已經

2023-02-27 14:28:47

,在這兩種情況下估算時間t3作為MOSFET的上升和下降時間,您可使用等式4估算開關損耗:開關損耗取決于頻率和輸入電壓。因此,輸入電壓和開關頻率較高時,總效率相對降低。在輕負載時,LM2673非同步降壓

2018-06-05 09:39:43

今天開始看電源界神作《開關電源設計》(第3版),發現第9頁有個名詞,叫“交流開關損耗”,不明白是什么意思,有沒有哪位大蝦知道它的意思啊?謝謝了!!

2013-05-28 16:29:18

)”一詞所表達的,電路的優先事項一定需要用最大公約數來實現優化。對此,將在Tech Web的基礎知識“SiC功率元器件”中進行解說。另外,您還可以通過ROHM官網下載并使用本次議題的基礎,即Application Note“利用驅動器源極引腳改善開關損耗(PDF)”。

2020-07-01 13:52:06

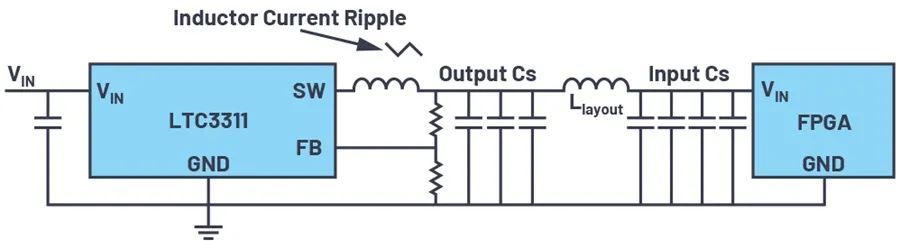

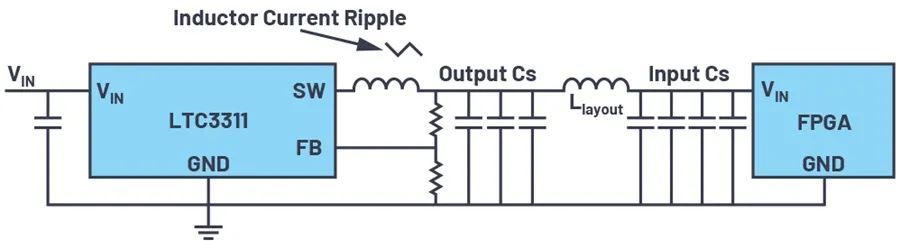

噪聲的傳導回路面積較大,進一步推動輻射發射的產生。在第 3 部分中,我將全面介紹降壓穩壓器電路中影響 EMI 性能和開關損耗的感性和容性寄生元素。通過了解相關電路寄生效應的影響程度,可以采取適當的措施將

2020-11-03 07:54:52

在第 3 部分中,我將全面介紹降壓穩壓器電路中影響 EMI 性能和開關損耗的感性和容性寄生元素。通過了解相關電路寄生效應的影響程度,可以采取適當的措施將影響降至最低并減少總體 EMI 信號。一般來說

2022-11-09 07:38:45

圖1:開關損耗讓我們先來看看在集成高側MOSFET中的開關損耗。在每個開關周期開始時,驅動器開始向集成MOSFET的柵極供應電流。從第1部分,您了解到MOSFET在其終端具有寄生電容。在首個時段(圖

2022-11-16 08:00:15

DN371- 高效率2相升壓轉換器可最大限度地降低輸入和輸出電流紋波

2019-08-15 07:27:09

理解功率MOSFET的開關損耗

本文詳細分析計算開關損耗,并論述實際狀態下功率MOSFET的開通過程和自然零電壓關斷的過程,從而使電子工程師知道哪個參數起主導作用并

2009-10-25 15:30:59 3320

3320 筆記本最大限度延長電池的使用壽命

本文將討論如何有效地使用電池,以及最大限度地延長電池的使用壽命。本文將只討論最新的XTRA這幾個使用了鋰電池的系列,對于較

2010-04-19 09:20:34 851

851 為了有效解決金屬-氧化物半導體場效應晶體管(MOSFET)在通信設備直流-48 V緩啟動應用電路中出現的開關損耗失效問題,通過對MOSFET 柵極電荷、極間電容的闡述和導通過程的解剖,定位了MOSFET 開關損耗的來源,進而為緩啟動電路設計優化,減少MOSFET的開關損耗提供了技術依據。

2016-01-04 14:59:05 38

38 FPGA平臺實現最小開關損耗的SVPWM算法

2016-04-13 16:12:11 10

10 基于DSP的最小開關損耗SVPWM算法實現。

2016-04-18 09:47:49 7

7 使用示波器測量電源開關損耗。

2016-05-05 09:49:38 0

0 MOSFET/IGBT的開關損耗測試是電源調試中非常關鍵的環節,但很多工程師對開關損耗的測量還停留在人工計算的感性認知上,PFC MOSFET的開關損耗更是只能依據口口相傳的經驗反復摸索,那么該如何量化評估呢?

2017-11-10 08:56:42 6345

6345 1、CCM 模式開關損耗

CCM 模式與 DCM 模式的開關損耗有所不同。先講解復雜 CCM 模式,DCM 模式很簡單了。

2018-01-13 09:28:57 8163

8163

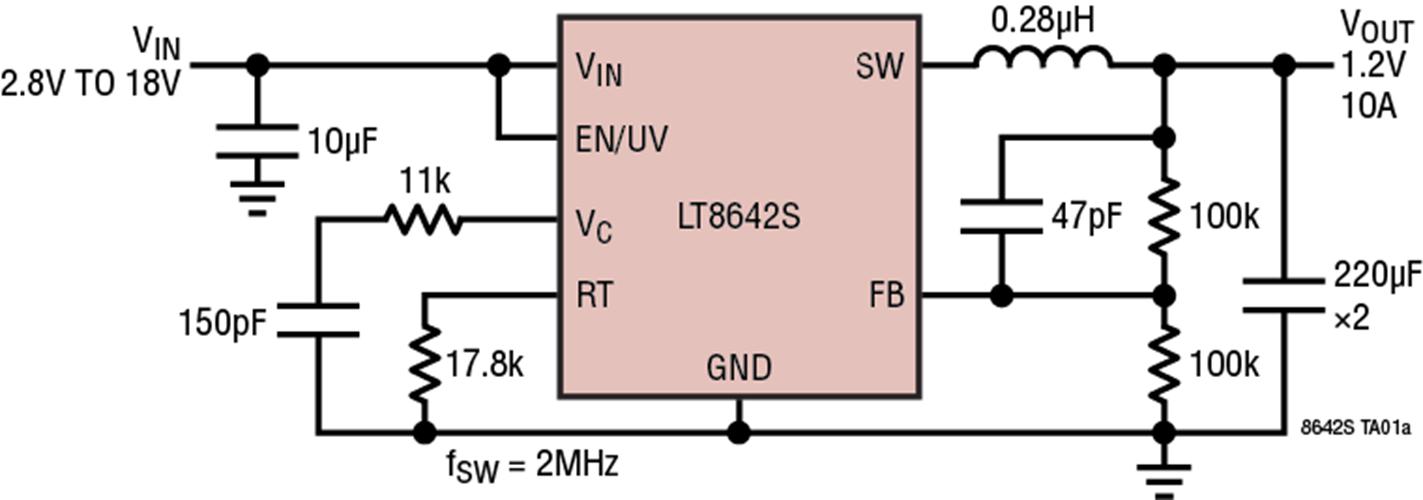

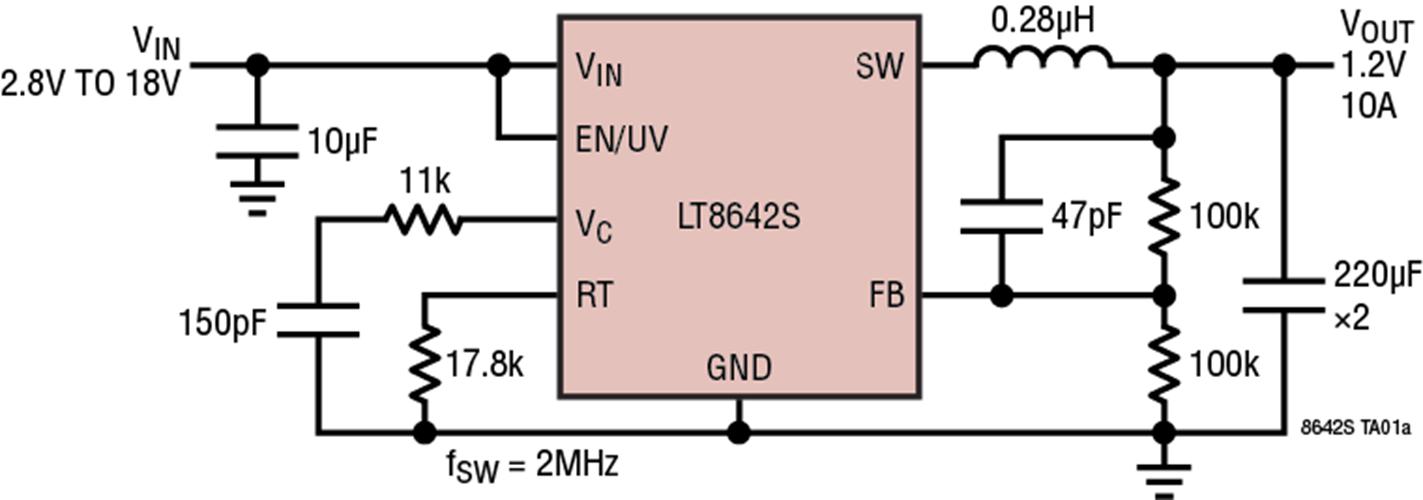

LT?8642S 同步降壓穩壓器采用第二代 Silent Switcher 架構,最大限度地降低了 EMI 發射,同時在高開關頻率下實現了高效率。這包括集成旁路電容器以優化所有內部快速電流環路

2018-07-11 16:38:00 1463

1463

一個高質量的開關電源效率高達95%,而開關電源的損耗大部分來自開關器件(MOSFET和二極管),所以正確的測量開關器件的損耗,對于效率分析是非常關鍵的。那我們該如何準確測量開關損耗呢?

2019-06-26 15:49:45 721

721 一個高質量的開關電源效率高達95%,而開關電源的損耗大部分來自開關器件(MOSFET和二極管),所以正確的測量開關器件的損耗,對于效率分析是非常關鍵的。那我們該如何準確測量開關損耗呢?

2019-06-27 10:22:08 1926

1926 功率MOSFET的開關損耗分析。

2021-04-16 14:17:02 48

48 一、開關損耗包括開通損耗和關斷損耗兩種。開通損耗是指功率管從截止到導通時所產生的功率損耗;關斷損耗是指功率管從導通到截止時所產生的功率損耗。二、開關損耗原理分析:(1)、非理想的開關管在開通時,開關

2021-10-22 10:51:06 11

11 ,熱損耗極低。 開關設備極大程度上決定了SMPS的整體性能。開關器件的損耗可以說是開關電源中最為重要的一個損耗點,課件開關損耗測試是至關重要的。接下來普科科技PRBTEK就開關損耗測試方案中的探頭應用進行介紹。 上圖使用MSO5配合THDP0200及TCP003

2021-11-23 15:07:57 1095

1095 與碳化硅 (SiC)FET 和硅基FET 相比,氮化鎵 (GaN) 場效應晶體管 (FET) 可顯著降低開關損耗和提高功率密度。

2022-02-08 16:32:44 4

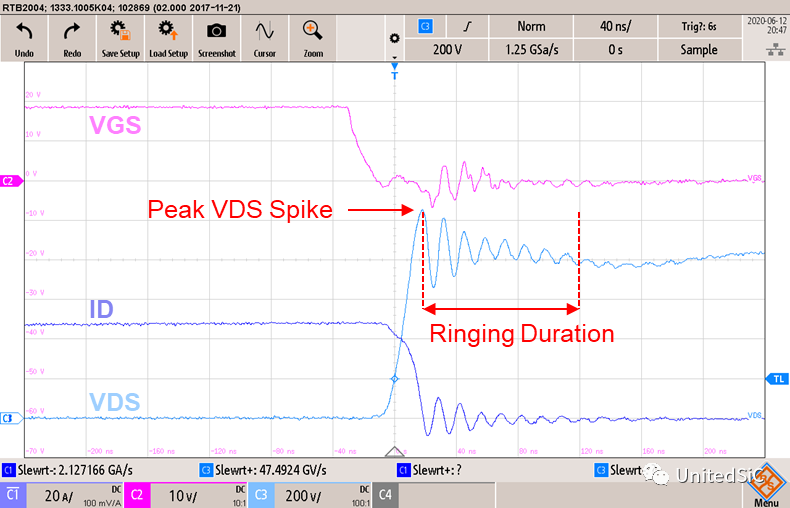

4 SiC FET 速度極快,邊緣速率為 50 V/ns 或更高,這對于最大限度地減少開關損耗非常有用,但由此產生的 di/dt 可能達到每納秒數安培。這會通過封裝和電路電感產生高電平的電壓過沖和隨后

2022-08-04 09:30:05 729

729

。此外,今天的開關元件沒有非常高的運行速度,不幸的是,在轉換過程中不可避免地會損失一些能量(幸運的是,隨著新電子元件的出現,這種能量越來越少)。讓我們看看如何使用“LTspice”仿真程序來確定 SiC MOSFET 的開關損耗率。

2022-08-05 08:05:07 5941

5941

尺寸和重量并降低成本。人工智能 (AI) 正在為推動電動汽車的自主性和效率提供重要支持,包括努力消除開關損耗以確保快速晶體管換向。

2022-08-09 08:02:02 1058

1058

UnitedSiC(現已被Qorvo收購)750V UJ4C/SC SiC FET,采用D2PAK-7L封裝。UJ4C/SC系列器件是750V碳化硅場效應晶體管(SiC FET),借助D2PAK-7L封裝選項提供低開關損耗、在更高速度下提升效率,同時提高系統功率密度。

2022-10-27 16:33:29 739

739 一次性按鈕開關幫助最大限度延長閑置時間

2022-11-04 09:52:06 0

0 時鐘采樣系統最大限度減少抖動

2022-11-04 09:52:12 0

0 如何最大限度減少線纜設計中的串擾

2022-11-07 08:07:26 1

1 AN2014_設計者如何最大限度使用ST單片機

2022-11-21 17:07:41 0

0 碳化硅 (SiC) MOSFET 的快速開關速度、高額定電壓和低導通 RDS(on) 使其對電源設計人員極具吸引力,這些設計人員不斷尋找提高效率和功率密度的方法,同時保持系統簡單性。

2022-11-23 11:45:13 1286

1286

如何最大限度地提高電子設備中能量收集的效率

2022-12-30 09:40:14 615

615 開關過程中,穿越線性區(放大區)時,電流和電壓產生交疊,形成開關損耗。其中,米勒電容導致的米勒平臺時間,在開關損耗中占主導作用。

2023-01-17 10:21:00 978

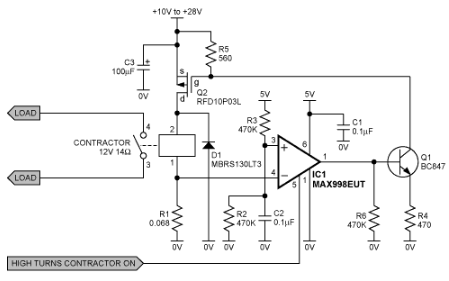

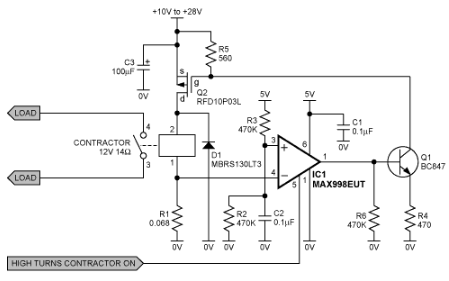

978 該接觸器電路自振蕩,以在接通時最大限度地降低功耗。比較器根據需要進行切換,以在遲滯限值之間上下斜坡調整線圈電流。隨著電源電壓的增加,電路開始自振蕩。

2023-01-16 15:56:44 577

577

內置SiC肖特基勢壘二極管的IGBT:RGWxx65C系列內置SiC SBD的Hybrid IGBT在FRD+IGBT的車載充電器案例中開關損耗降低67%關鍵詞 ? SiC肖特基勢壘二極管(...

2023-02-08 13:43:19 434

434

全SiC功率模塊與現有的IGBT模塊相比,具有1)可大大降低開關損耗、2)開關頻率越高總體損耗降低程度越顯著 這兩大優勢。

2023-02-08 13:43:22 673

673

-接下來,請您介紹一下驅動器源極引腳是如何降低開關損耗的。首先,能否請您對使用了驅動器源極引腳的電路及其工作進行說明?Figure 4是具有驅動器源極引腳的MOSFET的驅動電路示例。

2023-02-16 09:47:49 457

457

從某個外企的功率放大器的測試數據上獲得一個具體的感受:導通損耗60W開關損耗251。大概是1:4.5 下面是英飛凌的一個例子:可知,六個管子的總功耗是714W這跟我在項目用用的那個150A的模塊試驗測試得到的總功耗差不多。 導通損耗和開關損耗大概1:2

2023-02-23 09:26:49 15

15 上一篇文章中探討了同步整流降壓轉換器的功率開關--輸出端MOSFET的傳導損耗。本文將探討開關節點產生的開關損耗。開關損耗:見文識意,開關損耗就是開關工作相關的損耗。在這里使用PSWH這個符號來表示。

2023-02-23 10:40:49 623

623

全SiC功率模塊與現有的功率模塊相比具有SiC與生俱來的優異性能。本文將對開關損耗進行介紹,開關損耗也可以說是傳統功率模塊所要解決的重大課題。

2023-02-24 11:51:28 496

496

圖1所示為基于MAX1744/5控制器IC的簡化降壓轉換器,具有異步整流功能。由于二極管的關斷特性,主開關(Q1)的導通開關損耗取決于開關頻率、輸入環路的走線電感(由C1、Q1和D1組成)、主開關

2023-03-10 09:26:35 557

557

CCM 模式與 DCM 模式的開關損耗有所不同。先講解復雜 CCM 模式,DCM 模式很簡單了。

2023-07-17 16:51:22 4680

4680

電子發燒友網站提供《切換以最大限度地利用SAN.pdf》資料免費下載

2023-09-01 11:23:25 0

0 最大限度地減少SIC FETs EMI和轉換損失

2023-09-27 15:06:15 236

236

同步buck電路的mos自舉驅動可以降低mos的開關損耗嗎? 同步buck電路的MOS自舉驅動可以降低MOS的開關損耗 同步Buck電路是一種常見的DC/DC降壓轉換器,它具有高效、穩定、可靠的特點

2023-10-25 11:45:14 523

523 最大限度保持系統低噪聲

2023-11-27 16:58:00 161

161

使用SiC MOSFET時如何盡量降低電磁干擾和開關損耗

2023-11-23 09:08:34 333

333

如何最大限度減小電源設計中輸出電容的數量和尺寸?

2023-12-15 09:47:18 183

183

正在加载...

電子發燒友App

電子發燒友App

評論