上一篇文章中對ADC的概況進(jìn)行了簡單的介紹,這篇內(nèi)容主要針對ADC的一些技術(shù)方面的問題做探討。

一、28nm工藝下的ADC

隨著無線通信向高速、寬帶方向發(fā)展,對于無線信號(hào)接收機(jī)提出了越來越高的要求。特別是在電子戰(zhàn)領(lǐng)域、信號(hào)情報(bào)偵察應(yīng)用方向?qū)τ诟邘挕⑿⌒突⑤p型化以及低功率(Size, Weight and Power: SWaP)ADC的需求更加迫切。

65nm制程的ADC在向更高速的、高帶寬的數(shù)據(jù)變換器擴(kuò)展的時(shí)候遇到了一些固有的障礙:工藝制程、帶寬限制等方面。28nm的先進(jìn)工藝制程正在打破這個(gè)界限,從而使得原本一些無法考慮實(shí)現(xiàn)的接收機(jī)的架構(gòu)或者性能得到很大的促進(jìn)。接下來我們就從幾個(gè)角度來看看28nm的ADC具有哪些應(yīng)用的優(yōu)勢。

在寬帶的雷達(dá)電子戰(zhàn)領(lǐng)域中,系統(tǒng)的研發(fā)人員在設(shè)計(jì)高性能、低SWaP的接收機(jī)的時(shí)候會(huì)面臨很多挑戰(zhàn)。在接收機(jī)中ADC扮演了一個(gè)非常重要的角色,以至于有時(shí)候會(huì)因?yàn)锳DC的性能而采用不同的接收機(jī)架構(gòu)。

ADC的性能參數(shù)包括了采樣率、帶寬、分辨率,都會(huì)影響射頻RF鏈路以及后端的DSP。高采樣率和帶寬能夠一次性捕捉分析寬帶的RF信號(hào),同時(shí)降低掃描時(shí)間、保持更高分辨率,能夠提高分析的性能,降低虛警概率。

28nm的晶體管能夠降低寄生的柵極電容,實(shí)現(xiàn)更快的開關(guān)速度,同時(shí)僅需要很低的功率來驅(qū)動(dòng)即可。28nm的工藝不僅能夠提高單個(gè)晶體管的性能,同時(shí)能夠在單位面積上集成更多的晶體管以獲得更優(yōu)異的信號(hào)處理能力。28nm工藝下實(shí)現(xiàn)的高采樣率ADC在電子戰(zhàn)方向中的信號(hào)情報(bào)偵察、電子戰(zhàn)防御(Electronic Protect:EP)、電子戰(zhàn)支援(ElectronicSupport:ES)應(yīng)用需求十分迫切。

采用28nm的工藝,同時(shí)也帶給了半導(dǎo)體廠商更多的設(shè)計(jì)思路。能夠在ADC中集成更多的混合信號(hào)處理單元以保證在同等的SWaP條件下提高ADC的性能。

例如NCO(Numerically Controlled Oscillators:數(shù)控振蕩器,其作用類似于本振源,提供一個(gè)混頻信號(hào))和DDC(Digital Downconverters:數(shù)字下變頻器,其作用是將高頻信號(hào)在數(shù)字域進(jìn)行下變頻,降低頻率以便于后續(xù)處理)。

在提高了采樣率和帶寬之后面臨著有大量的數(shù)據(jù)吞吐(GSPS),在研發(fā)過程中就需要找到能夠與之相匹配的數(shù)據(jù)接口傳輸數(shù)據(jù)。目前市場上很多28nm的ADC數(shù)據(jù)輸出速率已經(jīng)超過了10Gbps,采用的接口通常為JESD204B,但是引入由串行和解串路由Gbps帶來的JESD相關(guān)電路布局、信號(hào)完整性分析方面的問題,進(jìn)一步提升設(shè)計(jì)研發(fā)的難度。

可以通過集成NCO、DDC實(shí)現(xiàn)降采樣,變換到基帶,結(jié)合數(shù)字濾波能夠保持很高速的數(shù)據(jù)輸出速率。所以集成NCO、DDC以實(shí)現(xiàn)降采樣是保持高速數(shù)據(jù)的有效方法。

另外一方面,如果JESD204B輸出的數(shù)據(jù)沒有經(jīng)過降采樣,一直維持在非常高速的傳輸下,所需要的功率、產(chǎn)生的功耗將會(huì)非常大。因此,采用抽取濾波的方式能夠降低功耗。

總的來說,在電子戰(zhàn)領(lǐng)域?qū)τ诩闪薔CO、DDC的高速的、高帶寬、高分辨率的ADC的應(yīng)用能夠極大的提升接收機(jī)的性能,先進(jìn)工藝制程的ADC能夠有效的解決低SWaP與高速數(shù)據(jù)之間的矛盾關(guān)系,為實(shí)現(xiàn)高性能的接收機(jī)提供了有效的解決方案。

二、ADC芯片的工藝方案

在ADC方向上,CMOS工藝已經(jīng)成為一種主流的工藝實(shí)現(xiàn)方式。CMOS工藝具有較低的寄生電容、電感以及電阻效應(yīng),是Δ-Σ、SAR以及Pipeline架構(gòu)(基于開關(guān)電容型的電路)的ADC的主要實(shí)現(xiàn)工藝。

BiCMOS的工藝成本較高,在一些性能要求較高的模擬前端需要使用。例如混頻器、采樣保持電路、輸入放大器以及高精度參考電壓都利用雙極型實(shí)現(xiàn)的,其他的功能電路利用CMOS實(shí)現(xiàn)。

GaAs在ADC方面的應(yīng)用主要在6-8bit,采樣率大于1G的flash架構(gòu)中使用。這一類的ADC通常成本、功率都比較高,但是市場較為小。

三、ADC對接收機(jī)系統(tǒng)架構(gòu)的影響

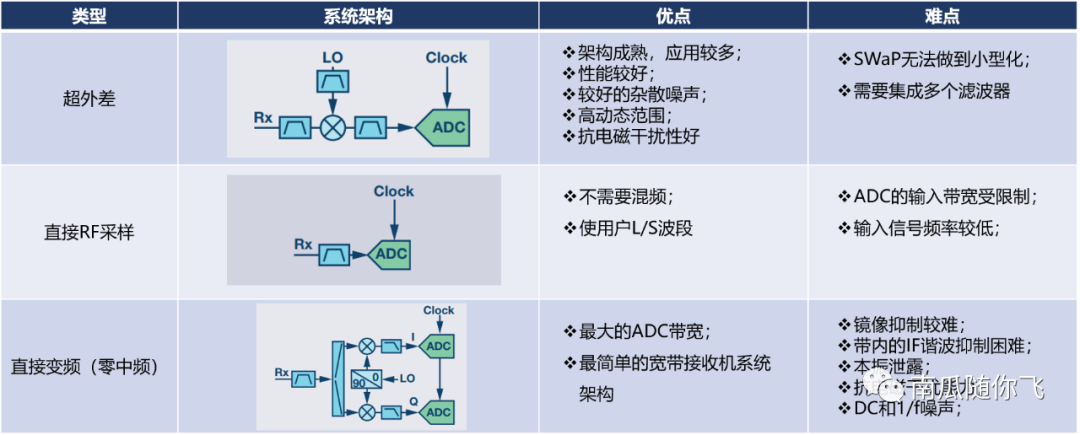

接收機(jī)按照不同的RF信號(hào)變頻處理方式可以分為三種:超外差式、直接RF采樣、直接下變頻(零中頻)。

1.超外差接收機(jī)

RF信號(hào)通過與本振信號(hào)混頻后變到中頻IF,在進(jìn)行后入處理。超外差式接收機(jī)應(yīng)用的時(shí)間早、架構(gòu)較為成熟、性能表現(xiàn)穩(wěn)定。通常會(huì)采用較高的IF頻率結(jié)合濾波器來抑制鏡像頻率干擾,或者通過多級下變頻器逐級變頻實(shí)現(xiàn)鏡頻抑制。

同架構(gòu)圖中可以看出來,超外差接收機(jī)的架構(gòu)較為復(fù)雜。通常需要很大的驅(qū)動(dòng)功率以及電路布局才能夠獲得較合適的工作帶寬,與現(xiàn)在系統(tǒng)對低SWaP的需求相違背。

2. 超外差接收機(jī)

直接RF采樣是市場和研發(fā)人員一直在追求的接收機(jī)架構(gòu)。目前主要的障礙在直接射頻采樣的速度、大輸入帶寬與ADC的速率之間不匹配的問題。這也是限制這類架構(gòu)向更高頻段發(fā)展的重要原因。

目前主要應(yīng)用還是集中在較高的奈奎斯特頻段(采樣率與信號(hào)頻率之間的關(guān)系)的L/S波段的接收機(jī)中。下一步隨著ADC的發(fā)展,將會(huì)逐步向C-band,X-band擴(kuò)展。

3. 零中頻

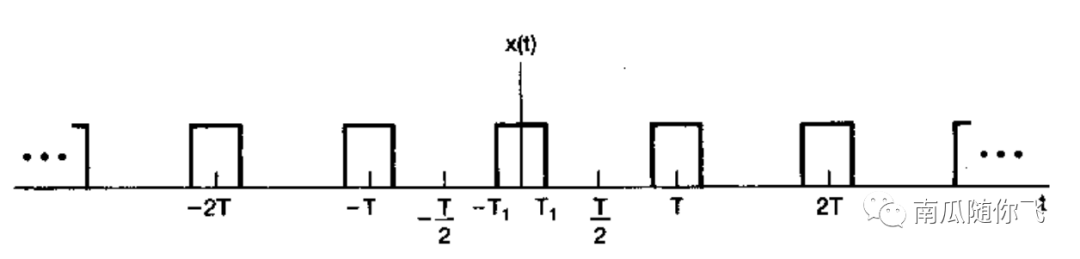

零中頻是對數(shù)據(jù)變換帶寬利用效率最高的架構(gòu)。ADC通常工作在第一奈奎斯特采樣區(qū)間。信號(hào)通過與正交的本振信號(hào)混頻過后形成兩路I/Q正交信號(hào),然后分別進(jìn)行ADC。

主要的難點(diǎn)在于保持較好的I/Q信號(hào)的平衡,以獲得較好的鏡像抑制、本振泄露以及直流偏移等。目前通過集成整個(gè)零中頻信號(hào)鏈路并結(jié)合數(shù)字校準(zhǔn)技術(shù)已經(jīng)解決了這些問題,進(jìn)一步打開了該類型接收機(jī)的應(yīng)用市場,在多種應(yīng)用場合已經(jīng)逐步采用這種類型的接收機(jī)。

以超外差結(jié)構(gòu)為例,介紹ADC對其架構(gòu)的影響。通常在低速的ADC時(shí)代,因?yàn)楣ぷ鲙捙c輸入頻率的比例很大,使得通過單級下變頻直接做低頻濾波較為困難,很多微波接收機(jī)通常都是采用多級變頻的模式。

圖片來源:ADI官網(wǎng)

隨著ADC的采樣率、輸入帶寬的提高,使得單級變頻架構(gòu)逐步進(jìn)入應(yīng)用。典型的框架如下圖所示:

圖片來源:ADI官網(wǎng)

接收鏈路最開始是一個(gè)低噪放,但是在有些特定的應(yīng)用領(lǐng)域,例如面對大功率電子對抗設(shè)備會(huì)在前端加載一個(gè)限幅器降低輸入功率的幅度。隨后經(jīng)過帶通濾波、放大、低通濾波、下變頻、低通濾波、放大,在進(jìn)入ADC之前需要做一個(gè)抗混疊濾波,濾除掉一些干擾、雜散以及諧波信號(hào)。信號(hào)進(jìn)入ADC進(jìn)行數(shù)據(jù)變換,后續(xù)的電路都是圍繞著ADC進(jìn)行設(shè)計(jì)的。

有沒有必要在每一種接收機(jī)或者設(shè)備中都采用高速、高精度的ADC?這是需要結(jié)合具體的應(yīng)用場景來討論的。當(dāng)面對的是寬帶、高速的信號(hào),典型的就是電子電子對抗、大數(shù)據(jù)量通信、頻譜測試測量等,高速的ADC就顯得必不可少。

從系統(tǒng)架構(gòu)方面來看,能夠有效降低系統(tǒng)復(fù)雜程度;從性能方面來說,能夠提高高吞吐量的數(shù)據(jù)采集變換。同時(shí)結(jié)合不同的接收機(jī)架構(gòu),在面對射頻直采和零中頻的應(yīng)用,高性能的ADC的需求更加迫切,大帶寬、高采樣率等特點(diǎn)有助于研發(fā)人員采用緊湊的系統(tǒng)架構(gòu);

超外差結(jié)構(gòu)中,高性能的ADC也能夠在一定程度上降低系統(tǒng)的復(fù)雜程度,但是如果需要考慮到性價(jià)比、成本方面的問題,如果能夠采用成本較低的多級變頻的方案+性能適合的ADC來實(shí)現(xiàn)也是一種方案。

綜上,考慮到架構(gòu)性價(jià)比、成本、性能優(yōu)勢以及復(fù)雜程度,雖然不是每一種接收機(jī)架構(gòu)都需要用到高速、高分辨率的ADC,但是高速的ADC能夠極大的降低接收機(jī)的架構(gòu)復(fù)雜度、提高性能,這也正式復(fù)合了系統(tǒng)朝著低SWaP方向發(fā)展的技術(shù)和應(yīng)用趨勢。

電子發(fā)燒友App

電子發(fā)燒友App

評論