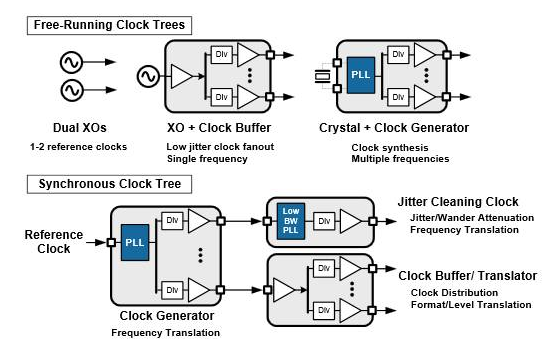

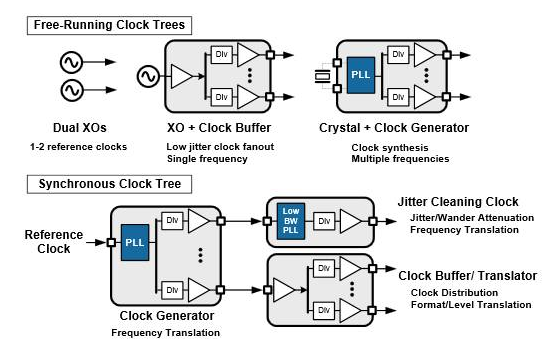

樹設(shè)計(jì)時(shí), “ 一成不變 ” 的策略并不適用,優(yōu)化時(shí)鐘樹以滿足性能和成本的要求取決于多種因素,包括系統(tǒng)架構(gòu)、集成電路( IC )時(shí)序需求(頻率、信號格式等)和終端應(yīng)用的抖動需求。

2017-10-31 09:45:13 5550

5550

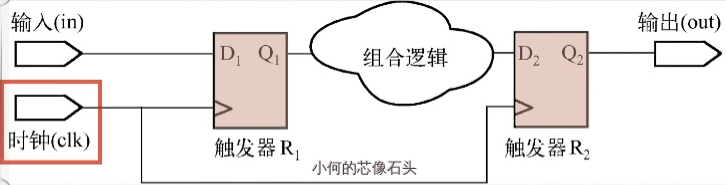

時(shí)鐘使能電路是同步設(shè)計(jì)的重要基本電路,在很多設(shè)計(jì)中,雖然內(nèi)部不同模塊的處理速度不同,但是由于這些時(shí)鐘是同源的,可以將它們轉(zhuǎn)化為單一的時(shí)鐘電路處理。在FPGA的設(shè)計(jì)中,分頻時(shí)鐘和源時(shí)鐘的skew不容易

2020-11-10 13:53:41 4795

4795

電路設(shè)計(jì)人員了解到,這些老化效應(yīng)會改變器件的 Vt,進(jìn)而減慢時(shí)鐘信號的上升和下降時(shí)間。隨著時(shí)間的推移,這些老化效應(yīng)會扭曲時(shí)鐘的占空比,實(shí)際上會導(dǎo)致時(shí)鐘電路出現(xiàn)故障。

2022-10-17 11:38:10 678

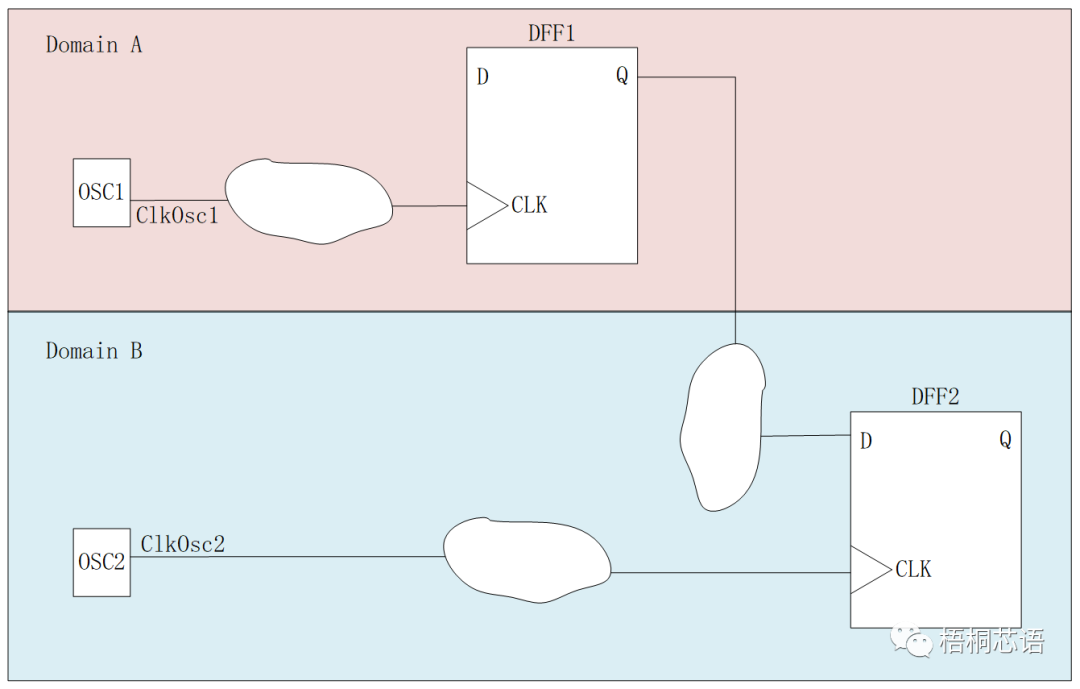

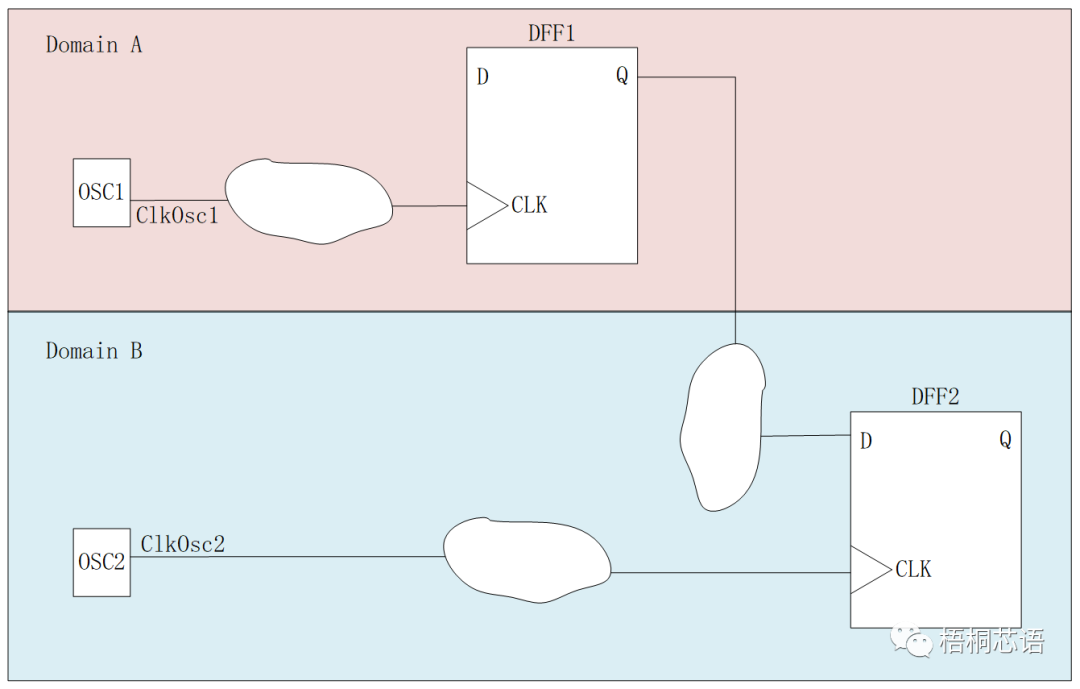

678 在一個(gè)復(fù)雜的SoC(System on Chip)系統(tǒng)中,不可能只有一個(gè)時(shí)鐘。我們一般認(rèn)為,一個(gè)時(shí)鐘控制的所有寄存器集合處于該時(shí)鐘的時(shí)鐘域中。

2023-08-01 15:48:20 1052

1052

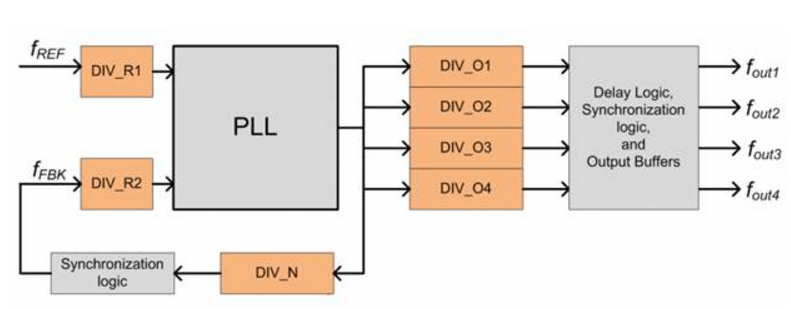

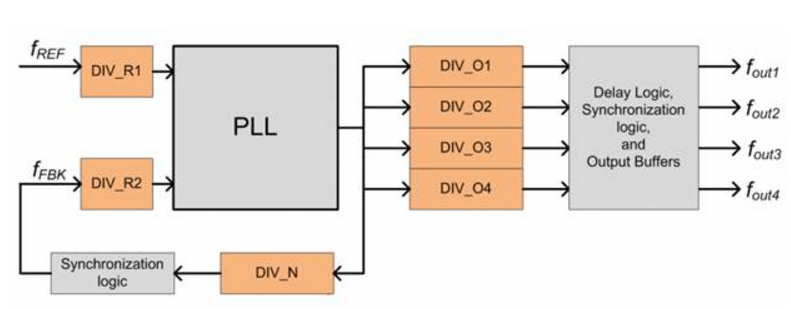

25MHz的時(shí)鐘源如何得到4路200MHz的時(shí)鐘信號

2019-01-10 10:19:05

MPC92433 - 1428 MHz Dual Output LVPECL Clock Synthesizer - Freescale Semiconductor, Inc

2022-11-04 17:22:44

你好現(xiàn)在遇到一個(gè)問題,MPC5644A芯片的時(shí)鐘配置方式是從同事那里學(xué)來的,發(fā)現(xiàn)如果要將MPC5644A系統(tǒng)配置為80M,必須先配置為40M,想知道這個(gè)過程是否合理?如果我直接把系統(tǒng)時(shí)鐘配置成80M

2023-04-18 07:54:14

種噪聲有可能非常嚴(yán)重,導(dǎo)致系統(tǒng)的性能大大降低。即使你使用了高性能器件(當(dāng)然價(jià)錢也很高),如果你使用的時(shí)鐘由于種種原因?qū)е逻呇匕l(fā)生了抖動,也會讓你的系統(tǒng)產(chǎn)生災(zāi)難性的后果。實(shí)際電路中的時(shí)鐘信號會發(fā)

2019-05-06 09:16:07

時(shí)鐘設(shè)備設(shè)計(jì)使用 I2C 可編程小數(shù)鎖相環(huán) (PLL),可滿足高性能時(shí)序需求,這樣可以產(chǎn)生零 PPM(百萬分之一)合成誤差的頻率。高性能時(shí)鐘 IC 具有多個(gè)時(shí)鐘輸出,用于驅(qū)動打印機(jī)、掃描儀和路由器等

2019-08-12 06:50:43

在很多設(shè)計(jì)中,雖然內(nèi)部不同模塊的處理速度不同,但是由于這些時(shí)鐘是同源的,可以將它們轉(zhuǎn)化為單一的時(shí)鐘電路處理。在FPGA的設(shè)計(jì)中,分頻時(shí)鐘和源時(shí)鐘的skew不容易控制,難以保證分頻時(shí)鐘和源時(shí)鐘同相

2013-01-08 09:06:49

非常多,但是并非所有外設(shè)都需要系統(tǒng)時(shí)鐘這么高的頻率,比如看門狗和RTC只需要幾十K的時(shí)鐘即可。同一個(gè)電路,時(shí)鐘越快,功耗越大,同時(shí)抗電磁干擾能力也會越弱,所以對于較為復(fù)雜的MCU一般采用多時(shí)鐘源的方法來

2021-08-12 06:45:07

的主要缺點(diǎn)是,您放棄了實(shí)現(xiàn)dc、地震、音頻和更高帶寬應(yīng) 用的絕對最高可能性能所需的自定義和優(yōu)化。在急于重用和完 成設(shè)計(jì)的過程中,往往會犧牲精確性能。其容易忽略和忽視 的一個(gè)主要方面是時(shí)鐘。在本文中,我們將討論時(shí)鐘的重要性, 并為正確設(shè)計(jì)高性能轉(zhuǎn)換器提供指導(dǎo)。

2021-01-27 07:27:36

的晶體時(shí)鐘源給不同的芯片提供時(shí)鐘信號,會提高系統(tǒng)成本,增大電路板面積,而且會帶來時(shí)間同步的問題,好的系統(tǒng)設(shè)計(jì)會選擇使用單一主時(shí)鐘振蕩器作為時(shí)鐘源,再將時(shí)鐘信號通過時(shí)鐘緩沖分配給整個(gè)系統(tǒng)中的各個(gè)芯片。時(shí)鐘

2022-06-08 12:54:33

時(shí)鐘設(shè)備設(shè)計(jì)使用 I2C 可編程小數(shù)鎖相環(huán) (PLL),可滿足高性能時(shí)序需求,這樣可以產(chǎn)生零 PPM(百萬分之一)合成誤差的頻率。高性能時(shí)鐘 IC 具有多個(gè)時(shí)鐘輸出,用于驅(qū)動打印機(jī)、掃描儀和路由器等

2018-08-27 09:46:58

檢測電路,以適應(yīng)于不同電機(jī)及不同控制方式的要求;同時(shí)由于采用了高性能的MCU,更多類型的通信接口可被靈活應(yīng)用,如:URAT、CAN、RJ45等。

2019-07-09 08:24:02

在外的高速PCB布線使還會帶來串?dāng)_、信號完整性等非常嚴(yán)重的問題。如果可以在中低端FPGA上實(shí)現(xiàn)高速時(shí)鐘數(shù)據(jù)恢復(fù)電路,則可降低成本且提高整個(gè)電路系統(tǒng)的性能。 &

2009-10-24 08:38:08

AD芯片采用外部時(shí)鐘時(shí),外部時(shí)鐘源可以是不規(guī)則的TTL電平嗎?

該TTL電平具體表現(xiàn)為,頻率由低到高,再由高到低,最大100K,每一個(gè)電平高電平是恒定的,低電平在不停的變化。

這樣的TTL電平能作為AD芯片的采樣時(shí)鐘嗎

2023-12-22 08:31:46

由鎖相環(huán)構(gòu)成的間接式頻率合成器在無線通信領(lǐng)域發(fā)揮著非常重要的作用。通常采用鎖相頻率合成器的輸出信號來作為無線接收機(jī)中的本振信號,以使直接頻率調(diào)制器、頻率解調(diào)器能夠從輸入信號中再生載波。如果用MB1504/MAX2620的話怎么能夠?qū)崿F(xiàn)鎖相時(shí)鐘頻率源?

2021-04-14 06:47:07

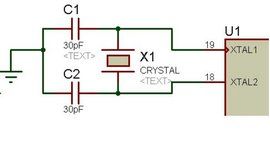

STM32時(shí)鐘時(shí)鐘源:時(shí)鐘源用來為環(huán)形脈沖發(fā)生器提供頻率穩(wěn)定且電平匹配的方波時(shí)鐘脈沖信號。它通常由石英 晶體振蕩器和與非門組成的正反饋振蕩電路組成,其輸出送至環(huán)形脈沖發(fā)生器。晶振脈沖時(shí)鐘頻率(又譯

2021-08-18 07:21:56

STM32有以下4個(gè)時(shí)鐘源:高速外部時(shí)鐘(HSE):以外部晶振作時(shí)鐘源,晶振頻率可取范圍為4~16MHz,我們一般采用8MHz的晶振。高速內(nèi)部時(shí)鐘(HSI): 由內(nèi)部RC振蕩器產(chǎn)生,頻率為8MHz

2021-08-12 07:35:54

時(shí)鐘源的作用無論是小型單片機(jī)還是像STM32這樣高級單片機(jī),它們工作的核心都是大規(guī)模的時(shí)序邏輯電路,而驅(qū)動時(shí)序邏輯電路的關(guān)鍵則是準(zhǔn)確而又穩(wěn)定的時(shí)鐘源。它的作用就像小學(xué)在操場上做廣播體操時(shí)...

2021-08-19 07:06:25

Xilinx Virtex 4 和高性能時(shí)鐘合成器 LMX2531 來滿足 9 位 ENOB 高速數(shù)字轉(zhuǎn)換器的系統(tǒng)要求。 特性2 個(gè) GSPS 模數(shù)轉(zhuǎn)換通道大于 9 位 ENOB 超寬輸入頻率范圍面向測試和測量系統(tǒng)的低成本雙通道高速數(shù)字轉(zhuǎn)換器原型

2022-09-20 07:01:22

有人要問,采用一個(gè)系統(tǒng)時(shí)鐘不是很簡單嗎?為什么STM32要有多個(gè)時(shí)鐘源呢?因?yàn)槭紫萐TM32本身非常復(fù)雜,外設(shè)非常的多,但是并不是所有外設(shè)都需要系統(tǒng)時(shí)鐘這么高的頻率,比如看門狗以及RTC只需要幾十k

2021-08-12 06:41:28

什么是時(shí)鐘?? 時(shí)鐘是單片機(jī)運(yùn)行的基礎(chǔ),時(shí)鐘信號推動單片機(jī)內(nèi)各個(gè)部分執(zhí)行相應(yīng)的指令。時(shí)鐘系統(tǒng)就是CPU的脈搏,決定CPU速率。片機(jī)有了時(shí)鐘,才能夠運(yùn)行執(zhí)行指令,才能夠做其他的處理 (點(diǎn)燈,串口

2022-02-14 07:52:45

fpga的時(shí)鐘信號,該fpga_clk經(jīng)過 fpga內(nèi)部以后,再路由某個(gè)管腳將新命名的 ext1_clk與ext2_clk輸出給外部ic,100Mhz的ext1_clk與ext2_clk因此稱為供源時(shí)鐘。

2019-08-06 07:42:55

的時(shí)鐘源。隨著集成電路加工中功能器件的尺寸縮小,器件電源電壓也呈下降趨勢,包括PLL和其它混合信號功能所用的電源。然而,PLL的關(guān)鍵元件——“壓控振蕩器”(VCO)的實(shí)用技術(shù)要求并未隨之大幅降低。許多高性能

2019-06-26 06:39:37

的引腳。然而,電路板正在接收 200KHz 時(shí)鐘信號,這讓我很困惑?這可以做到嗎?板上沒有晶體,所以它要么使用那個(gè)時(shí)鐘源,要么使用內(nèi)部時(shí)鐘。它的最高頻率要求是 115,200 異步 UART,因此內(nèi)部時(shí)鐘

2023-01-30 07:58:17

如何解決高溫下STM32采用內(nèi)部晶振作為系統(tǒng)時(shí)鐘的時(shí)鐘源導(dǎo)致時(shí)序紊亂問題?

2022-02-14 07:09:59

參考頻率源,電路和普通電路一樣。但要注意確保MODCLK腳在復(fù)位時(shí)為高,否則系統(tǒng)會出錯(cuò)。 本系統(tǒng)采用Motorola公司推薦的4.194MHz晶振頻率,同時(shí)通過寫時(shí)鐘合成控制寄存器SYNCR中的相關(guān)位

2012-11-15 16:22:38

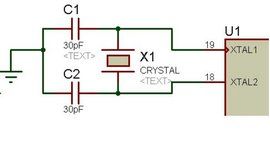

尤其適合于產(chǎn)品線豐富批量大的生產(chǎn)者。無源晶振其缺陷是信號質(zhì)量較差,通常需要精確匹配外圍電路(用于信號匹配的電容、電感、電阻等),更換不同頻率的晶體時(shí)周邊配置電路需要做相應(yīng)的調(diào)整。建議采用精度較高的石英

2013-04-18 15:58:58

是否可以將ETR引腳時(shí)鐘信號作為定時(shí)器的時(shí)鐘源呢?基于STM32定時(shí)器ETR信號有何應(yīng)用?

2021-11-23 07:46:35

晶體(XTAL)輸入之間的自動切換,最小化切換,引起的瞬態(tài),在頻率容差范圍內(nèi)工作壽命。小數(shù)N分頻PLL設(shè)計(jì)基于成熟的高性能,低抖動頻率合成器產(chǎn)品組合,可最大限度地提高網(wǎng)絡(luò)性能,而整數(shù)N分頻PLL則提供通用時(shí)鐘,可用作CPU和現(xiàn)場可編程門陣列(FPGA)參考時(shí)鐘

2019-02-25 09:40:01

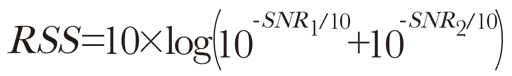

SNR 性能的影響以及怎樣降低一個(gè)噪聲時(shí)鐘源的抖動。作為基線,DC1826A-A 的時(shí)鐘輸入采用一個(gè)羅德與施瓦茨 SMB100A RF 發(fā)生器來驅(qū)動,并由 Stanford Research SR1 提供

2018-07-19 16:23:22

系統(tǒng)時(shí)鐘那么高的頻率,如果都用高速時(shí)鐘勢必造成浪費(fèi)。同一個(gè)電路,時(shí)鐘越快功耗越大、抗電磁干擾能力越弱。復(fù)雜的MCU采用多時(shí)鐘源的方法來解決這些問題。如下圖,是STM32的時(shí)鐘系統(tǒng)框圖。轉(zhuǎn)存失敗重新上傳取消如上圖左邊的部分,看到STM32有4個(gè)獨(dú)立時(shí)鐘...

2021-08-19 06:33:34

已經(jīng)有段時(shí)間了。但是,在要求快速切換速度、低相位噪聲或低雜散信號電平的場合,有必要使用更為復(fù)雜的架構(gòu)。通過正確的設(shè)計(jì)方法,結(jié)合使用現(xiàn)代低成本高集成度的PLL和直接數(shù)字合成器(DDS)集成電路(IC

2019-07-08 06:10:06

大家好,我現(xiàn)在設(shè)計(jì)一個(gè)時(shí)鐘源,由壓控振蕩器輸出10MHz時(shí)鐘,需要經(jīng)過一個(gè)時(shí)鐘合成器輸出62MHz(jitter值小于2ps)作為高精度ADC和FPGA的時(shí)鐘源,可是我在ADI官網(wǎng)上尋找了很久,發(fā)現(xiàn)

2018-09-25 11:36:31

描述適用于 GSPS 數(shù)據(jù)轉(zhuǎn)換器的低成本、高性能時(shí)鐘解決方案。此參考設(shè)計(jì)討論如何使用低噪聲頻率合成器 TRF3765 為 4 GSPS 模數(shù)轉(zhuǎn)換器 (ADC12J4000) 生成采樣時(shí)鐘。實(shí)驗(yàn)展示了

2018-08-16 06:56:42

頻率合成器的高性能架構(gòu)實(shí)現(xiàn)技術(shù)詳解

2021-04-07 06:48:49

系統(tǒng)時(shí)鐘源的比較選擇及高性能PLL的發(fā)展趨勢安森美半導(dǎo)體公司 供稿在所有電子系統(tǒng)中,時(shí)鐘相當(dāng)于心臟,時(shí)鐘的性能和穩(wěn)定性直接決定著整個(gè)系統(tǒng)的性能。典型的系統(tǒng)時(shí)序

2009-12-20 09:28:06 31

31 無線基礎(chǔ)設(shè)施、寬帶和儀器儀表應(yīng)用通常需要高性能的時(shí)鐘電路,它們主要需要時(shí)鐘的器件是高速數(shù)據(jù)轉(zhuǎn)換器。這些系統(tǒng)的時(shí)鐘電路所需的幾個(gè)關(guān)鍵性能指標(biāo)包括低相位噪聲和抖

2009-07-06 18:37:55 449

449

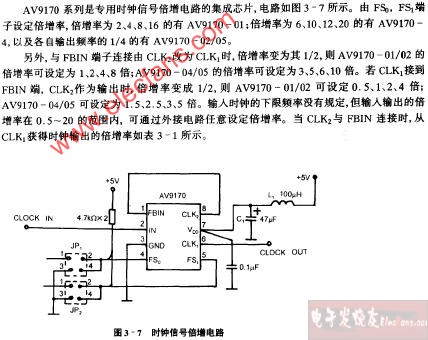

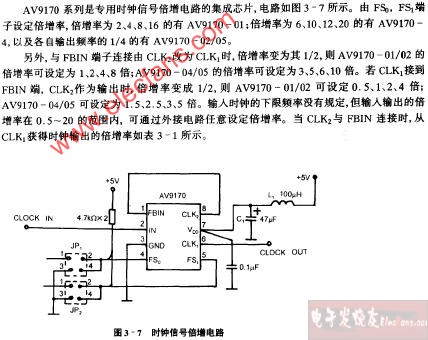

時(shí)鐘信號倍增電路圖

2009-07-14 17:18:36 741

741

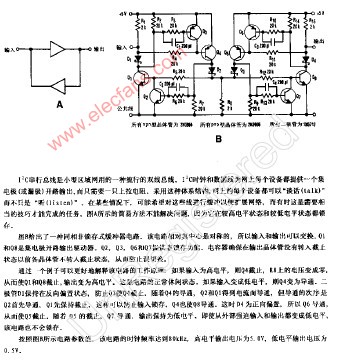

IC數(shù)據(jù)和時(shí)鐘時(shí)鐘線緩沖電路

2009-09-12 11:57:02 1372

1372

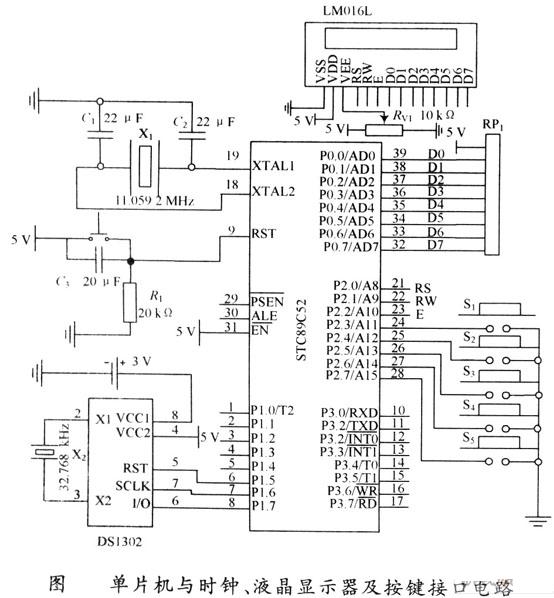

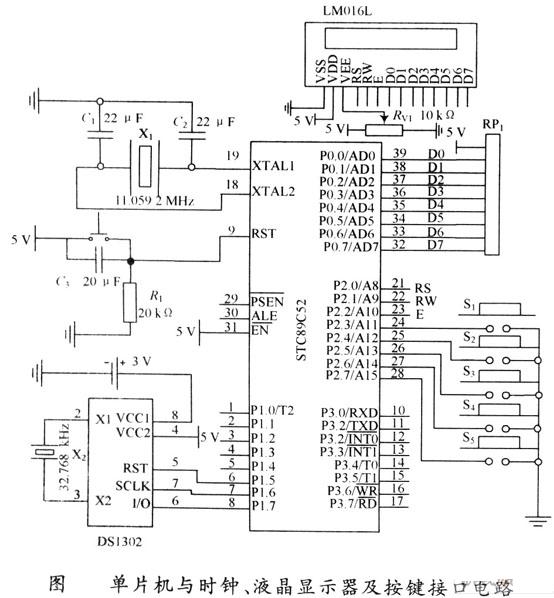

單片機(jī)與液晶顯示器及按鍵接口電路

單片機(jī)與時(shí)鐘芯片DS1302接口電路部分:DS1302是美國DALLAS公司推出的一種高性能、低功耗的實(shí)時(shí)時(shí)鐘芯片,采用SPI三線

2010-02-16 12:04:02 2283

2283

MAX3679A高性能四路輸出時(shí)鐘發(fā)生器(Maxim)

Maxim推出用于以太網(wǎng)設(shè)備的高性能、四路輸出時(shí)鐘發(fā)生器MAX3679A。器件采用低噪聲

2010-04-14 16:51:49 778

778 DS31415是一個(gè)靈活的,高性能的不同頻率轉(zhuǎn)換時(shí)間和頻率合成中的應(yīng)用集成電路。就其三個(gè)輸入和四個(gè)輸出時(shí)鐘時(shí)鐘,每個(gè)設(shè)備可以接受幾乎任何關(guān)系或產(chǎn)生2kHz和750MHz的頻率

2011-03-21 11:32:24 1033

1033 DS31407是一個(gè)靈活的,高性能的不同頻率轉(zhuǎn)換時(shí)間和頻率合成中的應(yīng)用集成電路。就其三個(gè)輸入和四個(gè)輸出時(shí)鐘時(shí)鐘,每個(gè)設(shè)備可以接受幾乎任何關(guān)系或產(chǎn)生2kHz和750MHz的頻率。

2011-03-21 11:35:53 1159

1159 DS31408是一個(gè)靈活的,高性能的不同頻率轉(zhuǎn)換時(shí)間和頻率合成中的應(yīng)用集成電路。在其八個(gè)輸入時(shí)鐘和14個(gè)輸出時(shí)鐘,

2011-03-21 11:40:29 1712

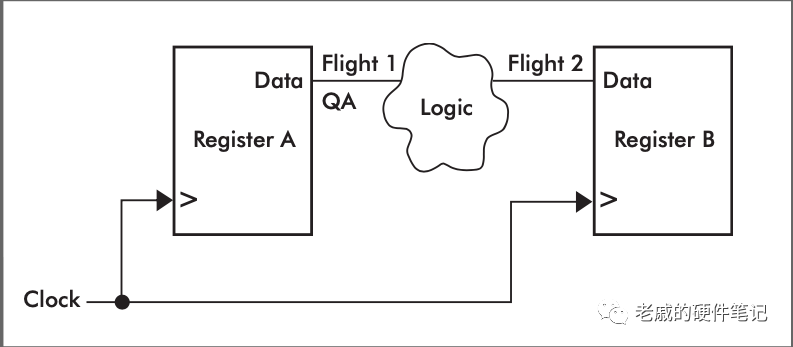

1712 信號在不同時(shí)鐘域之間的轉(zhuǎn)換是復(fù)雜數(shù)字電路設(shè)計(jì)中不可缺少的一部分,直接鎖存法和鎖存反饋法可處理控制信號的同步,異步FIFO在跨時(shí)鐘的數(shù)據(jù)交換方面具有高效的優(yōu)勢,本文設(shè)計(jì)的

2011-08-22 12:07:12 5851

5851

討論了物理設(shè)計(jì)中時(shí)鐘網(wǎng)絡(luò)的設(shè)計(jì)技術(shù),并以現(xiàn)有的CPU時(shí)鐘網(wǎng)絡(luò)的為例,介紹了高性能CPU的時(shí)鐘網(wǎng)絡(luò)設(shè)計(jì)技術(shù)。

2011-12-27 15:28:56 46

46 高性能的時(shí)鐘同步系統(tǒng)是任何通信傳輸領(lǐng)域必不可少的,并且在很大程度上決定了整個(gè)傳輸系統(tǒng)的性能,可稱之為傳輸系統(tǒng)的心臟 時(shí)鐘同步系統(tǒng)是基于鎖相環(huán)路的同步原理,跟蹤一個(gè)高

2011-12-28 16:39:39 41

41 提出一種高頻時(shí)鐘電路的設(shè)計(jì)方案。利用一款先進(jìn)的可編程時(shí)鐘合成器MPC92433,基于FPGA的控制,實(shí)現(xiàn)4對LVDS信號輸出。系統(tǒng)經(jīng)過測試,輸出時(shí)鐘信號頻率達(dá)到1 GHz,可以廣泛應(yīng)用到各種數(shù)

2012-08-08 11:29:46 24

24 世界上的各種電子設(shè)備,每一臺中都一定會有好幾個(gè)電子電路在工作。為了讓它們正常發(fā)揮功能,離不開間隔規(guī)律、穩(wěn)定的周期信號“時(shí)鐘信號”。電子電路以這個(gè)時(shí)鐘信號為基準(zhǔn)而進(jìn)行動作。時(shí)鐘信號既是讓各個(gè)電路完成其功能的時(shí)機(jī)提示信號,也是使電子設(shè)備與周邊的控制器等連動(同步)用的信號。

2016-04-12 13:47:11 5037

5037 我們知道,SERDES對參考時(shí)鐘有嚴(yán)格的相位噪聲性能要求。通常,SERDES供應(yīng)商會根據(jù)其SERDES采用的PLL以及CDR架構(gòu)特點(diǎn),以及性能數(shù)據(jù),提出對參考時(shí)鐘的相位噪聲的具體要求。

2017-02-10 18:40:10 5965

5965

現(xiàn)議價(jià)。不幸的是,相對較少信息已出現(xiàn)在晶體電路和工程師們常常把水晶電路視為一種黑色藝術(shù),最好留給幾個(gè)熟練的從業(yè)者(見盒子),關(guān)于石英水晶。 事實(shí)上,最高性能的晶體時(shí)鐘電路要求各種復(fù)雜的考慮和微妙實(shí)現(xiàn)技術(shù)。然而,

2017-05-05 11:38:25 14

14 時(shí)鐘設(shè)備設(shè)計(jì)使用I2C可編程小數(shù)鎖相環(huán)(PLL),可滿足高性能時(shí)序需求,這樣可以產(chǎn)生零PPM(百萬分之一)合成誤差的頻率。高性能時(shí)鐘IC具有多個(gè)時(shí)鐘輸出,用于驅(qū)動打印機(jī)、掃描儀和路由器等應(yīng)用系統(tǒng)的子系統(tǒng),例如處理器、FPGA、數(shù)據(jù)轉(zhuǎn)換器等。

2017-08-30 11:04:04 4285

4285

高性能CPU的時(shí)鐘網(wǎng)絡(luò)設(shè)計(jì)

2017-10-30 15:28:58 23

23 在本文中,筆者將談?wù)摱秳?b class="flag-6" style="color: red">合成器與清除器的不同系統(tǒng)參考信號(SYSREF)模式,以及如何用它們來最大限度地提高JESD204B時(shí)鐘方案的性能。 LMK04821系列器件為該話題提供了很好的范例研究素材

2017-11-17 10:31:45 3009

3009

設(shè)計(jì)中。 時(shí)鐘信號是任何數(shù)字電路設(shè)計(jì)的基礎(chǔ),而時(shí)鐘源是雷達(dá)、通信、測試儀器等電子系統(tǒng)實(shí)現(xiàn)高性能指標(biāo)的關(guān)鍵,很多電子設(shè)備和系統(tǒng)功能的實(shí)現(xiàn)都直接依賴于高性能的時(shí)鐘源。文中選擇時(shí)鐘合成器MPC92433+FPGA的方式設(shè)計(jì)高頻時(shí)鐘源,實(shí)現(xiàn)了4路LVDS (Low Voltage

2017-11-28 14:41:49 1

1 源。CDCE62005時(shí)鐘合成器芯片提供了一種現(xiàn)實(shí)的時(shí)鐘解決方案,以滿足對高速ADC的嚴(yán)格要求。該應(yīng)用報(bào)告突出了與時(shí)鐘源相關(guān)聯(lián)的限制性代理,其對ADC信號噪聲性能產(chǎn)生不利影響。

2018-05-16 14:26:14 24

24 TI最近推出了一套適合于高速、高IF采樣模數(shù)轉(zhuǎn)換器(ADC)的設(shè)備,如ADS583,它能夠采樣多達(dá)135個(gè)MSPS。為了實(shí)現(xiàn)這些高性能設(shè)備的全部潛力,系統(tǒng)必須提供極低的相位噪聲時(shí)鐘源。CDCE72010時(shí)鐘合成器芯片提供了現(xiàn)實(shí)的時(shí)鐘解決方案,以滿足對高速ADC的嚴(yán)格要求。

2018-05-28 09:09:47 11

11 首先,我們看一下時(shí)鐘信號中最常見到的波形 - 矩形波(尤其是方波更常用)。在較低時(shí)鐘頻率的系統(tǒng)中我們看到的基本上都是以矩形波為主的時(shí)鐘信號,因?yàn)?b class="flag-6" style="color: red">電路基本上都是靠時(shí)鐘的邊沿(上升沿或下降沿)進(jìn)行

2018-12-06 11:53:10 59988

59988

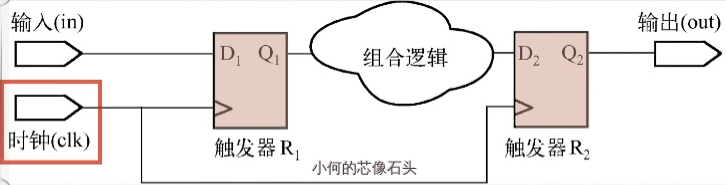

想象一下,如果頻率較高的時(shí)鐘域A中的信號D1 要傳到頻率較低的時(shí)鐘域B,但是D1只有一個(gè)時(shí)鐘脈沖寬度(1T),clkb 就有幾率采不到D1了,如圖1。

2019-02-04 15:52:00 10841

10841

ADI研討會:高性能時(shí)鐘: 解密抖動

2019-08-20 06:05:00 1656

1656 一個(gè)不尋常的電路,“tanktwanger”,提供了一些優(yōu)于傳統(tǒng)時(shí)鐘合成方法的時(shí)鐘產(chǎn)生和調(diào)整優(yōu)勢。您可以針對眾多應(yīng)用調(diào)整主電路,但在構(gòu)建此VHF設(shè)計(jì)時(shí)必須注意。

2019-08-08 10:51:20 2346

2346

美國馬薩諸塞州諾伍德市 - 全球領(lǐng)先的信號處理應(yīng)用高性能半導(dǎo)體公司ADI公司今天推出了一系列時(shí)鐘IC,可滿足當(dāng)今高性能電子應(yīng)用中最嚴(yán)格的信號處理要求,如作為無線基礎(chǔ)設(shè)施收發(fā)器,儀器儀表和寬帶基礎(chǔ)設(shè)施

2019-09-15 16:52:00 3289

3289

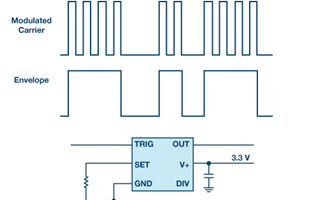

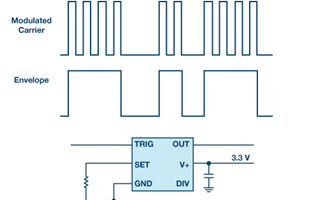

許多模擬電路需要一種時(shí)鐘信號,或者要求能在一定時(shí)間后執(zhí)行某項(xiàng)任務(wù)。對于這樣的應(yīng)用,有各種各樣適用的解決方案。

2019-11-19 14:39:36 2676

2676

時(shí)鐘設(shè)備設(shè)計(jì)使用I2C可編程小數(shù)鎖相環(huán)(PLL),可滿足高性能時(shí)序需求,這樣可以產(chǎn)生零PPM(百萬分之一)合成誤差的頻率。高性能時(shí)鐘IC具有多個(gè)時(shí)鐘輸出,用于驅(qū)動打印機(jī)、掃描儀和路由器等應(yīng)用系統(tǒng)

2020-11-03 10:40:00 0

0 時(shí)鐘篇 選用全局時(shí)鐘緩沖區(qū)(BUFG)作為時(shí)鐘輸入信號,BUFG是最穩(wěn)定的時(shí)鐘輸入源,可以避免誤差。 只用一個(gè)時(shí)鐘沿來寄存數(shù)據(jù),使用時(shí)鐘的兩個(gè)沿是不可靠的,如果時(shí)鐘沿“漂移”,就會導(dǎo)致時(shí)序錯(cuò)誤

2020-12-11 10:26:44 1482

1482 AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515時(shí)鐘分配IC的高性能ADC的低抖動采樣時(shí)鐘發(fā)生器

2021-04-30 09:48:42 13

13 貿(mào)澤電子即日起備貨Renesas Electronics FemtoClock2高性能時(shí)鐘頻率合成器。

2021-10-14 16:03:12 1331

1331

時(shí)鐘芯片是一種高性能、低功耗、帶RAM的實(shí)時(shí)時(shí)鐘電路,時(shí)鐘芯片可以對年、月、日、周日、時(shí)、分、秒運(yùn)行計(jì)時(shí),具有閏年補(bǔ)償功能,工作電壓為2.5V~5.5V。它使用三線接口與CPU運(yùn)行同步通信,并可使用突發(fā)方式一次傳送多個(gè)字節(jié)的時(shí)鐘信號或RAM數(shù)值。

2021-12-20 10:04:00 10463

10463 如果用單獨(dú)的時(shí)鐘信號板,一般采用什么樣的接口,來保證時(shí)鐘信號的傳輸受到的影響小?

2022-09-16 08:58:49 1918

1918

時(shí)鐘電路是一種電路,它可以產(chǎn)生定期的時(shí)鐘信號,用于控制電子設(shè)備的運(yùn)行。

它的特點(diǎn)是可以產(chǎn)生定期的時(shí)鐘信號,可以控制電子設(shè)備的運(yùn)行,可以提高電子設(shè)備的精度和可靠性。時(shí)鐘電路的應(yīng)用非常廣泛,它可

2023-02-20 18:16:38 5973

5973 。高性能時(shí)鐘芯片是電子設(shè)備不可或缺的重要元器件,在服務(wù)器、交換機(jī)、基站、醫(yī)療設(shè)備中廣泛應(yīng)用。但是,該領(lǐng)域此前一直為國外廠商所壟斷。極景微依托創(chuàng)始團(tuán)隊(duì)在超低抖動鎖相環(huán)技術(shù)及創(chuàng)新時(shí)鐘電路方案領(lǐng)域的深厚積累,成功

2021-11-22 09:47:49 1792

1792

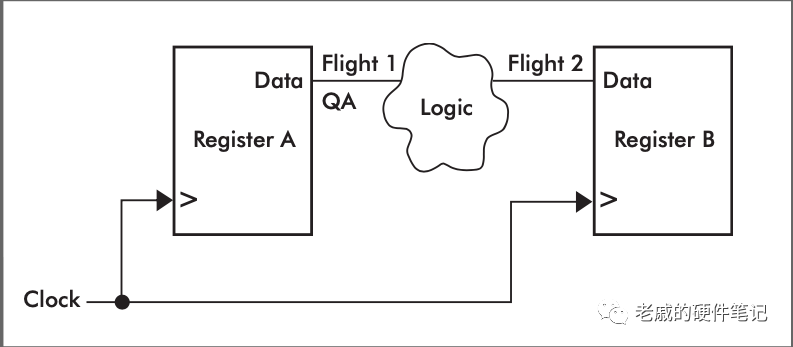

、保持(hold)時(shí)間的時(shí)序關(guān)系,電路的輸出(布爾值)就是可預(yù)測的,這是數(shù)字邏輯電路設(shè)計(jì)的基礎(chǔ)。如果 不能滿足建立保持時(shí)間 ,我們認(rèn)為輸入是 異步 (asynchronous) 信號 。一個(gè)時(shí)鐘域的同步信號輸出到另一個(gè)時(shí)鐘域通常被認(rèn)為是異步信號。

2023-06-23 17:53:00 898

898

即電路中的所有受時(shí)鐘控制的單元,全部由一個(gè)統(tǒng)一的全局時(shí)鐘控制

2023-06-27 09:54:21 377

377

時(shí)鐘電路用于產(chǎn)生穩(wěn)定的時(shí)鐘信號,常見于數(shù)字系統(tǒng)、微處理器、微控制器、通信設(shè)備等。時(shí)鐘信號用于同步各個(gè)電子元件的操作和數(shù)據(jù)傳輸,確保系統(tǒng)的正常運(yùn)行。

2023-08-03 14:46:04 1242

1242 單位寬(Single bit)信號即該信號的位寬為1,通常控制信號居多。對于此類信號,如需跨時(shí)鐘域可直接使用xpm_cdc_single,如下圖代碼所示。參數(shù)DEST_SYNC_FF決定了級聯(lián)觸發(fā)器

2023-08-16 09:53:23 462

462

業(yè)界高端FPGA的卓越性能和高口碑聲譽(yù)都有哪些因素了?其中很重要的一個(gè)因素就是FPGA內(nèi)部豐富的時(shí)鐘資源使得FPGA在處理復(fù)雜時(shí)鐘結(jié)構(gòu)和時(shí)序要求的設(shè)計(jì)中具有很大優(yōu)勢。設(shè)計(jì)師可以更好地控制和管理時(shí)鐘信號,提高時(shí)序性能、減少時(shí)鐘相關(guān)問題,并滿足設(shè)計(jì)的高性能和穩(wěn)定性要求。

2023-08-31 10:44:01 530

530 芯片為什么要時(shí)鐘信號 芯片是現(xiàn)代電子設(shè)備的核心組成部分,廣泛應(yīng)用于計(jì)算機(jī)、手機(jī)、電視等各個(gè)領(lǐng)域。芯片內(nèi)部有著復(fù)雜的電子元件和電路結(jié)構(gòu),這些元件和電路結(jié)構(gòu)需要進(jìn)行同步操作,以實(shí)現(xiàn)正確的工作。因此,芯片

2023-09-01 15:38:11 1376

1376 時(shí)鐘分頻電路通過將輸入的高頻時(shí)鐘信號分頻,生成較低頻率的時(shí)鐘信號。它通常基于計(jì)數(shù)器和邏輯門實(shí)現(xiàn),用于將高頻時(shí)鐘信號分解成系統(tǒng)所需的各種頻率。

2023-09-14 14:53:57 4894

4894 件、計(jì)算機(jī)、數(shù)字電路和通訊協(xié)議等設(shè)備的信號。它的主要作用是進(jìn)行時(shí)序控制,使數(shù)據(jù)傳輸和處理的時(shí)序保持一致。時(shí)鐘信號一般由計(jì)時(shí)器產(chǎn)生,其具有一定的周期性、穩(wěn)定性和精度。 時(shí)鐘信號的主要信號參數(shù)包括周期、頻率、精度和占空比等,

2023-09-15 16:28:12 1767

1767 芯片為什么需要時(shí)鐘信號? 在我們?nèi)粘I钪校覀兯褂玫母鞣N電子設(shè)備都需要一個(gè)時(shí)鐘信號來進(jìn)行計(jì)時(shí)和同步,例如:手機(jī)、電腦、電視、汽車、機(jī)器人、智能家居等設(shè)備都需要時(shí)鐘信號。對于各種這些電子設(shè)備

2023-09-15 16:28:14 1369

1369 的基礎(chǔ),因此,在電子學(xué)領(lǐng)域中,如何產(chǎn)生和控制時(shí)鐘信號是一項(xiàng)至關(guān)重要的技術(shù)。 時(shí)鐘信號是指一個(gè)周期性的方波信號,其周期性能和穩(wěn)定性非常重要。為了使時(shí)鐘信號精確可靠地產(chǎn)生,需要考慮多種因素的影響,包括設(shè)備的穩(wěn)定性、

2023-09-15 16:28:22 1496

1496 時(shí)鐘信號的同步 在數(shù)字電路里怎樣讓兩個(gè)不同步的時(shí)鐘信號同步? 在數(shù)字電路中,時(shí)鐘信號的同步是非常重要的問題。因?yàn)樵?b class="flag-6" style="color: red">信號處理過程中,如果不同步,就會出現(xiàn)信號的混淆和錯(cuò)誤。因此,在數(shù)字電路中需要采取一些

2023-10-18 15:23:48 771

771 什么是時(shí)鐘芯片?時(shí)鐘芯片的工作原理 時(shí)鐘芯片的作用 時(shí)鐘芯片是一種用于計(jì)算機(jī)或其他電子設(shè)備中的集成電路,它提供精準(zhǔn)的時(shí)鐘信號。時(shí)鐘信號是計(jì)算機(jī)進(jìn)行各種操作的基礎(chǔ),比如數(shù)據(jù)傳輸、運(yùn)算等等,所以時(shí)鐘芯片

2023-10-25 15:02:33 2314

2314 什么器件可以產(chǎn)生

時(shí)鐘信號?

時(shí)鐘信號是用來做什么用的?

時(shí)鐘信號起什么作用?

時(shí)鐘信號是一個(gè)精確的電

信號,它可以通過電子器件來產(chǎn)生,并且具有一定的頻率和周期。

時(shí)鐘信號在電子系統(tǒng)中具有非常重要的作用,因?yàn)?/div>

2023-10-25 15:07:45 637

637 什么是時(shí)鐘電路?什么是脈沖?時(shí)鐘電路是如何生成脈沖的? 時(shí)鐘電路是一種電路,它產(chǎn)生的周期性的信號被用作計(jì)算機(jī)系統(tǒng)的基準(zhǔn)。時(shí)鐘電路產(chǎn)生的信號被稱為時(shí)鐘脈沖或時(shí)鐘信號。在計(jì)算機(jī)系統(tǒng)中,時(shí)鐘信號用于同步

2023-10-25 15:14:17 795

795 時(shí)鐘合成器和時(shí)鐘發(fā)生器是兩種用于產(chǎn)生時(shí)鐘信號的電子器件,它們在功能和應(yīng)用上有一些區(qū)別。

2023-11-09 10:26:56 298

298 時(shí)鐘電路是指用于產(chǎn)生穩(wěn)定、精確的時(shí)間基準(zhǔn)信號的電路。這種電路通常采用晶體振蕩器或者其他穩(wěn)定的振蕩器作為時(shí)鐘源,產(chǎn)生固定頻率的信號。時(shí)鐘信號被廣泛應(yīng)用于數(shù)字系統(tǒng)、通信系統(tǒng)、計(jì)算機(jī)系統(tǒng)等各種電子設(shè)備中,用于同步和控制各種操作和數(shù)據(jù)傳輸。

2023-11-17 09:50:08 770

770 電子發(fā)燒友網(wǎng)站提供《時(shí)鐘和頻率合成的應(yīng)用領(lǐng)域.pdf》資料免費(fèi)下載

2023-11-27 10:41:13 2

2 高性能20路PCIe時(shí)鐘緩沖器新品推介SQ82100PCI-Express(PCIe)是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),主要用于擴(kuò)充計(jì)算機(jī)系統(tǒng)總線數(shù)據(jù)吞吐量以及提高設(shè)備通信速度。目前服務(wù)器

2023-12-20 08:19:38 240

240

什么是時(shí)鐘信號?數(shù)字電路的時(shí)鐘信號是怎么產(chǎn)生呢? 時(shí)鐘信號,也稱為時(shí)鐘脈沖,是用于同步數(shù)字電路中所有操作的基本信號。它提供了一個(gè)參考頻率,使得所有電路元件都能按照同樣的節(jié)奏進(jìn)行工作。時(shí)鐘信號

2024-01-25 15:40:52 909

909 芯片為什么要時(shí)鐘信號 時(shí)鐘芯片的作用是什么? 時(shí)鐘信號在芯片中起著非常重要的作用。它是芯片的“心臟”,相當(dāng)于人體的心臟,用于同步和控制芯片中的各個(gè)功能模塊之間的操作。時(shí)鐘信號可以提供一個(gè)穩(wěn)定的時(shí)間

2024-01-29 18:11:31 626

626 已全部加載完成

![]() 、NA、NB等分別與FPGA連接,接口模式為模式。

、NA、NB等分別與FPGA連接,接口模式為模式。 電子發(fā)燒友App

電子發(fā)燒友App

評論