當我們考慮出現EOS問題的放大器時,可能會想到靜電放電 (ESD) 。ESD使放大器引腳面臨短時、高壓、放電問題。第二種(通常會被人們忽略)過應力條件是 EOS 。EOS使放大器面臨相對于 ESD 較低的過壓和電流,但持續時間更長。看完本文后,您就會對潛在放大器 EOS 狀態有所了解,并知道解決這一問題的方法。利用這種方法,您就能夠設計防止電氣過應力損壞、穩健的集成電路外部系統。破壞性的靜電放電事件

電氣過應力的一個明顯起因是 ESD。當兩個物體 (body) 極為接近,且處于不同靜電位下(幾百伏或數千伏)時,便存在發生 ESD 的可能性。若兩個物體之間出現傳導路徑,則會發生靜電荷轉移。電荷中和以后,便不再放電。芯片處于電路斷開 (out-of-circuit) 環境下可能會發生 ESD 。一般而言,我們發現錯誤地操作 IC 芯片會導致 ESD發生,從而帶來一定的破壞性。ESD 發生在若干分之一秒時間內(通常不到 250ns)。若電流路徑中幾乎沒有電阻的話,則大約數安培的電流將會流入芯片電路。數十年前,半導體電路常常遭受 ESD 帶來的破壞,最終會導致整個電路故障,甚至帶來危害更大的參數降級。然而,一旦 ESD 的特性為人們了解之后,半導體廠商就開始在新的 IC 設計中實施保護電路。這些片上保護電路極大地降低了 ESD 對 IC 芯片產生破壞的可能性。片上 ESD 保護電路的主要功能是防止PCB 裝配之前和 PCB 裝配操作帶來的 ESD 相關破壞。此類操作期間,低阻抗接地路徑可起到放電路徑的作用,以對 IC 或周圍表面所帶的電荷進行放電。IC 安裝到 PC 電路板上后,情況便不一樣了。一旦安裝完成,在 IC 芯片和另一個板上組件之間便形成了連接。這就大大降低了低阻抗 ESD 路徑存在的可能性。完成此安裝以后,您極有可能不會碰到干預內部 ESD IC 電路的 ESD 情況。這的確不錯!但是,還有另一種可能性。工作電路的一些狀況可能會使 IC 芯片受 EOS的影響。在 EOS狀態下,可能會無意中激活 ESD 電路。EOS 的時滯可能會比 ESD 的時間要長得多。EOS期間電流傳導的強度和持續時間可能足以在芯片中產生具有危險水平的熱量。在這種極端條件下,芯片會被迅速破壞而且不可避免,最終損壞電路。幻像電氣過應力

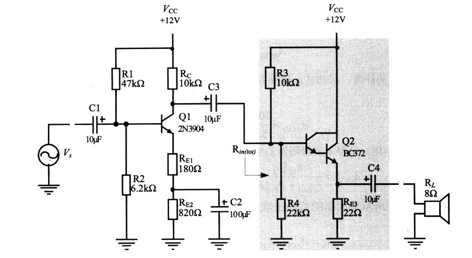

不知不覺地,我們可能正依賴器件的內部 ESD 電路在 EOS期間提供保護,盡管并非有意讓電路支持這一用途。您可能會發現,在施加電力以前您便擁有了一個可以完美運行的 IC(請參見圖 1),然而在施加電力和輸入信號以后該 IC 突然就被破壞了。EOS 可能會非常劇烈,以至于 IC 過熱,從而熔化裸片和封裝材料。圖 2 為此類破壞的一個例子。

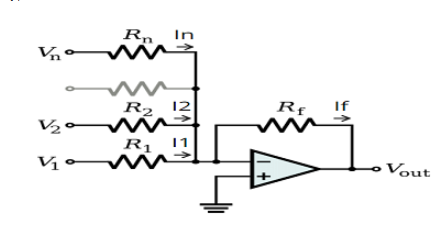

圖 1 安裝之前的全功能 IC

圖 2 出現EOS后被破壞的 IC集成電路通常不包括 EOS 條件保護。充其量,內部 ESD 保護電路可能會在 EOS 期間啟用,并提供充分保護。但是,設計 ESD 保護電路并不能保證在所有 EOS 狀態下都提供這種保護。EOS 期間建立的電流路徑較為復雜,并且有一定的不可預知性,雜散阻抗變大的高頻情況下更是如此。圖 3 顯示了放大器內幾種可能的電流路徑例子。ESD 輸入保護二極管(常為“關閉”)提供了到各個電源和 T1 的直流路徑。如果放大器電源不能吸入 EOS相關電流,則 IC 電源引腳電壓可能會上升至危險水平。T1 為一個 ESD 吸收器件。ESD 期間,T1 的功能是在安全水平開啟并鉗制電源引腳的電壓。切記大多數 ESD 事件都發生在 IC 處于電路斷開時。但是,在電路內 EOS 期間,T1 可能在不經意間開啟。此時,T1 會在運算放大器電源引腳之間建立起一個低電阻連接。這樣,強破壞性電流開始流動,直到 T1 熔化,從而在放大器電源之間形成短路。前面提到的自加熱和破壞均可能發生。上述熱量溫度可以升高到足以使封裝熔化、裂開,如圖 2 所示。

圖 3 EOS激活多條路徑圖中翻譯:

(左上黑字)電源阻抗可能會很復雜并且傳導路徑會根據電源的能力吸收或提供電流

(左上)目標信號(intended signal)

(左下)EOS 脈沖源(EOS pulse source)

(右上)T1 會發生傳導并在一個 ESD 事件中出現閉鎖(T1 may conduct and latch on during an ESD event)作為一個主要的設計考慮因素,需要確保經過器件的所有路徑均能夠安全地經受住 EOS 事件期間出現的電流和電壓。如果您無法預見這些條件,同時您的 IC 也不能散出產生的熱量,那么電路就可能會被損壞。了解放大器的內部 ESD 電路,并預測它們在 EOS 事件中的表現,是避免出現這些問題的一種有效方法。大多數運算放大器廠商均可提供 ESD 電路的相關信息。EOS 條件舉例

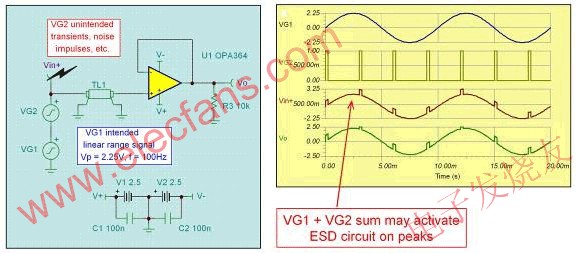

利用 TINA 軟件工具和 OPA364 宏模型生成的圖 4 是使用低功耗 OPA364 CMOS 運算放大器的簡單跟隨器電路的一個例子。低頻信號 VG1 表示來自變送器輸出端的信號。該變送器遠離放大器,有一條線纜 (TL1) 將它們連接起來。該電路中,周圍環境使得線纜上出現了瞬態。

圖 4 輸入過驅動可能會激活 ESD 保護電路圖中翻譯:

(左圖上)VG2無意瞬態、噪聲、沖擊等(VG2 unintended transients, noise impulses, etc.)

(左圖下)VG1 目標線性信號范圍VP=2.25.f=100Hz(VG1 intended linear range signal)

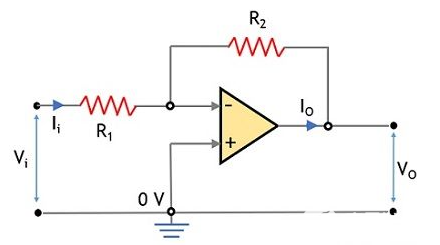

(右圖下)VG1+VG2 的和可以在峰值激活 ESD 電路(VG1+VG2 sum may activate ESD circuit on peaks)VG2 是與變送器輸出信號 (VG1) 結合在一起的計劃外瞬態信號。總信號振幅超出了放大器的最大規定輸入范圍。一個足夠強的瞬態信號將會觸發運算放大器輸入 ESD 電路。位于該放大器非反相輸入端前面的電阻限制了產生輸入電流的大小。ESD 單元設計旨在極短的時間內安全地傳導數安培電流,該傳導持續時間不超過幾十到數百納秒。當 ESD 單元在 EOS 事件期間激活時,電流傳導的時間取決于 EOS 脈沖或過壓特性。這些相同的 ESD 單元一般可持續處理五到十毫安的電流,當占空比下降時可持續處理的電流安培數會大大增加。在這些條件下,它們可能非常安全并且不受過壓的影響。在一些應用中,在電源電壓施加到放大器以前就出現了輸入信號(請參見圖 5)。該圖是使用 TINA 軟件工具和 OPA374 宏模型生成的。如果未將電流限制在一個安全值范圍內,則該上電行為就有可能會損壞輸入 ESD 保護電路。

圖 5 觀察上電過程中的 Vin!圖中翻譯:(右上)在電源斜坡下降時 Iin 過高(Iin excessively high while supply ramps)圖 5 中,電源 (VG2) 在 50ms 內從 0V 斜坡上升到 5V。電源開始斜坡上升 5ms 以后,施加一個 3.5V 的輸入信號 (VG1) 時便可完成上述過程。這種情況下,輸入開始為一個高于正電壓軌的電壓。這便開啟了非反相輸入 ESD 二極管。電流從非反相輸入端 (AM1) 流出,直到電源和輸入端之間的壓差低于約 0.6V 為止。若該輸入源為低阻抗并且可提供電流,則在電路中幾乎對其沒有限制。在這種條件下,一個可能產生破壞作用的電流會流經 ESD 二極管。安裝串聯輸入電阻可保護輸入電路免受此類損壞。在放大器轉換時間內,輸入 (VG1) 迅速達到 3.5V。另一方面,放大器轉換時輸出 (VM1) 達到輸入脈沖峰值。在放大器轉換時間內,該電路創建了一個較大的輸入-輸出壓差。最初,輸入端和輸出端之間的差值為 10V。同時,運算放大器內部電路和反饋元件必須在處理這一時間內流入放大器輸入端 (AM1) 的電流。當放大器輸入經受一個大信號也即快速邊緣脈沖(請參見圖 6)時,便出現另一種潛在破壞情況。該圖是使用 TINA 軟件工具和 OPA277 宏模型生成的。在這種情況下,VG1 的信號對輸入施加了一個 10V 的峰值矩形脈沖。放大器通過產生一個線性斜坡輸出電壓來響應該脈沖。放大器的有限轉換率(本例而言,OPA227 轉換率等于 2V/us)規定了輸出電壓的特性。

圖 6 輸入轉換期間輸入到輸入的應力圖中翻譯:(右上)輸入-輸出壓差(input-output voltage difference)在圖 6 所示的轉換時間內,在輸出達到輸入脈沖峰值要求的時間期間存在一個較大的輸入到輸出電壓差。一開始,放大器輸入端和輸出端之間的壓差為 10V。放大器轉換至其最終水平后該壓差隨之降低。由于反相輸入一開始便具有與輸出相同的電位,因此在兩個輸入端之間存在 10V 壓差。若運算放大器不包括內部輸入到輸入鉗位功能,則破壞性電壓電平可能會被施加到輸入晶體管的半導體結點上。這是雙極輸入運算放大器更為嚴重的一個問題。當前的現代雙極輸入運算放大器差不多都包括保護鉗位電路。一些運算放大器會呈現出輸出反向特性,其伴隨著輸入過驅動(請參見圖 7)。這種現象一般被稱為輸出相位反向。大多數現代運算放大器都不會出現這種現象,但也有一些運算放大器會出人意料地存在這一現象。對于那些具有這種特性的運算放大器來說,一般只有當施加的輸入電平超出產品規定的共模電壓 (CMV) 范圍時才會發生。當運算放大器出現輸出相位反向時,需采取預防措施來防止輸入被過驅動。

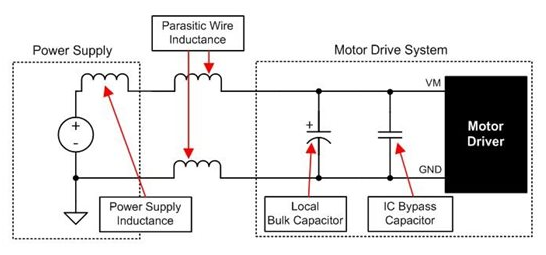

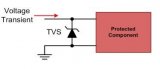

圖 7 輸入過驅動期間的輸出反向圖中翻譯:(右)輸出反向(output inversion)在圖7中,放大器輸入端 (VG1) 將被驅動至負電源軌以下約 0.5V。輸出電平立刻從負電壓軌轉為正電壓軌。由于輸入被進一步過驅動,因此輸出反向持續時間會更長。即使這可能不會損壞放大器,但其也是一種非理想的條件,如果它是屬于機電性質的(即馬達、傳動器等),則會給負載帶來破壞性的后果。通過在非反相輸入和負電源軌之間放置一個小信號、反偏壓連接的肖特基二極管就可解決這一過驅動問題。應將一個串聯輸入電阻包括在內,以限制流經該二極管的電流。開關電源輸出可能會包含高頻、瞬態能量。即使這些電源中包括了濾波,但輸出端上的電壓“峰值”仍可在放大器的電源引腳上產生瞬態過壓條件。如果電源電壓超出放大器的電壓擊穿極限,則 ESD 吸收器件可能會被觸發,從而在電源引腳之間形成一個傳導路徑。

圖 8 電源引腳過壓保護圖中翻譯:

(左)5V 電源電壓 1us 瞬態(1us transient riding on 5V supply voltage)

(右上)+5V 電源線 5V 1us 瞬態(5V 1us transient riding on+5V supply line)

(右下)無 TVS 模型時仿真中使用的齊納二極管(zener diode used in simulation on TVS model available)

A、RLC 電路的輸入電流限制(limits input current with RLC circuit)

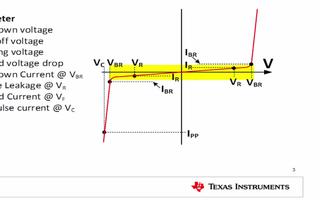

B、TVS 的輸入電壓限制(limits input voltage with TVS)利用 RC 或 RLC 電路,您可以保護器件免于電源瞬態(請參見圖 8)。使用一個普通的板上 EMI/RFI 濾波器便可完成這項工作。然而,電路的響應會隨 RLC 常數和負載特性的不同而呈現出極大的差異。在圖 8A 中,簡單的 RLC 電路被連接至一個負載電阻。+5V 電源具有 5V 的電壓,1us 瞬態,等于 10V 電壓峰值。這超出了一些低壓 CMOS 工藝的最大電源電壓。1kΩ 負載電阻模擬了一個需要約 5mA 電源電流的放大器。從響應可以看到 RLC 電路將該峰值融入到了一個 +5Vdc 電平上的正弦響應。輕微過壓不會導致器件出現問題。但是,在許多情況下,同 RLC 電路組合相關的一些未知條件會使電源電壓下沖。這會影響運算放大器的輸出偏移。雖然運算放大器的 PSRR 將有助于最小化輸出偏移的變化,但其也是一個明顯的誤差。由于太多的變量未知,因此最好不要依賴此類保護。一種更佳、可預知性更高的瞬態抑制方法是在電源線上使用瞬態電壓抑制器 (TVS)(請參見圖 8B)。TVS 與齊納二極管相類似,但它是專為承受超大瞬態電流和峰值功率而設計。在單極和雙極運算放大器中,TVR Littlefuse 1.5KE 系列均可用于 6.8V-550V 的反向承受電壓。10 次 100us 脈沖的峰值功率能力為 1500W。它們是一些具有納秒響應時間的快速響應器件。一個明顯的優勢是快速電壓鉗制特性,其電源電壓下沖極少(如果有的話)。圖 9 顯示了使用外部保護器件的完整 EOS 保護方案。如果您了解每一個運算放大器引腳上所用的內部 ESD 單元,則只要內部器件能夠完全保護各個運算放大器引腳就可以去除一些外部器件。

圖 9 完整的外部 EOS 保護圖中翻譯:

(標題)

實現完整的 EOS 保護所添加的外部組件(external components added to provide complete EOS protection)

(左上)

RF 和 RI 限制了流經 SDI2 和 SDI4 的電流(RF and RI limit current through SD12 and SD14)

(左中)

SDlx 為小信號肖特基二極管,并將輸入電壓限制在 (V. +0.3) 或 (V. -0.3) 二極管泄漏會影響輸入電流(SCOx are small signal schottky diodes and limit input voltage to(V. +0.3) 或 (V. -0.3). diode leakage affects the input current)

(右上)

SCOx 為小信號肖特基二極管。使用電源運算放大器的電源肖特基二極管。二極管將 EOS 電壓限制在 (V. +0.3) 或 (V. -0.3) (SCOx are small signal schottky diode. use power schottky diode for power OP amps. diode limit EOS voltage to(V. +0.3) or (V. -0.3))

(右中)

ROL 限制了流經 SDO5 和 SDO6 的電流。ROL 位于在 Vcut 時帶來極小影響的反饋中。(ROL limits current through SDO5,SDO6. ROL is inside the feedback adding little error at Vcut.) (中下)

ZSx 為齊納二極管或無極性半導體瞬態電壓抑制器 (TVS)。ZSx 防止了電源過壓、反極性并在一個電源電壓縮放時為 lq 提供一條路徑.(ZSx are zener diode or input semiconductor transient voltage suppressors (TVS). ZSx prevent power supply overvoltage. Reverse polarity, and provide a path for lq if one supply is floating.)SDIx 肖特基二極管提供了輸入過壓的電壓鉗制功能。R1 將流經這些二極管的電流限定在所用二極管的規定電平。SDOx肖特基二極管提供了輸出過壓的電壓鉗制保護。如果您在運算放大器電源上使用這種輸出保護,則需使用功率肖特基二極管。流經這些二極管的電流必須限定在所用二極管的規定電平。一旦您讓這種瞬態電流流經輸入或輸出二極管,則必須將這種能量接地,否則運算放大器電源可能會進入過壓狀態。如果出現這種情況,那么放大器就會鎖閉,甚至會被永久損壞。若電源不能吸入電流,或者非二極管直流電流頻率的低阻抗,則在每一個電源上都需要有一個齊納二極管或直流電壓抑制器 (TVS) 來引導該接地電流。大多數電源均為單向而非雙向流出電流或吸入電流。齊納二極管或單向半導體瞬態電壓抑制器提供了一種將器件引腳維持在安全水平的簡單、低成本方法。結論

一個 EOS 事件可能會激活運算放大器中的 ESD 保護電路。您也許會更傾向于認為 ESD 電路也同樣適合處理 EOS 事件。ESD 事件持續時間非常短,通常不到幾百納秒。相反,EOS 事件持續時間可能會更長。當 ESD 電路被 EOS 事件激活時,電路傳導電流可能會導致過熱,進而可能帶來一定的損壞。如果碰到您的系統面臨 EOS 事件時,需使用簡單的外部保護電路來保護您的電路。盡管存在一些較小的前端設計問題,但這可以讓您避免一些后端設計難題。

電子發燒友App

電子發燒友App

評論