集成電路可靠性——新興的競爭因素

可靠性驗證正獲得越來越多的關注。器件和導體愈加小巧,器件氧化層越來越薄,電源域的數量快速增長。數字內容的顯著增加正滲透到汽車、醫療和通信領域對可靠性要求較高的應用中。

集成電路可靠性的技術和市場推動因素

最早的可靠性檢查是對集成電路版圖進行目測,確定哪些結構可能出問題,然后進行調整。這種方法不再奏效。設計工作量大,而且非常復雜,人工檢查方法太不可靠。競爭環境要求設計人員根據仿真和經驗,采用技術節點留出明顯的余量,優化性能、占用空間和可靠性。

相比預防外部因素(例如靜電放電)引起的重大故障,設計人員現在必須處理好更不易察覺的設備退化。與快速明顯的硬故障不同,這些可靠性故障隨著時間的推移而逐漸顯現出來,通常難以預測。一旦某件產品被認為并不可靠,便可能很難改變市場對它的看法。

行業內目前正在更仔細地研究集成電路可靠性問題,以確定需要注意的方面并事先了解其對設計余量的影響。美國靜電放電協會 (ESD Association) 撰寫了一份關于靜電放電檢查的技術報告[1],旨在幫助行業做好更充分的準備來處理設計過程中常見的靜電放電問題。Reliability Simulation Council 也在研究其它方法來提高集成電路設計的可靠性。

更換代工廠或改用不同的工藝節點可能有損專門方法的效率。在這些關鍵時候,一套嚴格完善的最佳操作方法對于維持生產力和推動力至關重要。

集成電路可靠性檢查

重要的可靠性設計 (DFR) 問題包括:

時間相關介質擊穿 (TDDB)

負偏壓溫度不穩定性 (NBTI)

熱載流子注入 (HCI)

閾值電壓偏移 (Vt)

電遷移 (EM)

電過應力 (EOS)

閂鎖效應(Latch-up)

本文并不逐一詳細解釋這些機制。我們將討論一種普遍的集成電路設計可靠性檢查方法,并舉例說明這種方法如何應用于 TDDB 和 NBTI。這種檢查方法靈活,自動,還能以類似的方式進行其它檢查。

傳統方法

添加識別層

對于傳統設計規則檢查 (DRC) 工具,設計人員必須通過在版圖上添加識別層,確定需要進行可靠性檢查的實際位置。識別層用以確定需要通過具體檢查來確認適當的 DFR 方法的實際區域,而不是將要實現的實際功能。

添加識別層是一個單調乏味且容易出錯的手動過程。識別層也增加了 DRC 工作量(延長了整體周期時間),并且難以維護。由于存在這些缺點,識別層無法充分確保設計具備當今競爭市場所需的可靠性。

SPICE 仿真

一些可靠性檢查需要了解電路中每個節點的電壓。傳統方法采用 SPICE 仿真,提供每個節點的電壓和電流,因為電路由一系列支持對所有預期的工作模式進行仿真的向量推動。但是,SPICE 仿真特別耗時,需要大量的時間和洞察力來恰當地解釋和評估產生的波形。為了確保充足的覆蓋面,測試向量通常由自動覆蓋工具產生。由于產生了眾多向量,因此在依賴人工評估技術時很容易漏掉某個問題。

可升級的解決方案的特色

設計人員需要一個強大的可升級自動化物理驗證 (PV) 解決方案,幫助各個經驗水平的設計人員在設計中整合可靠性檢查的最佳做法。

一款可升級的可靠性驗證解決方案必須能夠:

體現物理系統的特色,并按照一套定義明確的最佳方法或規則進行驗證,

盡量避免完整模擬,以節省時間和計算資源,

讓具有專長的工程師能夠按照專業的可靠性設計方法來驗證設計。

為了完成這些任務,可升級的可靠性驗證工具需要一些對于物理驗證過程來說新出現的關鍵功能:

通過網表的規則支持拓撲識別,確定需要檢查的物理結構,

支持傳遞/連接的規則,從而在需要檢查的結構之間建立特定關系,

能夠評估應用于前兩個工藝結果的物理規則,

能夠與常用的物理驗證流程相整合,簡化信息交流過程。

橋接觀點

可靠性檢查的關鍵難題在于架起設計過程中邏輯觀點與物理觀點之間差異的橋梁。邏輯和模擬設計人員通常考慮原理圖和 Verilog 描述。而物理(班圖)設計人員則考慮幾何結構、寬度、長度、特征間隔等等。他們使用的工具也會相應變化。可靠性檢查需要結合這些觀念,因此給這些工具和使用工具的工程師都帶來了挑戰。

對于許多可靠性檢查而言,問題在于確定班圖中的哪些地方需要檢查。因為沒有方法來縮小范圍,大多數設計會產生大量誤報。像識別層這樣只以物理觀點操作的解決方案很有限。更好的解決方案應該可以讓設計人員現在網表里指定需要檢查的區域,然后在版圖中相應的區域進行必要的物理測量。

除了拓撲識別之外,設計人員還需要在整個設計過程中追蹤邏輯和物理關系。例如,要檢測因不正確的電壓域交叉導致違反柵擊穿電壓限制的情況,設計人員必須能夠在靜態模式下向設計中的所有節點傳遞供應電壓(以避免耗時的模擬)。之后,設計人員可以使用拓撲識別來消除原本擁有多個電源域連接的結構(例如電平轉換電路),消除誤報并且得到快速高效的結果。

實例:TDDB 檢查演示

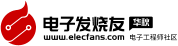

這種 TDDB 檢查采用的是 Calibre? PERC? 可靠性驗證工具。圖1顯示的是電路包含 PMOS 和 NMOS 薄柵氧化層,它們通過直接和非直接連接為電源域 VDD2 和 VSS2 提供電源。非直接連接可能會貫穿另一個晶體管、二極管、電阻器或其它電路元件,成為設計審核階段不易察覺的“缺失”路徑,特別是當非直接路徑貫穿的是設計層級不明顯的情況下的其它地方的電路。子電路 (VDD/VSS) 本身的局部電源連接可以在更大規模的設計中看到。還必須對在其它方面已經得到驗證的 IP 模塊的外部連接進行評估。

圖1:采用 Calibre PERC 的 TDDB 檢查法:檢查的是通過直接和非直接路徑到 VDD2/VSS2 的薄柵氧器件。

為確定不安全的薄柵氧器件,設計人員對這個檢查方法進行了定義(下面顯示的是偽代碼):

定義設計中的電源域。

定義哪些電源域對薄柵氧器件是“不安全”的。

定義薄柵氧MOS器件的類型和襯底類型。檢查這些薄柵氧MOS器件中“source”、“drain”、“bulk”到電源域的連接性。

a. 評估直接和非直接路徑。

b. 把那些連接到“不安全”電源域的薄柵氧MOS標識為錯誤。

復雜的系統通常存在多個電源域,這就需要通過復雜的設計規則來確定哪些電源域是安全的,以及什么條件下才是安全的。

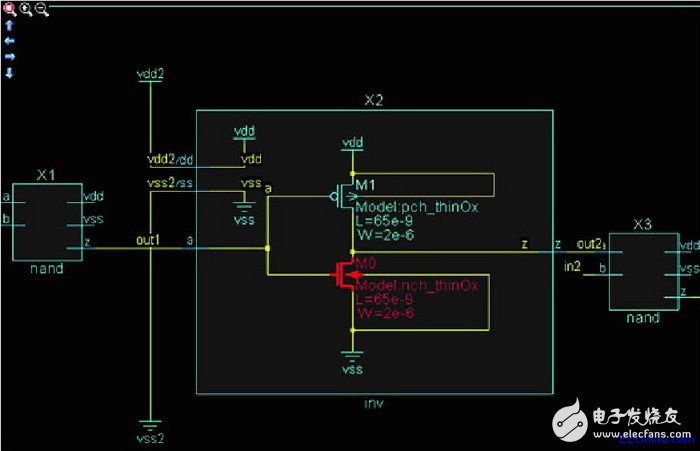

驗證MOS器件的bulk端的連接性對判斷一個電路是否容易受到與電源域相關的可靠性問題的影響非常重要。圖2顯示的是,一個不當的bulk 端的連接是如何因為bulk電壓的上升而讓 PMOS 柵易受到 NBTI 的影響的。

圖2:采用 Calibre PERC 的 TDDB 檢查法:一個具有高壓路徑的薄柵氧 PMOS(型號:pmos_lv)可能會導致 NTBI 。

與現有的可靠性技術相比, Calibre PERC 這樣的自動化可靠性驗證工具可以保證現在的設計不僅能夠被生產出來,而且性能在其整個生命周期中一直很穩定(表1)。

有了存檔、維護和改進可靠性驗證方法的集中式自上而下的方法(一般由某個 CAD 或 QA 部門掌握)后,這個部門應當(通過一個公共設計規則平臺)在工具中采用新的可靠性檢查,并向集成電路設計和驗證人員推廣配置好的工具。

自下而上的方法通常最初由小的設計小組開始采用這些新工具并結合自身的檢查規則來提高他們驗證任務的效率和有效性。在他們的成果發布后,會有更多的人需要這項新技術。在某個時間點,CAD 部門會加入進來提供支持,以減輕本地支持負擔,并為所有用戶提供統一的經驗。

結論

集成電路的可靠性驗證工作并非易事,但它正迅速變成一項至為關鍵的能力,能否創建出能夠提供長期可靠性的成功集成電路產品便在此一舉。為了做好這件事,您必須對這項工作給予明確的關注,并采用你認為最有效的工具。