摘 要:軍事電子裝備和民用通信系統復雜度日益提升, 射頻(RADIO FREQUENCy,RF) 集成技術正從傳統的混合集成技術或多芯片組件技術向芯片化的系統級封裝技術(SySTEM IN PACKAGING,SIP) 快速發展。對射頻系統級封裝(RF?SIP) 中的高性能互連技術需求進行了分析, 依據先進封裝互連技術的發展趨勢, 總結了芯片倒裝集成、 芯片埋置與扇出以及三維堆疊等技術在面向 RF?SIP 應用的最新研究進展, 最后提出了射頻系統級封裝互連技術的主要挑戰和發展方向。

0 引言

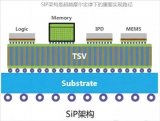

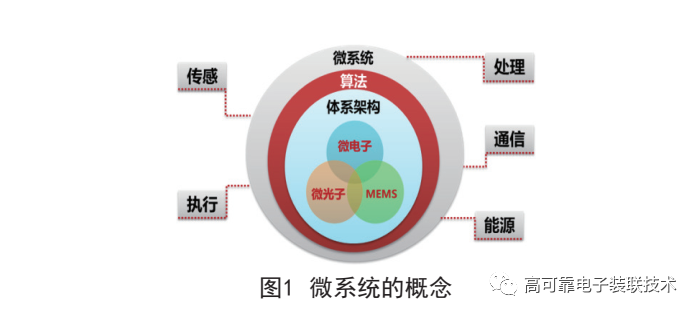

現代軍事電子裝備的發展對射頻系統提出了微型化、多功能、可重構的需求[1] ,射頻系統功能復雜度日益提升。有源相控陣(ACTIVE ELECTRONICALLy SCANNED ARRAy,AESA) 技術要求射頻系統實現高性能、可擴展、 低成本以及低剖面等特性,當前射頻系統集成架構從多芯片組件(MULTI?CHIP MODULE,MCM) 向系統級封裝(SySTEM IN PACKAGING, SIP) 方向發展[2?3]。在SIP的集成架構下,通過異構集成技術將多個不同功能的有源、 無源器件高密度地集成在單一封裝內, 形成具有系統或子系統功能的單元。射頻系統級封裝(RF?SIP) 通常采用 BGA、LGA 等標準的器件封裝形式, 以便進一步地通過表面貼裝技術(SURFACEMOUNTED TECHNOLOGy, SMT) 在系統母板上集成, 形成更為復雜和完整的電子系統[4] 。

相比 MCM 集成, 采用 RF?SIP 集成架構的射頻系統主要優勢如下:

1)在后摩爾時代的技術趨勢下, 射頻系統可持續吸收異構集成(HETEROGENEOUS INTEGRATION) / 系統級封裝的最新技術, 實現更復雜、 更高性能的系統集成;

2)RF?SIP 采用標準的封裝形式, 產品結構、 工藝方法具有較強的規范性和通用性, 因此新產品導入周期短,可快速進入批量生產, 制造成本低;

3)利用高低頻復合母板, 通過 SMT 工藝實現RF?SIP 與電源、 數字處理及天線等功能單元之間的板級系統集成,消除體積龐大的射頻/ 低頻電纜, 大幅提升系統集成密度及可靠性。 基于以上顯著優勢, RF?SIP 在國內外得到了廣泛的研究與應用。民用移動通信設備的射頻前端模塊主要采用 SIP 技術實現, 支撐SUB?6GHz 到毫米波, 甚至亞太赫茲頻段的應用[5?6] 。在軍事電子裝備領域, 面向輕薄化低剖面天線陣面的發展需求,采用 RF?SIP 集成技術實現收發組件(TRANS?MITTER AND RECEIVER, T / R) “芯片化” 是一個重要的技術趨勢[7] ,尤其在陣元間距僅幾個毫米的毫米波頻段更是如此[8] 。 互連技術是 SIP 的核心使能技術。相對于傳統的引線鍵合技術, 處于研究和應用前沿的先進封裝互連技術包括芯片倒裝(FLIP CHIP) 、 芯片埋置與扇出(CHIP EMBEDDED AND FAN?OUT) 以及三維堆疊(3DSTACKING) 等。射頻電路系統通常包含多樣化的元器件和零部件,如化合物半導體、 硅基射頻芯片、集成 無 源 器 件 (INTEGRATED PASSIVE DEVICES,IPD) 、MEMS 等, 這些器件采用了不同的材料和工藝, 互連和封裝要求差異大, 因此 RF?SIP 具有非常鮮明的異構集成特征, 并傾向于綜合采用多種先進互連技術。

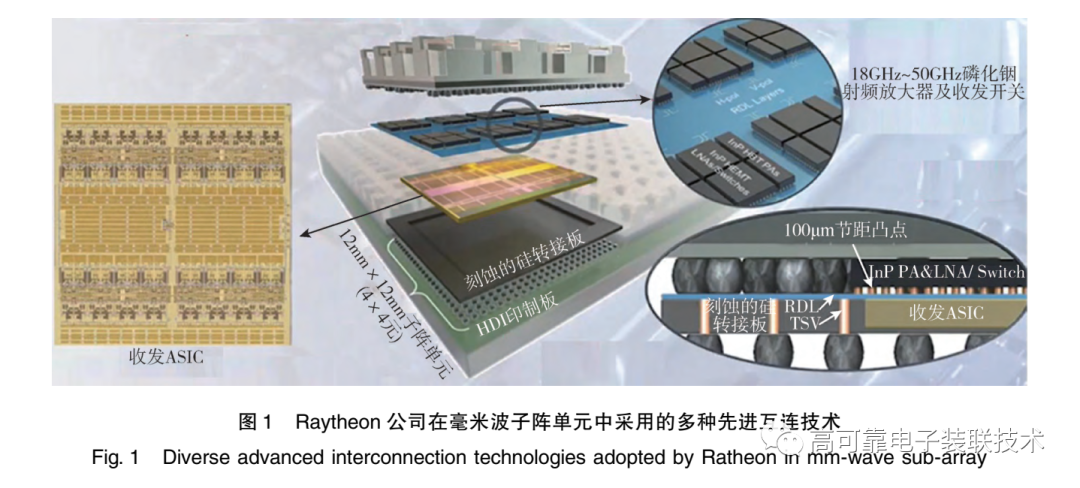

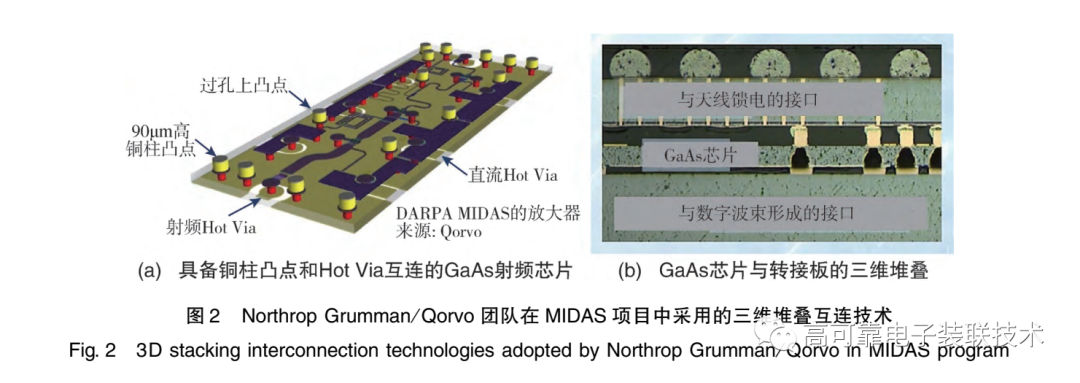

以美國國防高級研究計劃局(DARPA) 主導的毫米波數字陣列項目(MIDAS) 為例, RAyTHEON 公司的 4 × 4 子陣單元中, 綜合利用了硅基轉接板、有機高 密 度 基 板、 再 布 線 層 ( REDISTRIBUTE LAyER,RDL) 、 微凸點倒裝等技術, 將硅基 ASIC 多功能芯片、 磷化銦(INP) 低噪放/ 功放以及低剖面寬帶陣列天線進行堆疊集成, 展示了一種 18GHz ~ 50GHz 超寬帶應用的低剖面三維異構集成架構[9] , 如圖1所示。該項目的另一研究團隊(NORTHROP GRUMMAN / QOR?VO) 采用銅柱凸點、 熱過孔(HOT?VIA) 等互連結構, 通過多金屬與多溫度的鍵合技術將硅轉接板、砷化鎵 (GAAS) 射頻芯片、 鍺硅(SIGE) 有源轉接板、 CMOS 芯片實現可靠的垂直堆疊互連, 如圖 2所示[10] 。

由于分布參數的作用, RF?SIP 集成方案的選擇對射頻信號的傳輸、 增益、 噪聲、 功率以及隔離等系統指標有著直接的影響。先進封裝互連技術應用于RF?SIP 時將面臨射頻電路性能相關的挑戰, 本文重點綜述了 RF?SIP 中的芯片倒裝、 芯片埋置與扇出、 三維堆疊三類先進封裝互連技術的研究進展。

1 芯片倒裝技術

傳統的射頻封裝或模塊通常采用引線鍵合技術,但由于基板上的鍵合焊盤必須布置在芯片的外圍, 加之鍵合引線必須存在一定的高度, 因此互連結構大, 封裝內空間利用率低, 集成密度難以進一步提升。芯片倒裝技術通過互連材料將芯片有源面與基板焊盤進行組裝,相對引線鍵合,射頻芯片倒裝的主要技術優勢如下:

1)互連距離短、 分布參數小、 一致性好, 尤其在毫米波頻段互連性能優異;

2)利用芯片底部面積以面陣的方式與基板在垂直方向互連, 互連結構幾乎不占用額外的封裝空間, 集成密度高;

3)有效降低封裝高度, 有利于封裝的三維堆疊集成, 構建復雜功能的 RF?SIP。

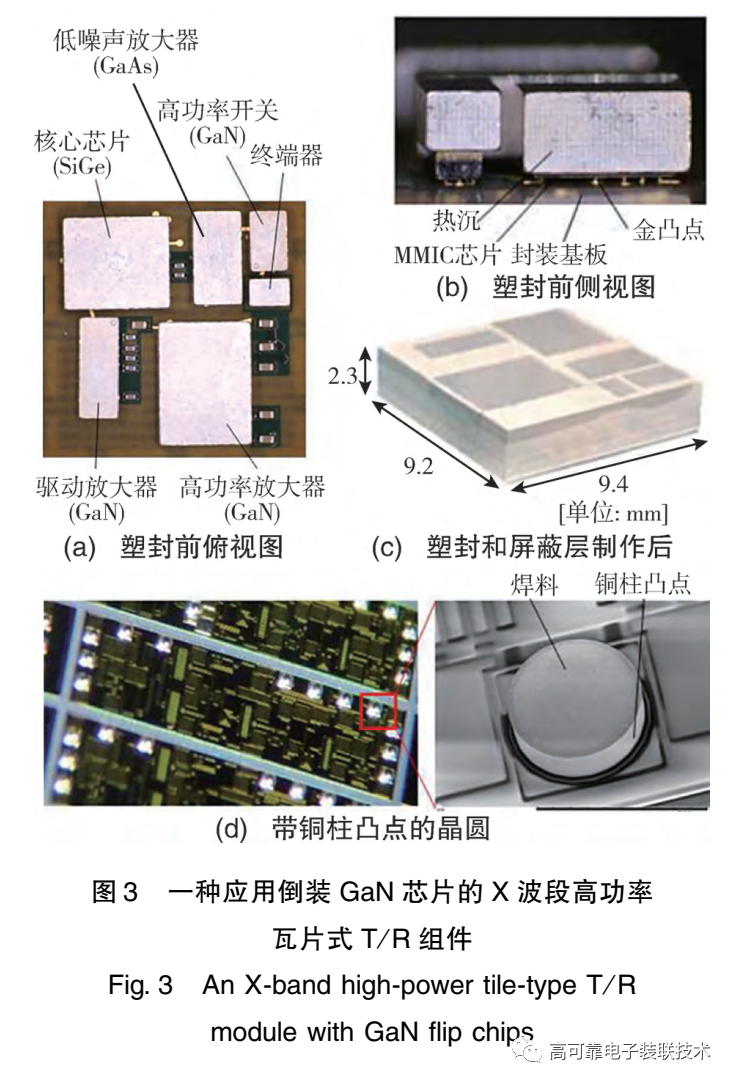

射頻芯片倒裝技術的研究在 20 世紀90 年代就已開始[11?12] , 但由于射頻芯片的 I / O 數量少, 單個I / O 的互連成本相對引線鍵合優勢并不明顯, 再加上化合物半導體射頻芯片因環保和工藝的差異,在利用硅芯片成熟的微凸點產業鏈能力上存在障礙, 導致了射頻芯片倒裝技術的應用速度遠慢于數字芯片。但隨著技術的成熟和產業規模的擴大,化合物半導體FOUNDRy 公司發布了倒裝芯片工藝設計套件(PROCESS DESIGN KITS, PDK) , GAAS 和硅基射頻芯片的倒裝技術已得到大量的應用。在 GAN 芯片方面的技術也即將走向量產應用, 如 QORVO公司獲得美國國防部 “ COPPER?PILLAR?ON?GAN” 的項目合同, 目標在 2022 年將 GAN 銅柱倒裝芯片技術從小批量的原型工藝推進至高產量、 高可靠的 9 級制造成熟度。 面向低剖面雷達孔徑的應用, 日本三菱電機[13] 報道了一種 X 波段高功率 T / R 組件, 其中的SIGE 核心芯片、GAAS 低噪放以及 GAN 功放/ 開關芯片全部采用銅柱凸點倒裝集成在有機基板上,然后進行塑封、 屏蔽層制作等工藝, 在尺寸僅9。 2MM × 9。 2MM × 2。 3MM 的 SIP 封裝中實現了 20W的發射功率, 如圖 3所示。在商業

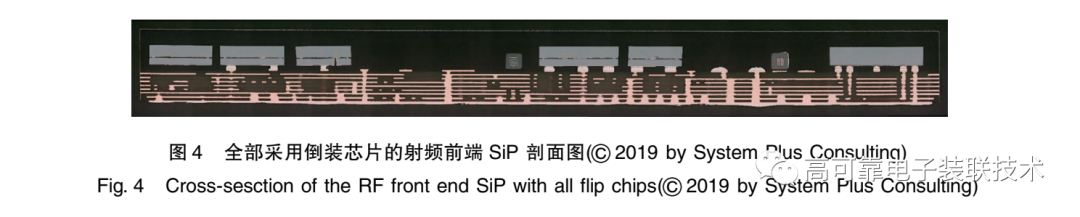

無線通信應用的射頻前端 SIP 中, 近年來倒裝射頻芯片已經成為主流, 如 BROADCOM 公 司 2019 年 量 產 的 射 頻 前 端AFEM8092, 封裝的 29 顆 MMIC 全部基于倒裝技術集成, 封裝中芯片面積占比高達 40% , 而且由于消除了芯片粘結、 引線鍵合等工序, 制造流程簡化,整體成本下降, 如圖 4 所示。

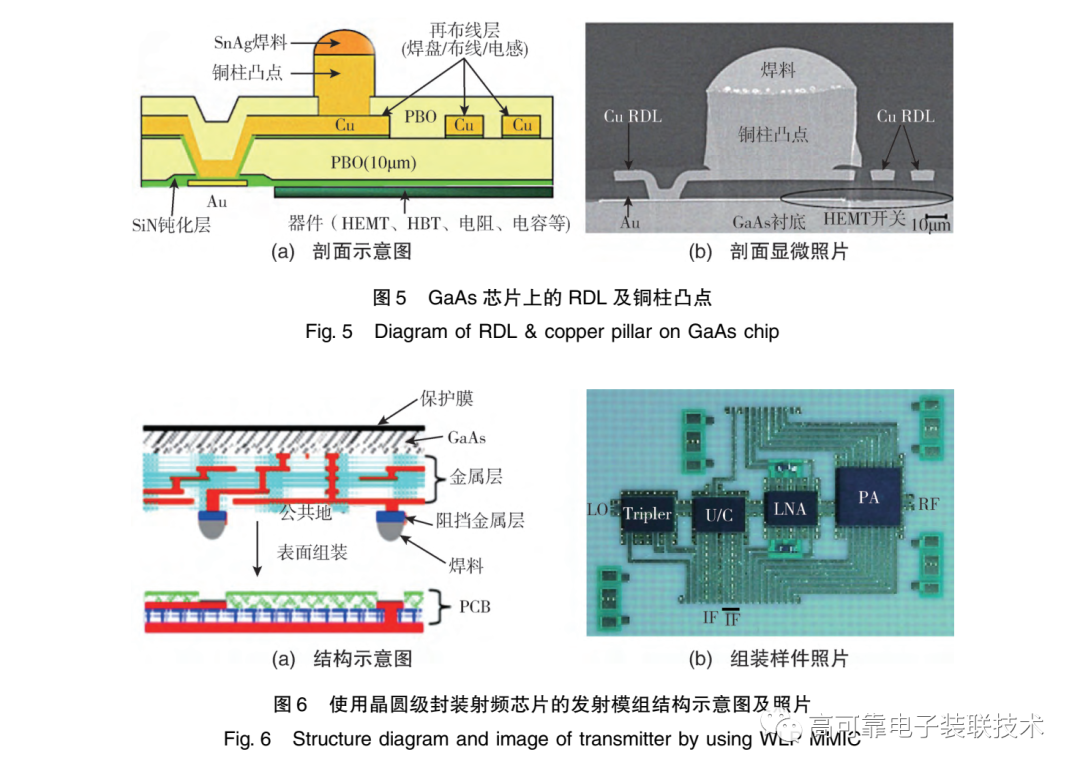

RF?SIP 中的芯片倒裝技術主要包括芯片?封裝協同設計、 射頻芯片凸點制備、 射頻高密度基板、倒裝集成裝配、可靠性技術等要素。在 RF?SIP 中應用芯片倒裝技術, 需重點在芯片?封裝協同設計和射頻芯片凸點制備兩個維度作特殊的考慮。 與數字電路不同, 射頻芯片表面設計有大量的傳輸線、電感等無源元件, 其傳輸阻抗、 Q 值等參數易受凸點焊接后的高度、 使用的底部填充和基板材料的影響, 因此射頻倒裝芯片通常需要與封裝進行協同設計[14] 。考慮到裝配工藝的精度遠低于晶圓工藝, 為降低封裝對芯片性能的影響,一種思路是在芯片中采用共面波導傳輸線(CPW) ,將傳輸線電場約束在 CPW 的縫隙附近, 并在此基礎上進一步優化芯片到基板之間的距離[14?15] ;另一種思路是采用晶圓級封裝(WAFER LEVEL PACKAGING,WLP) 在芯片表面增加低介電常數的厚介質和再布線層(REDISTRIBUTIONLAyER, RDL) [16] , 甚至設置接地層形成 “反轉傳輸線” 結構[17?18] , 屏蔽安裝基板對芯片性能的影響, 如圖 5 和圖6 所示。

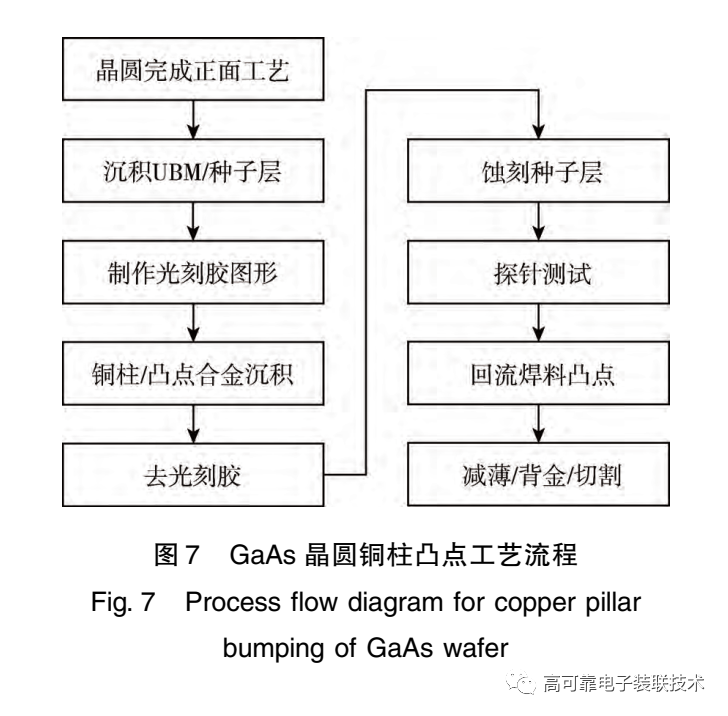

中國電科29所[19] 總結和對比了射頻芯片中焊料球凸點、銅柱凸點以及金球凸點這三種主流的凸點制備技術和應用特點。其中,金球凸點與化合物半導體芯片的金屬化體系(AU) 兼容,無須制作UBM層,具有較好的靈活性。帶焊料帽的銅柱凸點制備工藝顯然更為復雜,但可獲得更小的互連節距(≤100μM) ,是倒裝芯片技術應用的關鍵技術之一。為解決凸點電鍍和晶圓減薄過程中的破片問題,需要重新設計晶圓的后道工藝流程,并優化晶圓減薄所采用的臨時鍵合工藝。圖7給出了一種可行的GAAS晶圓銅柱凸點工藝流程[20] 。

2 芯片埋置與扇出技術

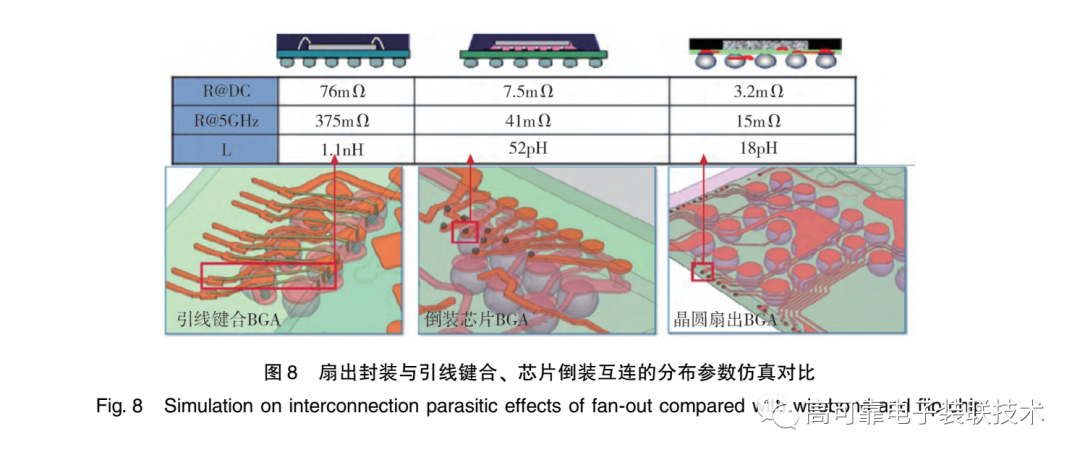

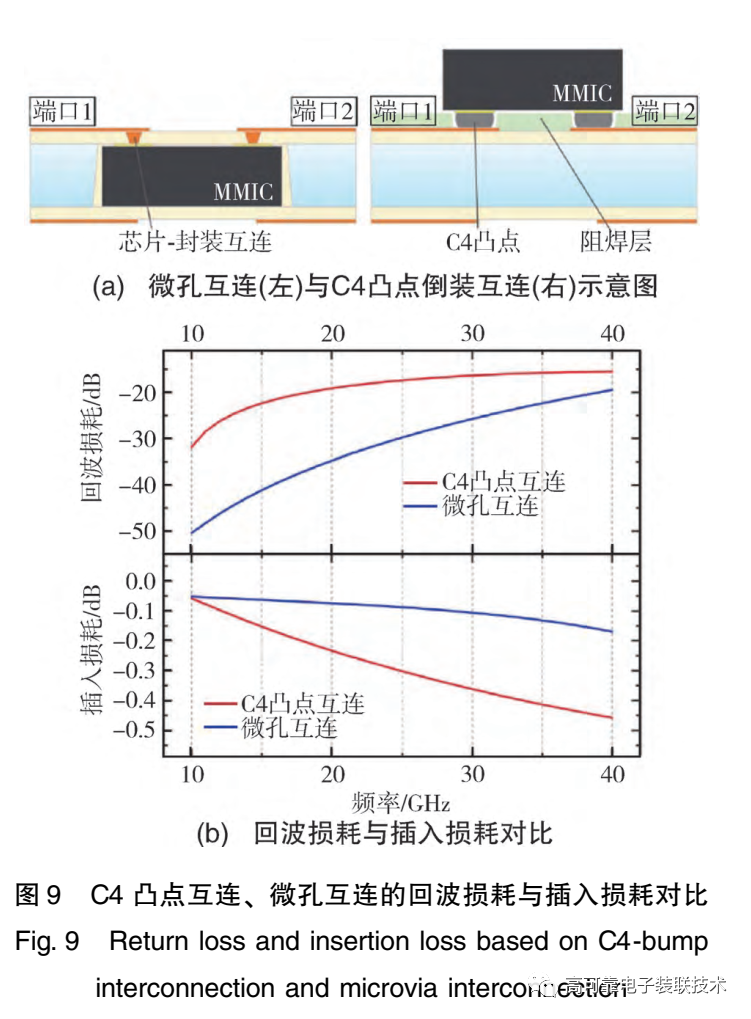

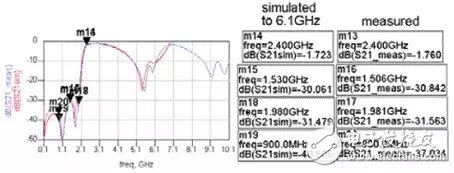

芯片埋置與扇出技術指基于晶圓級或面板級工藝,將器件埋置于塑封料或者基板之中, 然后通過 RDL 扇出器件的 I / O 端口并形成封裝[21] 。當埋置多顆不同種類的器件時, 即可形成 SIP[22?23] 。扇出技術通過微孔和 RDL 實現芯片?封裝的互連,由于互連距離短,分布參數(RLC) 小[24] ,毫米波頻段互連性能優勢明顯[25?26] 。如圖 8 和圖 9 所示, 分布參數、 插入損耗相比倒裝互連下降至少 50% ,更遠優于引線鍵合。因此, 芯片埋置與扇出互連技術能很好地適應微波/毫米波的應用需求。

自 INFINEON 公司 2009年將基于塑封重構晶圓工藝路線的 EWLB (EMBEDDED WAFER?LEVEL BALL GRIDARRAy) 投入量產以來,埋置與扇出工藝作為一種先進封裝技術得到了迅速的發展, 并衍生出眾多的技術變體。除了已得到較充分研究和成熟應用的“芯片先裝/面朝下(CHIP FIRST / FACE DOWN) ”、 “芯片先裝/ 面朝上(CHIP FIRST / FACE UP) ”、 “芯片后裝/ 面朝下(CHIPLAST / FACE DOWN) ” 這三種基于塑封工藝的技術形態[27] 外, 最近還發展了基于硅、 玻璃、金屬以及陶瓷等材料作為埋置材料的扇出系統級封裝。華天科技[28] 展示了在硅晶圓上通過 BOSCH 工藝刻蝕高精度盲腔并采用光敏干膜壓膜技術埋置了毫米波芯片的封裝案例,該方案得益于硅晶圓的高導熱性, 因此散熱性能優良[29] 。

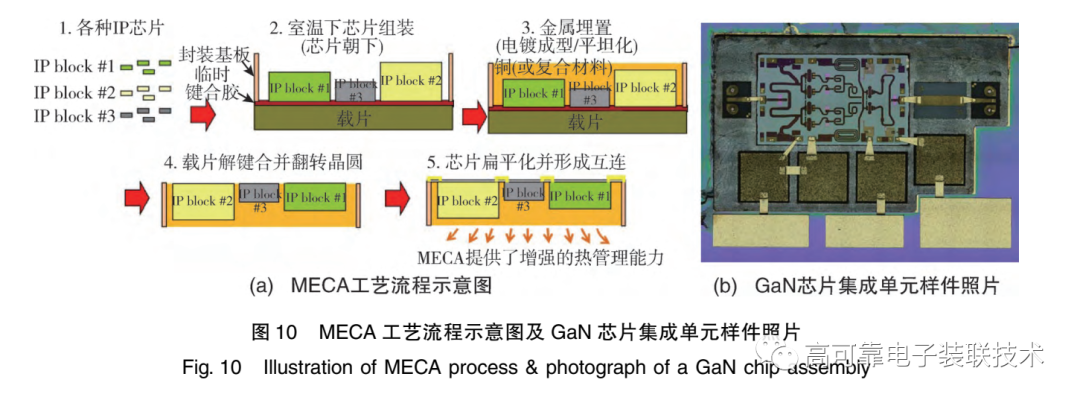

此外,由于芯片與埋置材料為同質材料, 克服了塑封重構晶圓在多芯片封裝時翹曲控制的難題[30] 。玻璃以其良好的尺寸穩定性、 優良的高頻介電性能以及可制作高密度垂直互連通孔(THROUGHGLASS VIA, TGV)等 獨 特 優 勢, 也 被 應 用 到 RF?SIP 扇 出 封 裝中[25, 31?32] 。美國休斯實驗室(HRL) 提出了一套面向高性能相控陣應用的金屬埋置芯片組裝工藝(METAL?EMBEDDED CHIP ASSEMBLy,MECA ) 。

如 圖 10 所示[33?34] , 包含 GAN 毫米波功放芯片在內的多顆異質芯片在室溫下臨時鍵合到載片上,之后通過電鍍銅填充工藝將所有芯片進行埋置,去掉臨時載片之后制作空氣橋進行芯片互連。MECA 提供了良好的散熱環境, 相比 AUSN 共晶到鎢銅熱沉的工藝, GAN芯片輸出功率提升了 42% 。此外, 國內基于多層共燒陶瓷(如 ALN) 制作盲腔,利用苯并環丁烯(BENzO?CyCLO?BUTENE, BCB) 作為填充介質預埋置芯片, 然后采用CMP 工藝平坦化并露出芯片凸點, 進一步制作 RDL 互連。中國電科 38 所[35] 和14 所[36] 分別對陶瓷盲腔的激光加工技術和埋置應力進行了研究,成功制作了陶瓷基的射頻埋置扇出系統級封裝電路結構, 在保留了多層陶瓷封裝高導熱、 高布線層數等原有特點的同時, 利用RDL 技術提升了互連性能并降低了封裝剖面厚度。

3 三維堆疊技術

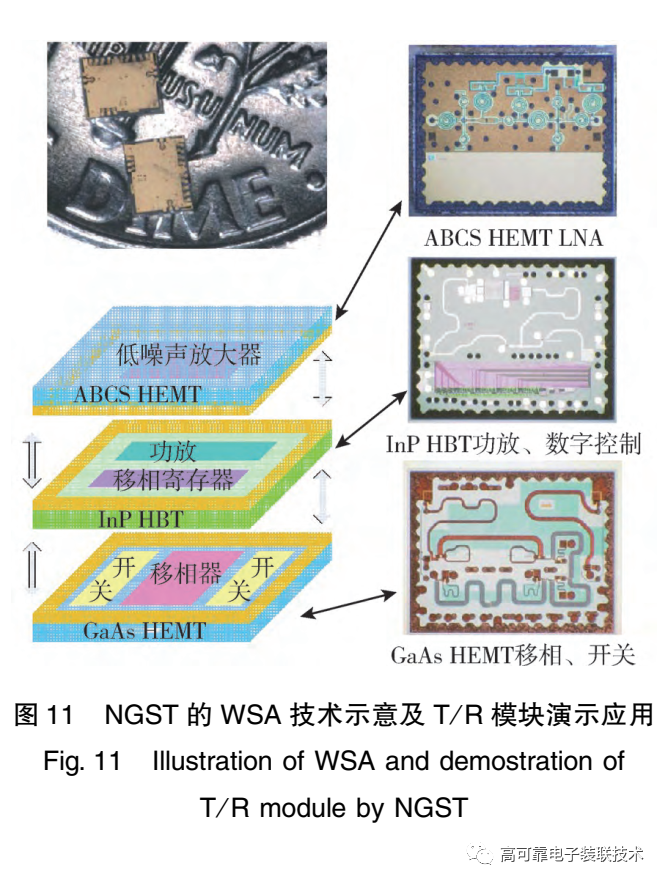

三維堆疊技術在 Z 方向上擴展 SIP的集成維度是異構集成公認的技術方向, 然而射頻鏈路中大量的無源器件采用分布參數設計, 當芯片或封裝基板緊密堆疊時, 電磁場的耦合可能導致電路性能嚴重下降甚至不能正常工作。因此,充分考慮射頻性能的約束是RF?SIP 應用三維堆疊技術的關鍵。從堆疊互連的對象不同, 三維堆疊技術可分為芯片堆疊(3D?IC) 和封裝堆疊(PACKAGING ON PACKA?GING, POP) 兩大類型。 射頻電路的芯片?芯片堆疊較早的嘗試是諾斯洛普空間技術公司(NGST) 2007 年開發的晶圓級組裝(WAFER SCALE ASSEMBLy,WSA) 技術[37] ,通過晶圓級 AU?IN 低溫鍵合形成腔內互連(INTRA?CAVITy INTER?CONNECTIONS, ICIC ) , 實 現 了 僅 2。

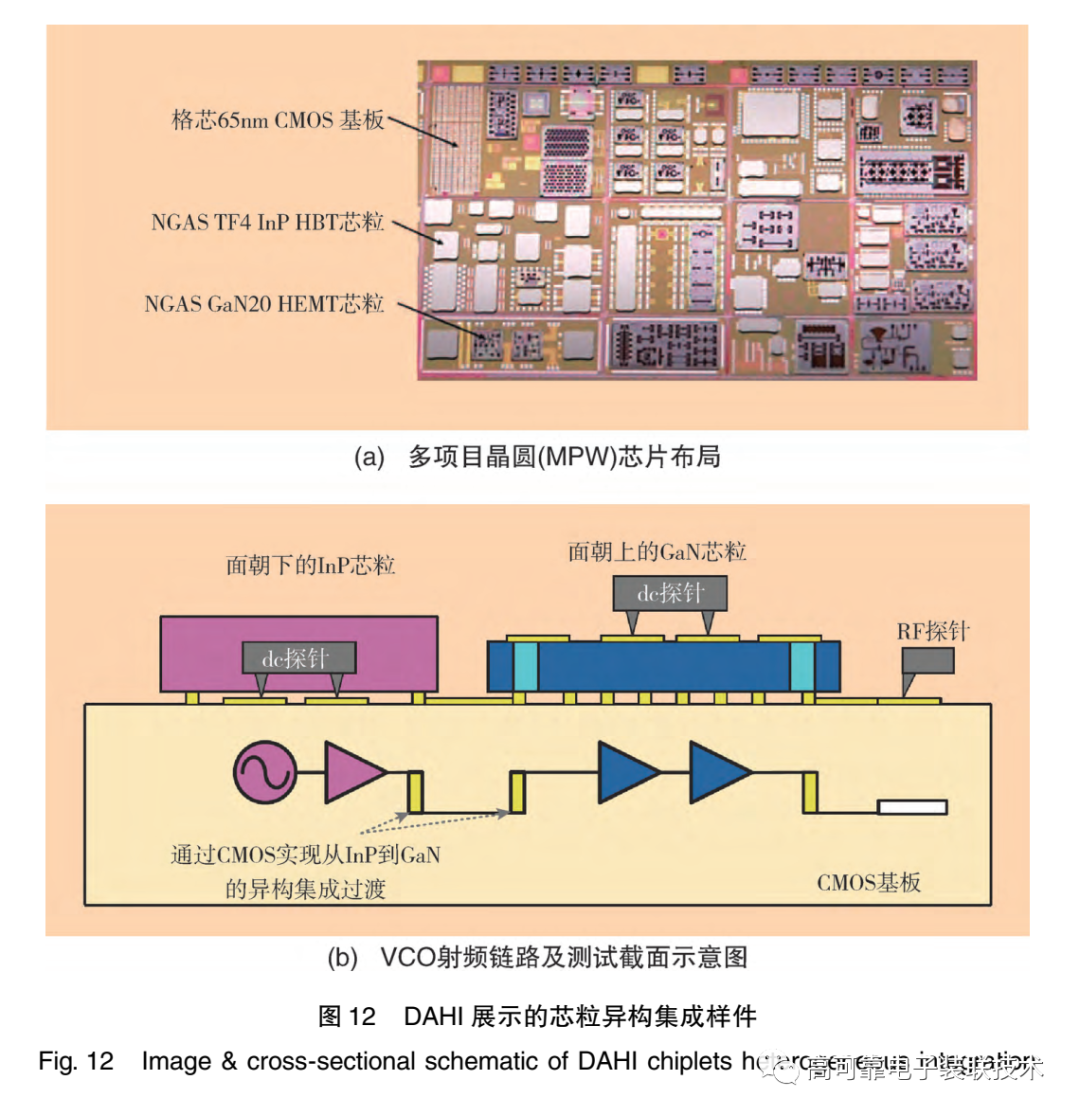

5MM× 2MM ×0。 46MM 的超小型氣密封裝 X頻段 T / R 組件, 相比傳統金屬封裝, 體積和質量僅為原來的 1 / 1000[38] ,如圖 11 所示。NGST 進一步開發了 KU、 Q、 W 等頻段的三維集成芯片, 并取得了與傳統芯片幾乎相同的性能,但傳統芯片設計移植到新的 WSA 體系必須重新進行仿真設計, 以評估封裝的空氣腔對性能的影響, 并通過電路的調整優化實現預定的性能指標。為了充分利用不同材料和不同工藝的成熟半導體技術,以高性價比構建性能優越的微系統, DARPA 在 2013 年啟動了多樣化可用異構集成項目(DIVERSE ACCESSIBLEHETEROGENEOUS INTEGRA?TION, DAHI) , 采用芯粒集成(CHIPLET) 、晶圓鍵合以及外延轉移等技術實現了例如 GAN HEMT、 INPHBT、 CMOS 等芯片間低寄生效應的緊密垂直堆疊互連, 如圖 12 所示[39] 。

在 DAHI 項目所展示的集成范式下, 所集成的芯片無需更改其制程即可實現廣泛來源的晶體管級集成,有關 DAHI 的研究成果已有較好的文獻綜述可供參考[39?41] 。與此類似的異構芯片堆疊集成技術在國內也得到了研究和開發,如中國電科 13 所公布的發明專利[42] 闡述了一種多通道幅相控制芯片,由上層的硅基 CMOS 譯碼電路芯片與下層的 GAAS 射頻芯片通過直徑 50μM~ 80μM 的金球鍵合實現垂直堆疊。射頻芯片與數字芯片的直接混合堆疊無需額外的轉接板, 集成密度和成本優勢明顯, 未來的工程應用將迅速增長。

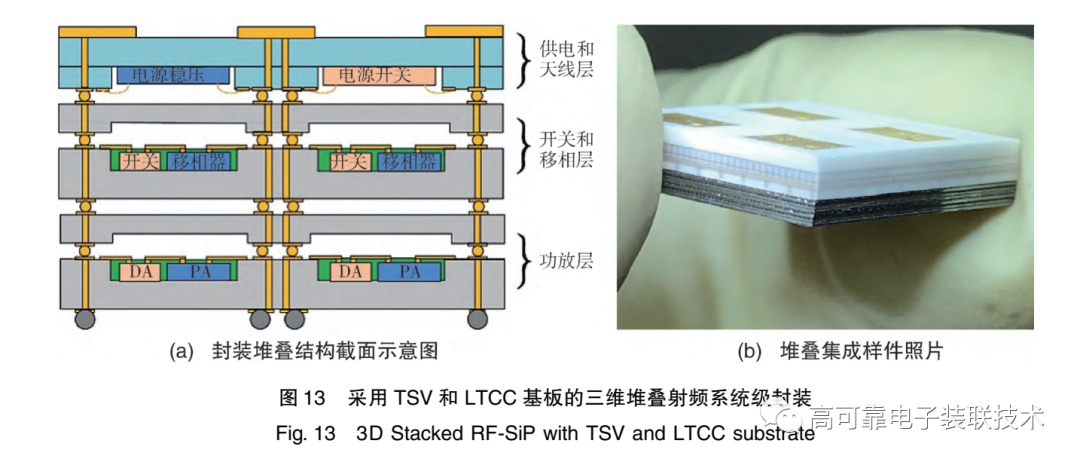

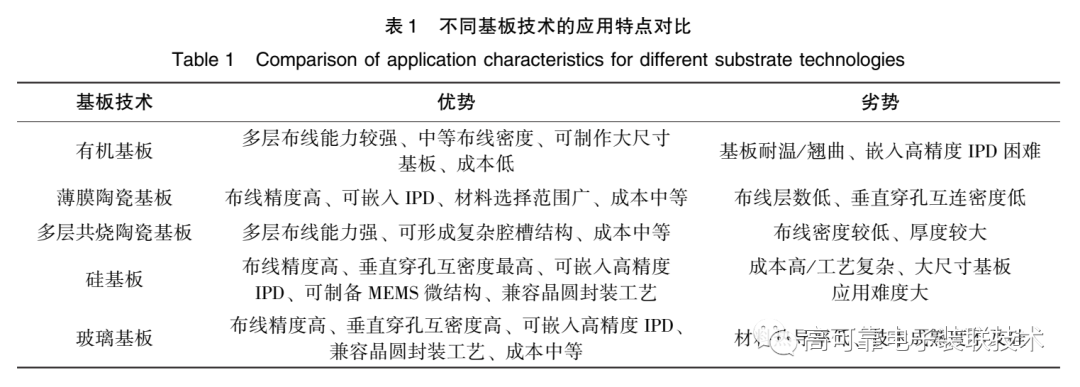

因芯片尺寸的限制, 僅通過芯片?芯片的三維堆疊集成難以滿足電路的復雜度和集成規模需求,因此有必要在封裝級的三維堆疊基礎上進一步拓展集成密度,并借助封裝結構提升封裝內解決電磁兼容難題的靈活性。單獨的封裝堆疊單元由基板及裝配的芯片構成, 典型的基板包括有機基板[43?44] 、 薄膜陶瓷基板[45] 、 共燒多層陶瓷基板[46] 、硅基板[47?48] 、 玻璃基板[49] 等。此外, 實現塑封穿孔互連(THROUGH MOLDING VIA,TMV) 的扇出封裝[50]也可作為堆疊單元。混合基板封裝的堆疊可充分發揮不同基板技術的優勢, 以滿足更為復雜的系統集成需求, 如圖 13 所示[51] 的 4 通道發射模塊, 它采用了 TSV 和 LTCC 基板混合封裝堆疊方案,其中天線單元集成到 LTCC 基板上, 有效提升了系統集成度。一般來說, 不同的基板在封裝中應用特點各異, 歸納如表 1 所示。但需要指出的是, 隨著新的基板技術持續突破,優勢和劣勢對比并非一成不變。早期的堆疊互連技術多采用毛紐扣彈性互連方案[52] , 但由于毛紐扣的互連中心距和厚度均在毫米量級, 無法滿足系統級封裝需求。因此,封裝堆疊主要采用 BGA 焊球互連[43] 、 微凸點互連[51,53] 以及晶圓鍵合互連[54?55] 等技術。

4 RF?SIP互連技術面臨的挑戰與發展方向

微電子技術已進入異構集成時代, 將系統級封裝前沿技術應用到電子信息裝備是一項重大的課題,如:美國國防部(DOD) 于 2019 年啟動了高水平異質異構集成與封裝(STATE OF THE ART HETEROGENE?OUS INTEGRATION ANDPACKAGING, SHIP) 項目, 正在充分整合 QORVO 等行業領先公司的最新射頻異構封裝技術, 滿足下一代相控陣雷達系統、無人機、 電子戰以及衛星通信系統在體積、 質量、 功耗和成本(SWAP?C) 上的需求。結合 RF?SIP 的需求, 應重點關注以下先進封裝互連技術發展:

1)更高密度的無凸點互連技術。先進工藝節點的硅基 RF?IC 已經能夠處理高達 300GHz的射頻信號, 融合射頻與數字的混合信號 SIP 將會加速發展, 并將采用 CHIPLET 集成方案低成本地實現 IP 復用, 在獲得最佳系統性能的同時縮短產品開發周期。混合信號 SIP 對互連節距的要求將縮放至小于10μM 量級, 當前成熟并且廣泛應用的微凸點互連很可能成為瓶頸。基于以上需求, DIE?TO?WAFER[56]或 WAFER?TO?WAFER[57] 無凸點直接鍵合(DBI) 可能是最優的互連解決方案。

2)高頻高性能先進基板材料。在無機基板材料方面, 玻 璃/ 石 英 具 有 低 介 電 常 數 和 低 成 本 優勢[58?59] , 隨著玻璃穿孔互連工藝的成熟以及供應鏈的完善, 工程應用價值將逐步顯現;而硅材料在MEMS 技術中得到了廣泛深入的研究,在射頻系統級封裝領域正得到行業的密切關注[53, 55] ;碳化硅、氮化硅等材料的熱導率、強度等性能突出, 有望在解決功率射頻系統級封裝中發揮重要價值。得益于 5G 毫米波商業化的推動, 高頻低損耗有機基板材料的開發和應用發展迅速[60?61] , 其中作為晶圓級封裝的關鍵材料, 介質損耗(DF) 低至 10 - 3量級的光敏介質對提升基板及 RDL 的射頻性能具有重要意義。

3)熱/ 電一體高性能互連技術。隨著 GAN 等器件功率密度的提升, RF?SIP 中的熱?電耦合更為緊密。因此, 在電互連結構中同時實現高效的熱傳導具有良好的前景, 如通過密集的實心填充通孔解決玻璃轉接板散熱性能不足的問題[62] 、 通過在TSV 轉接板中引入液冷流體實現大功率散熱[63] 等。賓夕法尼亞大學的 SHOEMAKER 等[64] 提出了在 GAN芯片上制作金剛石鈍化層, 再用金凸點倒裝集成到金剛石基板的互連架構, “結?封裝” 熱阻可低于最新的金剛石上 GAN(GAN?ON?DIAMOND) 技術。這些新興的熱/ 電一體高性能互連技術仍處于原理驗證階段, 后續亟需利用有效的熱阻分析方法[65] 驗證其性能, 并在工程環境下實現產品級的工藝整合。

4)芯片?封裝的協同設計與優化技術。在高頻下, 封裝與芯片間存在的 “機、 電、 熱、 磁” 耦合對性能的影響已不可忽略。比如應用倒裝或扇出互連技術時,RF 芯片中的傳輸線、 電感與封裝布線可能存在強烈的耦合, 底部填充材料除了提升產品可靠性, 也會改變傳輸線阻抗并可能使芯片性能漂移。為提高設計一次成功率,采用電磁仿真技術進行芯片?封裝協同設計與優化是 RF?SIP開發中的一項關鍵技術[66] 。為了降低協同難度,需要針對特定的封裝工藝開發組裝設計套件(AS?SEMBLy DESIGN KITS,ADKS) , 并在此基礎上建立基于模型驅動的 EDA 設計環境, 實現芯片與封裝設計最大程度的解耦。

5 結論

先進封裝互連技術是 RF?SIP 持續提升集成密度和性能的關鍵使能技術。芯片倒裝、 芯片埋置與扇出以及三維堆疊是目前主流和最重要的先進互連技術:射頻芯片倒裝需要特別考慮芯片?封裝協同設計及化合物半導體芯片的微凸點制備工藝;在射頻系統級封裝領域出現了多種芯片埋置與扇出技術變體,在降低傳輸損耗、 提升功率等方面進行了有效拓展;3D?IC 和 POP 兩個層面的三維堆疊互連為RF?SIP 的技術創新打開了新的維度。為滿足未來下一代電子信息裝備 SWAP?C 的需求, 射頻系統級封裝的互連技術應重點關注無凸點互連、高頻高性能先進基板材料、 熱/ 電一體高性能互連、芯片?封裝的協同設計與優化等技術的發展。

編輯:黃飛

電子發燒友App

電子發燒友App

評論