230MHz無線電臺通信系統(tǒng)在電力負荷管理系統(tǒng)和用戶用電信息采集系統(tǒng)中有著廣泛的應(yīng)用。然而,隨著無線通信技術(shù)的發(fā)展,在不同時期投入應(yīng)用的無線電臺,雖然基本結(jié)構(gòu)類似,但調(diào)制方式、波形結(jié)構(gòu)、調(diào)制速率都有較大差別,不同的設(shè)備占用不同頻段單獨組網(wǎng),獨立運行,十分不利于系統(tǒng)的維護,而且,隨著對高速通信電臺設(shè)備需求的增加[1],使得通信系統(tǒng)結(jié)構(gòu)更加復(fù)雜。

為了解決上述問題,本文基于GNU Radio?系統(tǒng)提出了一種多信道、多傳輸速率、多調(diào)制方式的軟件無線電多通道主站電臺的系統(tǒng)結(jié)構(gòu)。該系統(tǒng)在調(diào)制方式上與現(xiàn)有的無線電臺設(shè)備全面兼容,覆蓋整個電力系統(tǒng)230 MHz?全雙工頻段,可以同時在多個頻點運行,以不同的速率、調(diào)制方式進行通信,很好地保證了現(xiàn)有業(yè)務(wù)的正常運營。此外,基于軟件無線電的系統(tǒng)具有極強的可配置性,為將來的業(yè)務(wù)拓展和設(shè)備升級提供了可靠保障,降低了系統(tǒng)的維護和升級成本。

1、230 MHz?無線通信系統(tǒng)分析

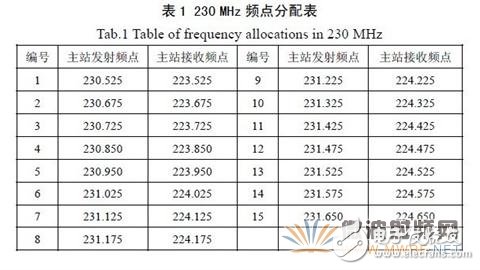

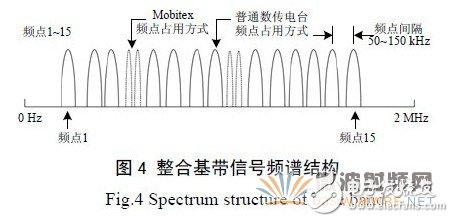

230MHz無線通信系統(tǒng)由主站電臺和從站電臺組成,主站采用全雙工電臺,從站采用半雙工電臺。無線電管理委員會將230 MHz?頻段的15?對雙頻頻點分配給電力系統(tǒng)專用[2],頻點分配如表1?所示。每個頻點帶寬為25 kHz,相鄰頻點間隔為50~150 kHz,15?個接收/發(fā)送頻點總帶寬約為2 MHz,上下行頻率間隔為7 MHz。

目前電力行業(yè)中使用的大部分是模擬調(diào)頻電臺,電臺內(nèi)增加調(diào)制解調(diào)模塊后進行數(shù)據(jù)傳輸。早期的低速電臺采用FSK,MSK?等調(diào)制方式,傳輸速率為600~2 400 bps;高速電臺采用GMSK?調(diào)制方式,實現(xiàn)9 600 bps?的信號收發(fā)。此外,部分地區(qū)運行著230 MHz?頻段的Mobitex?系統(tǒng),它直接采用GMSK?調(diào)制,避免了第二級FM?調(diào)制對信道資源的浪費,僅占用12.5 kHz?的射頻帶寬,實現(xiàn)了8 kbps數(shù)據(jù)傳輸。

2、GNU Radio?主站電臺總體設(shè)計

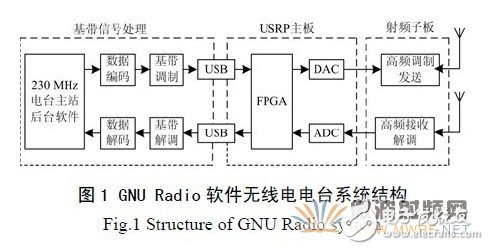

GNURadio?系統(tǒng)是一種運行于通用處理器(GPP)上的開放的軟件無線電平臺,并配以USRP(Universal Software RadioPeripheral)作為硬件射頻前端。GNU(GNU’s Not Unix)是一個推進軟件開放源代碼的著名項目,由FSF(Free SoftwareFoundation)提供支持。GNU Radio?運行于Linux操作系統(tǒng),其軟件代碼和硬件設(shè)計完全公開,其設(shè)計的核心思想是:基帶信號處理過程由通用處理器而不是DSP?實現(xiàn);基帶信號通過USB 2.0?接口與USRP?系統(tǒng)相連,由USRP?上的FPGA?實現(xiàn)數(shù)字上下變頻,然后通過AD/DA?芯片與射頻子板連接;覆蓋不同頻段的射頻子板將模擬信號變換到射頻進行信號收發(fā)。

本文設(shè)計的多通道主站電臺系統(tǒng)的系統(tǒng)結(jié)構(gòu)如圖1?所示,由基帶信號處理部分、USRP?主板、230 MHz?射頻子板三個部分組成。

(1)基帶信號處理部分

基帶信號處理部分包括數(shù)據(jù)緩存、編解碼、調(diào)制解調(diào)等模塊。這部分的主要工作是基帶信號處理模塊和信號收發(fā)流圖(Flow Graph)的設(shè)計。此外,可使用WxPython?跨平臺GUI?工具庫編寫人機交互界面,采用MySQL?作為數(shù)據(jù)庫系統(tǒng)。

(2)USRP?主板

USRP主板實現(xiàn)了信號的中頻處理,主要為數(shù)字上下變頻操作。板載FPGA?芯片采用了Altera?公司生產(chǎn)的Cyclone?系列芯片EP1C12Q240C8,設(shè)計開發(fā)工具為Quartus II 7.2,各模塊邏輯采用Verilog語言描述。

(3)230 MHz?射頻子板

目前?USRP?配套的全雙工子板沒有覆蓋到230MHz?頻段,本文根據(jù)USRP?主板與子板連接的接口說明,設(shè)計了收發(fā)頻率覆蓋200~250 MHz?的射頻子板。同時,由于子板輸出功率過小,發(fā)送信號需外接至大功率天線設(shè)備輸出。

3、GNU Radio?主站電臺基帶信號處理

GNURadio?的基帶信號處理編程基于C++和Python?腳本語言的混合方式。C++執(zhí)行效率較高,用于編寫各種底層信號處理模塊。Python?是一種新型的腳本語言,用來編寫連接各個信號處理模塊的腳本,最終使之成為完整的信號收發(fā)流圖。

3.1GNU Radio?基帶信號處理模塊設(shè)計

GNURadio?提供一個基帶信號處理的底層模塊庫,含有100?多種信號處理模塊,如:濾波器,F(xiàn)FT?變換、調(diào)制解調(diào)器、時頻同步模塊等[3]。

本系統(tǒng)同時支持多種無線通信電臺,而不同電臺的調(diào)制方式、信號速率可以不相同。通過分析可知,電臺系統(tǒng)中基帶信號所用的數(shù)字調(diào)制方式如FSK、MSK、GMSK?等均屬于恒包絡(luò)調(diào)制方式,這些信號都可以通過FM?調(diào)制器輸出。

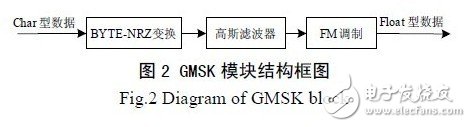

下面以?GMSK?調(diào)制模塊為例簡要說明GNURadio?信號處理模塊的實現(xiàn)原理及實現(xiàn)方法。

從?Python?的角度來講,GNU Radio?提供了一種信號流圖的抽象,用戶可以方便地使用底層信號處理模塊連接各種通信模塊,最終組成完整的無線通信系統(tǒng)。首先從gnuradio?包中導(dǎo)入gr?和modulation_utils?模塊,并在__init__()方法的參數(shù)中定義模塊中每符號的采樣點個數(shù)、BT值和程序調(diào)試接口等。定義完這些參數(shù)之后,方法調(diào)用其父類gr_hier_block2?的__init__()方法設(shè)定該模塊的輸入輸出接口類型,本模塊輸入為要傳輸?shù)臄?shù)據(jù)字節(jié),輸出為GMSK?的調(diào)制波形。

GMSK調(diào)制模塊由三個底層信號處理模塊構(gòu)成,分別是字節(jié)到NRZ?編碼變換器,高斯濾波器和FM?調(diào)制器(FM?調(diào)制器模塊需自行編寫,系統(tǒng)提供的FM?調(diào)制器輸出為復(fù)采樣信號,本調(diào)制器輸出為實采樣信號)。配置好這些模塊之后,調(diào)用connect函數(shù)將這些模塊連接,就形成了新的GMSK?調(diào)制模塊。其結(jié)構(gòu)圖如圖2?所示。其他調(diào)制方式如FSK、MSK?調(diào)制模塊與之十分類似,不再贅述。

通過?Python?語言構(gòu)造信號處理模塊非常靈活,大幅提高了代碼的復(fù)用度。但由于底層模塊庫并不完備,在執(zhí)行某些數(shù)據(jù)處理時還需采用C++語言編寫對應(yīng)的底層模塊,如糾錯編碼、多相濾波發(fā)送、多相濾波接收等,編寫底層模塊的具體方法可參考文獻[4]。

3.2基帶信號收發(fā)流圖設(shè)計

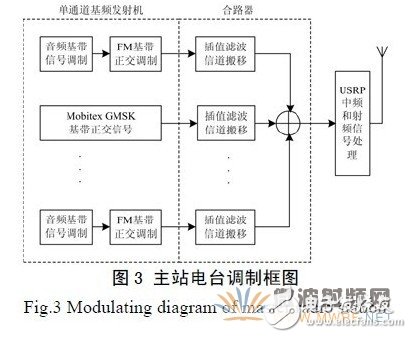

本系統(tǒng)同時覆蓋了230 MHz?頻段的15?個雙工頻點,如果將這15?個支路的信號分別通過獨立的載波調(diào)制解調(diào),系統(tǒng)將過于復(fù)雜。因此,本文采用了信道化收發(fā)機的系統(tǒng)結(jié)構(gòu),即一部收發(fā)機同時處理信道帶寬內(nèi)所有信道上的信號。

圖?3?是主站電臺信道化發(fā)射機基本調(diào)制原理框圖。基帶信號的處理分為了兩部分工作:

第一步是由N?個單通道基頻發(fā)射機產(chǎn)生N?個基帶數(shù)字信號。對于普通數(shù)傳電臺,首先根據(jù)不同的基帶調(diào)制方式(FSK、MSK、GMSK?等)輸出基帶信號,再由FM?基帶正交調(diào)制器進行復(fù)合調(diào)制,調(diào)制完成后的基帶信號數(shù)字譜帶寬為25 kHz。對于Mobitex?電臺,直接輸出速率為8 kbps?的GMSK?基帶正交信號,數(shù)字譜帶寬為12.5 kHz。

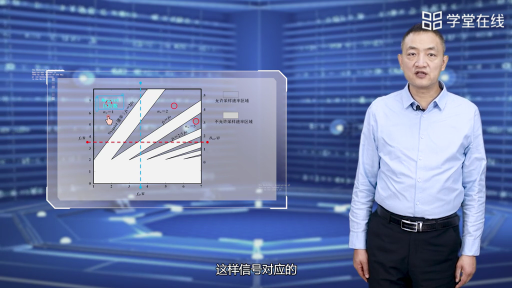

第二步將調(diào)制完成的各路基帶信號進行插值濾波,并分別根據(jù)各路占用的不同頻點,用移頻因子ejωk t?搬移到虛頻點ωk(即射頻頻點相差230 MHz的基帶頻點)處,最后將所有支路上的信號整合,得到覆蓋0~2 MHz?的整合基帶信號,其頻譜結(jié)構(gòu)如圖4?所示。在具體實現(xiàn)時,本文采用了基于多相結(jié)構(gòu)的信道化發(fā)射機模型以提高計算效率和實時處理能力,實現(xiàn)細節(jié)請參閱文獻[5]。

合路器輸出的整合基帶信號的復(fù)采樣頻率為6 MHz,精度為8 bit,這樣每個復(fù)采樣點占據(jù)2?個字節(jié),通過USB2.0?接口傳輸?shù)経SRP,雙向收發(fā)占用的USB?帶寬為24 MByte/s。在USRP?中,基帶信號再通過插值和濾波變換為固定速率的中頻信號并送到D/A?轉(zhuǎn)換器轉(zhuǎn)換為模擬信號,最后在射頻子板轉(zhuǎn)換為射頻信號發(fā)射。

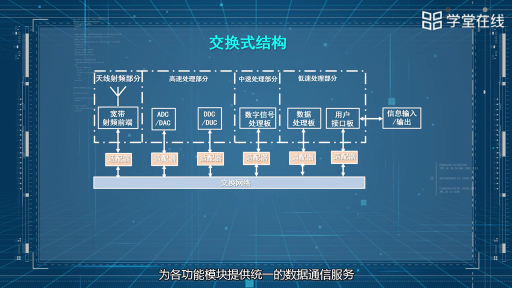

4、USRP?主板FPGA?配置

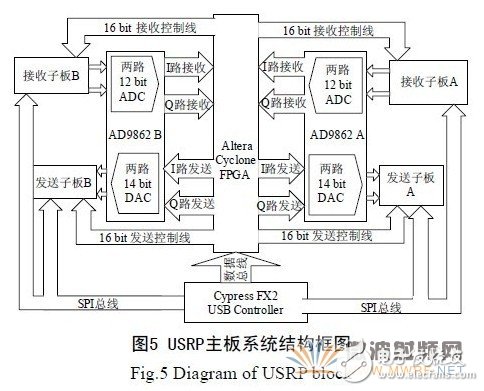

USRP主板上可支持兩路信號并行收發(fā),結(jié)構(gòu)框圖如圖5?所示,本文中只使用其中一路。FPGA芯片處于USRP?主板中的核心位置,內(nèi)部邏輯通過Verilog?語言描述。它的主要功能是將ADC?采來的中頻信號進行數(shù)字下變頻(DDC),并將基帶信號進行插值濾波、速率匹配、輸出到DAC?進行數(shù)字上變頻(DUC),同時還要控制子板信號收發(fā),適配各路ADC,DAC?與PC?機之間的數(shù)據(jù)交換。

USRP提供了標準系統(tǒng)的Verilog?代碼供用戶使用,但需要針對不同的信號帶寬,信號精度和外插子板情況對Verilog?文件進行改寫并重新編譯后,下載到FPGA?中運行。

本系統(tǒng)中,AD采樣輸出的數(shù)據(jù)為兩路12bits、64MSample/s的正交中頻信號,F(xiàn)PGA要首先對其中有用的信號進行下變頻。

數(shù)字下變頻的第一步是對信號進行混頻,這部分主要由乘法器和DCO組成。USRP采用坐標旋轉(zhuǎn)數(shù)字計算(CORDIC)算法生成正弦和余弦信號[6],與常規(guī)的查表法不同,CORDIC算法不占用存儲器空間,僅使用移位寄存器和加法器就可產(chǎn)生正余弦信號,具有很好的NCO的精度。

數(shù)字下變頻的第二個環(huán)節(jié)是對混頻后的信號進行抽取濾波,以便降低軟件解調(diào)的計算復(fù)雜度。USRP使用了由一個4級CIC抽取濾波器和一個31階半帶濾波器組成的混合濾波器結(jié)構(gòu)。CIC濾波器為整系數(shù)濾波器,濾波時無需乘法運算,而半帶濾波器有一半系數(shù)為零,這樣在濾波時大大減少了計算量[7]。濾波的同時,在CIC濾波器實現(xiàn)了4倍的數(shù)據(jù)抽取,在半帶濾波器實現(xiàn)了2倍的數(shù)據(jù)抽取,這樣就得到了帶寬為2MHz的兩路8 bits,8MSample/s的正交基帶信號。

對于發(fā)送信號,F(xiàn)PGA將USB傳輸?shù)牡退俾驶鶐盘栠M行插值并濾波,變換為32 MSample/s的采樣信號并輸出到DAC單元的數(shù)字上變頻模塊中,最終以兩路14 bits,128 MSample/s的速度轉(zhuǎn)換為模擬信號。

5、230 MHz?射頻子板的實現(xiàn)

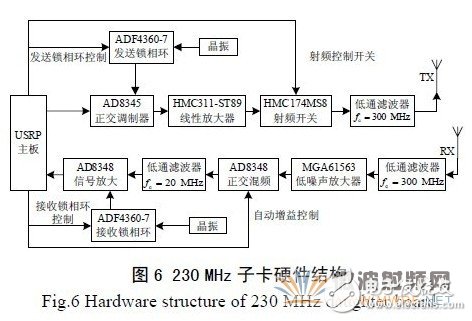

USRP的子板有很多種規(guī)格,分別針對了基帶信號處理、廣播電視接收、移動通信信號處理等領(lǐng)域。但由于在230 MHz?頻段沒有可用的全雙工子卡,本文根據(jù)USRP?與子卡的接口說明,設(shè)計了針對230MHz?頻段應(yīng)用的全雙工子卡,實現(xiàn)信號收發(fā)。其硬件實現(xiàn)結(jié)構(gòu)如圖6?所示。

230MHz?子板采用AD8345?和AD8348?分別作為調(diào)制器和解調(diào)器。AD8345?是ANALOG DEVICES公司推出的正交調(diào)制器,其工作頻率為140~1000MHz,在數(shù)字通信系統(tǒng)中可用作中頻調(diào)制器或直接上變頻器。AD8348?是ANALOG DEVICES?公司推出的正交解調(diào)器,其工作頻率為50~1000 MHz,解調(diào)帶寬75 MHz,內(nèi)部集成中頻可變增益放大器。

AD8345和AD8348?輸入的本振頻率是兩塊ADF4360-7?鎖相環(huán)輸出的,本振頻率分別為460 MHz和446 MHz。460 MHz?的信號在ADF4360-7?內(nèi)部二分頻輸出至AD8345,446 MHz?信號在AD8348?內(nèi)部進行二分頻。芯片內(nèi)部VCO?的中心頻率設(shè)為460 MHz,這個中心振蕩頻率值是由外部電感設(shè)置的,它們之間的對應(yīng)關(guān)系為:

通過計算可得,外部電感的值為3.84 nH。子板系統(tǒng)中晶振輸出的參考頻率為10 MHz,通過SPI總線控制配置ADF4360中的14?位R?計數(shù)器值為200,再配置N?計數(shù)器數(shù)值,就可以以50 kHz?的步長,覆蓋420~500 MHz?的頻率范圍。

此外,由于USRP?的板載電源功率過小,子板的天線接口只能提供了100MW?的功率輸出,而一般的230MHz?主站電臺的功率為15 W?左右,因此,還需要在另外加裝高增益的外接天線。

6?結(jié)束語

本文提出了一種基于GNU Radio?的多速率、多種調(diào)制方式、多信道的軟件無線電主站電臺的系統(tǒng)結(jié)構(gòu)。該系統(tǒng)基于通用硬件平臺,成本較低,既充分的利用了現(xiàn)有的無線電臺資源,實現(xiàn)多種電臺的全面兼容,又為將來的業(yè)務(wù)拓展和設(shè)備升級提供了保證。該系統(tǒng)使用純軟件的信號處理具有很大的靈活性,采用高級語言(C/C++、Python)進行系統(tǒng)開發(fā),擴展性和可移植性強,開發(fā)周期短,并且隨著CPU?處理能力的不斷提高以及軟件技術(shù)的進步,系統(tǒng)性能還有進一步提升的空間。

參考文獻

[1]周立巖,孫毅,馮小安.?提高電力負荷管理系統(tǒng)通信效率的新方法[J].?電力系統(tǒng)通信,2008,28(128):46-49.ZHOU Li-yan,SUN Yi,F(xiàn)ENG Xiao-an. New MethodofImproving Communication Efficiency in Power LoadManagement System[J].Telecommunications for ElectricPower System,2008,28(128):46-49.

[2]無管字5?號,民用超短波遙測遙控數(shù)據(jù)傳輸業(yè)務(wù)頻率劃分[S].Radio AdministrativeBureau No.5?,?Frequency Allocations ofCivil Ultrashort Wave Telemetering and Telecontrol Data Trasmit Servies[S].

[3]曹瀚文,王文博. GNU Radio:開放的軟件無線電平臺[J].?電信快報,2007(4):31-34.CAO Han-wen,WANG Wen-bo. GNU Radio:OpenSource SDRPlatform[J]. Telecommunication Information,2007(4):31-34.

[4]Blossom E. How to Write a Signal Processing Block[EB/OL].?2006.

[5]楊小牛,樓才義,徐建良.?軟件無線電原理與應(yīng)用[M].北京:電子工業(yè)出版社,2001.68-85.YANG Xiao-niu,LOU Cai-yi,XU Jian-liang. Principles andApplications of Software Defined Radio[M].Beijing:Publishing House of ElectronicsIndustry,2001.68-85.

[6]Ray Andraka. A Survey of CORDIC Algorithms for FPGA Based Computers[A]. in: Proceedingsof the 1998 ACM/SIGDA Sixth International Symposium on Field Programmable GateArrays[C]. 1998. 191-200.

[7]徐以濤,沈良,王金龍. FPGA?技術(shù)在軟件無線電中的應(yīng)用[J].?電信科學,2001,11:36-39. XU Yi-tao,SHEN Liang,WANG Jin-long. Applicationof FPGA Technology in Software Radio [J]. Telecommunications Science,2001,11:36-39.

電子發(fā)燒友App

電子發(fā)燒友App

評論