簡介

無線通信網(wǎng)絡(luò)正在迅猛發(fā)展。在多種空中標(biāo)準(zhǔn)共存的同時(shí),消費(fèi)者對數(shù)據(jù)服務(wù)需求的快速擴(kuò)張呼喚更廣的覆蓋范圍和更寬的帶寬。不同的無線電技術(shù)以及不斷增加的頻率分配使控制網(wǎng)絡(luò)和降低成本變得更為復(fù)雜。無線服務(wù)提供商正在尋求不僅能保護(hù)他們的現(xiàn)有投資,并且還能簡化系統(tǒng),以便未來網(wǎng)絡(luò)升級和擴(kuò)容的解決方案。

為了滿足這些需求,必須通過有效且相對廉價(jià)的方案來解決多頻段、多標(biāo)準(zhǔn)無線電(MB-MSR)基站構(gòu)建問題。支持基站設(shè)計(jì)變革的技術(shù)進(jìn)步之一是新一代射頻數(shù)模轉(zhuǎn)換器(RF DAC),比如ADI公司的AD9129。本文將論述采用RF DAC設(shè)計(jì)MB-MSR發(fā)射器時(shí)需要考慮的主要方面。

傳統(tǒng)發(fā)射器架構(gòu)

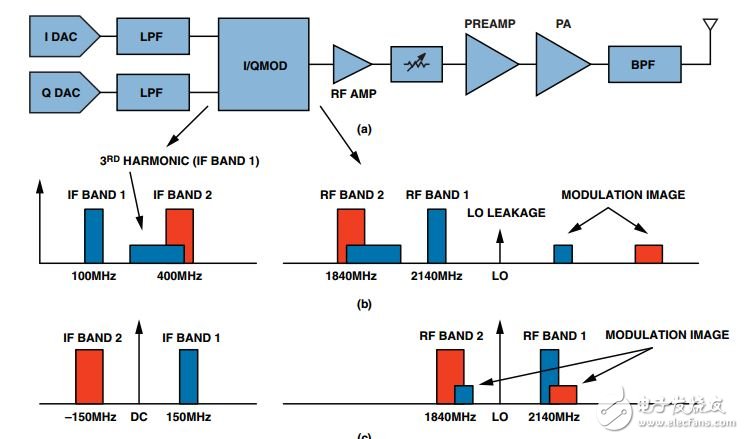

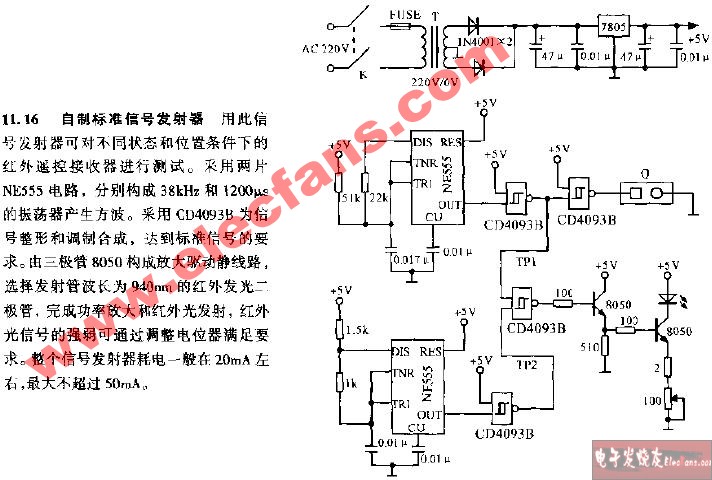

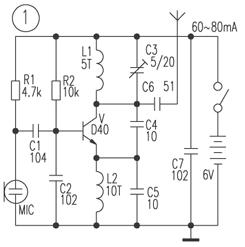

圖1(a)顯示了一個(gè)廣泛用于無線基站發(fā)射器設(shè)計(jì)的架構(gòu)。同相(I)和正交(Q)輸入數(shù)據(jù)經(jīng)過數(shù)字調(diào)制,然后由DAC轉(zhuǎn)換為一對中頻(IF)I和Q輸出信號。應(yīng)當(dāng)選擇合適的IF,以便其數(shù)值足夠高,使帶通濾波器能夠抑制調(diào)制鏡像;而同時(shí)又足夠低,使DAC能夠保持良好的輸出性能。該架構(gòu)已成功應(yīng)用于數(shù)代單頻段無線電設(shè)計(jì)中。

其優(yōu)點(diǎn)和設(shè)計(jì)權(quán)衡因素已廣為人知。然而,該架構(gòu)有一些固有的限制,在規(guī)劃多頻段無線電設(shè)計(jì)中的頻率時(shí)將會(huì)遇到諸多困難。圖1(b)顯示直接將此架構(gòu)應(yīng)用到多頻段設(shè)計(jì)時(shí)經(jīng)常會(huì)碰到的一種限制情形。在單頻段無線電應(yīng)用中,DAC輸出端的信號諧波通常視為帶外雜散信號,可由DAC之后連接的低通濾波器加以抑制。在雙頻段應(yīng)用中,這些諧波可能會(huì)成為帶內(nèi)信號并進(jìn)入較高的發(fā)射頻段內(nèi)。這一限制可通過圖1(c)所示方法加以避免。這兩個(gè)信號頻段圍繞復(fù)數(shù)域內(nèi)的直流居中配置。諧波變?yōu)閹庑盘枺赏ㄟ^濾波消除。該方法對DAC采樣速率和低通濾波器帶寬的要求也更低,因?yàn)閷?shí)際信號帶寬較窄。雖然如此,這種頻率規(guī)劃下的調(diào)制器輸出會(huì)產(chǎn)生問題。由于每個(gè)頻段與本振(LO)的距離有所不同,每個(gè)信號的調(diào)制鏡像將會(huì)在靠近另一頻段處下降。雖然復(fù)雜的正交誤差校正(QEC)算法有助于抑制該鏡像,它可能對基帶信號處理引擎造成額外的負(fù)擔(dān),因?yàn)楫?dāng)鏡像落入帶內(nèi)時(shí),模擬濾波技術(shù)不起作用。

?

圖1. 傳統(tǒng)發(fā)射器架構(gòu)中的雙頻段無線電(頻段1和頻段3)頻率規(guī)劃示例:a) 發(fā)射器信號鏈組成; b) IF變頻;c)直接變頻

直接至RF發(fā)射器架構(gòu)

從架構(gòu)的角度來說,DAC在無線電傳輸系統(tǒng)中扮演著關(guān)鍵的角色。DAC的速度和性能決定了執(zhí)行數(shù)模轉(zhuǎn)換時(shí),其有多接近天線。RF DAC將數(shù)字信號處理的范圍由基帶頻域擴(kuò)展至天線。它實(shí)現(xiàn)了基帶數(shù)字信號直接合成至最終輸出頻率,并事實(shí)上將傳統(tǒng)架構(gòu)的模擬上變頻操作帶進(jìn)了數(shù)字域中。數(shù)字頻率轉(zhuǎn)換在頻率規(guī)劃和噪聲等方面具有更高的靈活性和性能。這是MB-MSR設(shè)計(jì)特別引人入勝的地方。

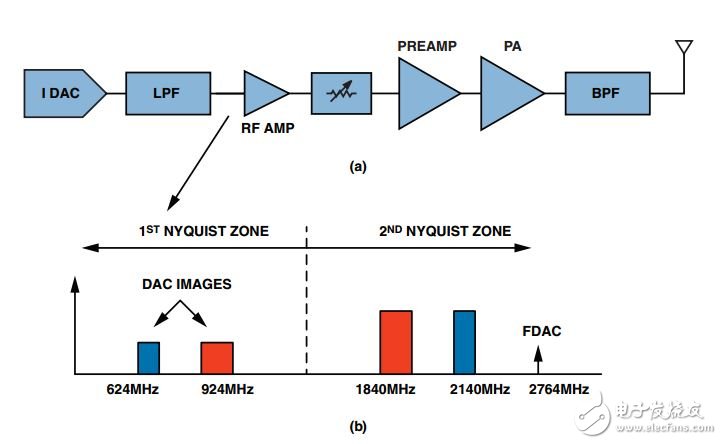

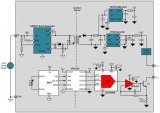

使用RF DAC可更靈活地進(jìn)行頻率規(guī)劃,因?yàn)閿?shù)字調(diào)制非常理想,且不產(chǎn)生干擾信號的調(diào)制鏡像。DAC采樣時(shí)鐘頻率是進(jìn)行頻率規(guī)劃時(shí)唯一需要確定的設(shè)計(jì)變量。圖2顯示采用RF DAC的直接RF頻率合成架構(gòu),以及該架構(gòu)在傳統(tǒng)架構(gòu)中可完美支持雙頻段應(yīng)用的能力。本例中,雙頻段信號在最終傳輸頻段中直接合成。選擇DAC采樣時(shí)鐘頻率,使信號諧波落在遠(yuǎn)離目標(biāo)頻段的位置,并且可在信號饋入下一個(gè)RF級之前加以過濾。

圖2. 直接至RF發(fā)射器架構(gòu)中的雙頻段無線電(頻段1和頻段3)頻率規(guī)劃示例:a) 發(fā)射器信號鏈組成; b) 直接至RF變頻

有兩個(gè)原因使直接至RF架構(gòu)的噪聲性能更佳。第一個(gè)原因是無需使用模擬上變頻級。在傳統(tǒng)架構(gòu)中,發(fā)射信號鏈的整體噪聲系數(shù)通常由調(diào)制器噪聲確定,因?yàn)镈AC對調(diào)制器輸出的噪聲貢獻(xiàn)相比折合到調(diào)制器輸出端的噪底而言一般更低。移除調(diào)制級可讓系統(tǒng)設(shè)計(jì)師降低系統(tǒng)噪聲系數(shù),方法是利用DAC的低噪底和RF放大器的高增益。噪底性能更佳的第二個(gè)原因是發(fā)射多頻段信號時(shí),天線的插入損耗更少。這是因?yàn)樗恍枰褂煤下菲鳌F DAC合成多頻段的能力改善了系統(tǒng)的整體性能,同時(shí)還降低了復(fù)雜程度,進(jìn)而縮小了尺寸和成本。

直接至RF架構(gòu)的電路板設(shè)計(jì)考慮

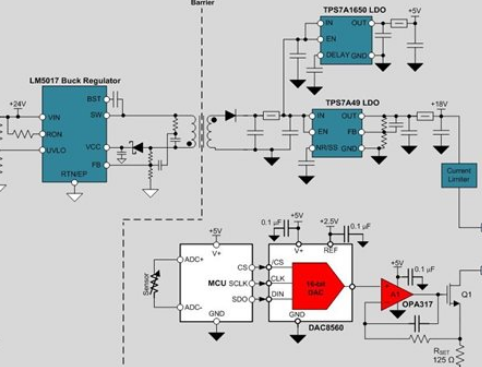

典型的多頻段通信系統(tǒng)包括數(shù)據(jù)接口邏輯、現(xiàn)場可編程門陣列(FPGA)或?qū)S?a target="_blank">ASIC、DAC、濾波器、增益模塊和RF功率放大器。在通道卡內(nèi),DAC用作數(shù)字邏輯和RF模擬輸出驅(qū)動(dòng)網(wǎng)絡(luò)之間的接口。DAC在系統(tǒng)中發(fā)揮著重要的作用,因?yàn)樗男阅堋⒉蓸铀俾屎蛶挾紩?huì)影響系統(tǒng)架構(gòu)和設(shè)計(jì)。

需重點(diǎn)關(guān)注某些關(guān)鍵電路——如DAC輸出路徑、時(shí)鐘電路、傳輸線路、電源和返回路徑——以確保它們的設(shè)計(jì)可實(shí)現(xiàn)最佳性能。可能需要對這些模塊以及DAC印刷電路板(PCB)進(jìn)行分析與仿真。

此外,電源布線也具有一定的挑戰(zhàn)性。數(shù)字邏輯包括I/O和內(nèi)核邏輯電源,而RF輸出網(wǎng)絡(luò)可包括多達(dá)四個(gè)或五個(gè)額外電源。電源域必須彼此隔離,信號返回路徑應(yīng)仔細(xì)管理,以確保電源域間無串?dāng)_。保持電源之間的隔離對于實(shí)現(xiàn)低噪聲性能而言極為關(guān)鍵。

DAC主時(shí)鐘是系統(tǒng)卡上最重要的信號。DAC時(shí)鐘為差分信號,通過護(hù)欄與其他信號隔離。此外,控制返回路徑,以確保無耦合或串?dāng)_。耦合至?xí)r鐘的任何信號將直接出現(xiàn)在DAC輸出端。破壞時(shí)鐘的數(shù)字信號可減少系統(tǒng)內(nèi)的噪聲裕量。必須防止DAC輸出耦合至?xí)r鐘,否則將造成二次諧波,甚至可能造成輸出頻譜的其他諧波問題。時(shí)鐘驅(qū)動(dòng)器最好盡可能靠近DAC,以減少噪聲和其他耦合問題。DAC輸出通過傳輸線路連接到各自的負(fù)載。仔細(xì)控制這些連接負(fù)載的傳輸線路的阻抗,確保DAC輸出信號具有可預(yù)測的性能。RF DAC的輸出阻抗與封裝和芯片有關(guān),因此進(jìn)行輸出級的分析和仿真時(shí)必須考慮到層壓板的影響。DAC與負(fù)載間的阻抗匹配非常重要,這是為了實(shí)現(xiàn)從DAC到目的地的最大能量傳輸,將從目的地返回DAC的反射降至最低。合理的傳輸線路設(shè)計(jì)可改善信噪比(SNR),對于優(yōu)秀的多頻段通信系統(tǒng)而言是必需的。

目前,典型的多頻段通信系統(tǒng)包括多RF鏈,它們由IF DAC、正交調(diào)制器、帶通濾波器、RF功率放大器和天線前的最終濾波器級組成。該架構(gòu)要求極大的電路板面積,以便將多個(gè)頻段集成到單個(gè)發(fā)射器中。如此多的元件功耗也非常大,并會(huì)產(chǎn)生相當(dāng)多的熱量,需通過散熱片或風(fēng)扇來散熱,這使得整體系統(tǒng)設(shè)計(jì)的復(fù)雜程度和成本都有所上升。由于RF DAC具有足夠的帶寬來合成多個(gè)RF頻段,因此它們可用來建立具有多頻段輸出的單個(gè)發(fā)射器。例如,三頻段發(fā)射器可能需要使用三對IF DAC,而三個(gè)調(diào)制器和三個(gè)帶通濾波器可用單個(gè)RF DAC和輸出濾波器代替,從而生成全部三個(gè)頻段。隨著功率放大器的設(shè)計(jì)向更寬的帶寬過渡,甚至可以節(jié)省更多電路板空間,因?yàn)橹恍柙诓煌琑F鏈上的功率放大器之后使用元器件即可,從而降低了所需元器件的數(shù)目。因此,采用RFDAC、DAC與功率放大器之間的輸出濾波器、功率放大器以及功率放大器與天線之間的輸出濾波器,便可實(shí)現(xiàn)多頻段發(fā)射器。

測量結(jié)果

信號鏈

?

?

?

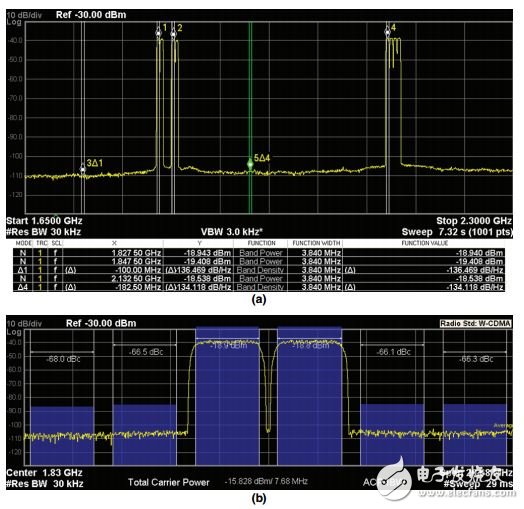

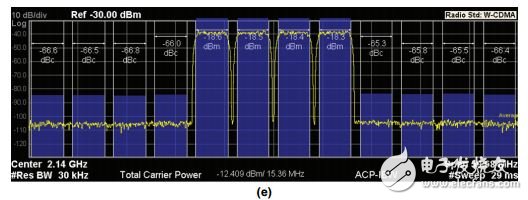

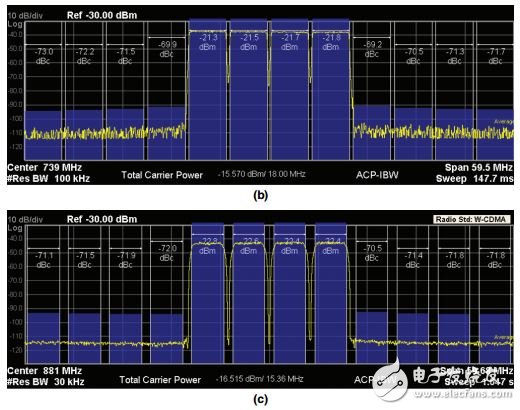

圖3. AD9129 RF DAC輸出的頻譜分析儀實(shí)測圖

(采樣速率為2764.8 MSPS):a)第二奈奎斯特區(qū)中的8個(gè)5 MHz寬W-CDMA通道;b) 1825 MHz至1835 MHz的2個(gè)5 MHz寬W-CDMA通道;c) 1845 MHz至1855 MHz的2個(gè)5 MHz寬W-CDMA通道;d) W-CDMA通道之間兩通道的間隙;e) 2130 MHz至2150 MHz的4個(gè)5 MHz寬W-CDMA通道

圖3顯示AD9129 RF DAC在2764.8 MSPS采樣速率下的輸出,采用DAC提供的可選模式,支持第二奈奎斯特區(qū)。八個(gè)5 MHz寬W-CDMA通道在三個(gè)不同頻段內(nèi)合成。建立兩個(gè)1825 MHz至1835 MHz通道、兩個(gè)1845 MHz至1855 MHz的通道,以及四個(gè)2130 MHz至2150 MHz的通道。信號在可編程門陣列(FPGA)內(nèi)產(chǎn)生,然后由RF DAC直接合成。

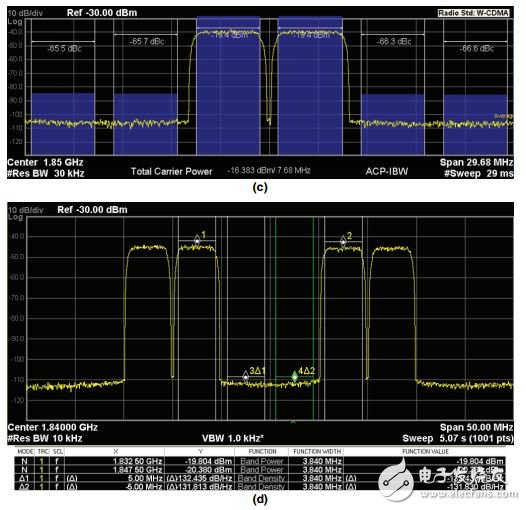

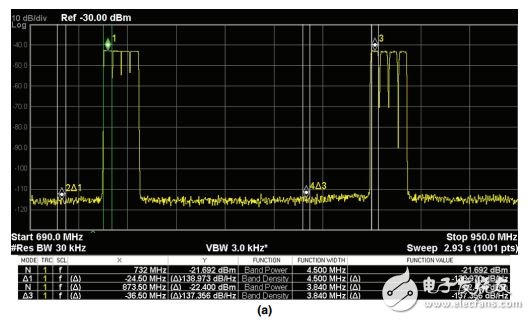

圖4顯示AD9129在2764.8 MSPS采樣速率下的輸出,使用的模式可在第一奈奎斯特區(qū)進(jìn)行頻率合成。帶有四個(gè)LTE下游通道的四個(gè)5 MHz寬W-CDMA通道在兩個(gè)不同的頻段內(nèi)合成。四個(gè)W-CDMA通道頻率范圍為871 MHz至891 MHz,建立的四個(gè)LTE下游通道頻率范圍為729 MHz至749 MHz。

?

?

圖4. AD9129 RF DAC輸出的頻譜分析儀實(shí)測圖

(采樣速率為2764.8 MSPS):a)第一奈奎斯特區(qū)中的4 MHz寬W-CDMA通道和4個(gè)5 MHz寬LTE通道;b) 729 MHz至749 MHz的4個(gè)5 MHz寬LTE通道;c) 871 MHz至891 MHz的4個(gè)5 MHz寬W-CDMA通道

小結(jié)

現(xiàn)代無線通信網(wǎng)絡(luò)要求使用靈活、易于升級的多頻段、多標(biāo)準(zhǔn)基站。直接至RF發(fā)射器架構(gòu)為多頻段、多標(biāo)準(zhǔn)無線電發(fā)射器設(shè)計(jì)提供了高性價(jià)比解決方案。RF DAC技術(shù)的發(fā)展(比如ADI的AD9129)有助于降低多頻段和多標(biāo)準(zhǔn)無線電設(shè)計(jì)的門檻,并展現(xiàn)了未來直接至RF架構(gòu)應(yīng)用于更多設(shè)計(jì)的發(fā)展前景。

電子發(fā)燒友App

電子發(fā)燒友App

評論