集成一直是無線通信進步的關鍵,它使設備實現了多功能、小型化。盡管手機處于這些趨勢的前沿,但降低成本、加快上市速度也是促使蜂窩基礎設施實現更高集成度的驅動力。隨著無線集成設計人員力求在更小封裝內集成更多功能,在單一器件內實現模擬、數字和高頻功能等更高水平的集成依舊是IC的主流趨勢。手機和基礎設施設計人員試圖在單個系統內集成多個無線標準的訴求使問題變得更加復雜。為平衡這些不同的需求,創新性設計技術借力放大器、收發器和其它器件的先進技術資源和專業知識,以期創造出不犧牲性能且集成度更高的系統。

Analog Devices(ADI)射頻事業部高級營銷經理Dale Wilson指出,“尺寸作為設計的一個重要的考量標準,在手持和便攜式應用中是尤為突出;而在較大的系統中,對尺寸大小也有要求,客戶希望在一定體積內,實現更多更強的功能。在多數情況下,客戶希望單個設備在擁有多功能的同時,成本能有所下降。此外,他們還希望能夠減少組裝和測試成本、簡化實際設計工作。如果調諧、濾波、偏置等功能都能在芯片上實現,則可以大量減少用戶端的工作量,同樣也可以加快客戶產品的面市時間。分立射頻元件的性能通常比高集成度器件要好。但在許多應用中,只要目標價格得以實現,那么性能‘足夠好’就可以接受。因模擬和高性能射頻器件更多地采用CMOS工藝,也就有更多機會集成數字控制功能。”

為應對這種高集成度的要求,ADI公司傳統上采用先進的雙極型工藝實現其眾多高性能射頻產品。然后,客戶會在其系統內采用數字控制功能。Wilson指出,ADI現正采用最新的BiCMOS工藝,它具有優越的模擬性能以及在芯片中集成數字控制功能的能力。CMOS工藝也被用來實現高度集成的射頻器件,并且采用數字化處理來克服射頻性能局限。

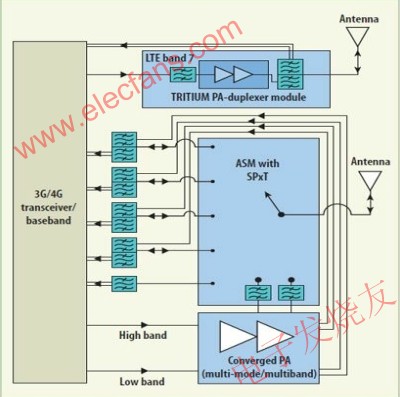

去年秋天,ADI首次推出了支持高密度射頻卡的射頻混頻器和調制器,而且它能提升長期演進(LTE)和第四代(4G)基站(圖1)的容量和速度。ADRF670x系列混頻器和ADRF660x系列調制器可在單一器件內整合多個獨立功能模塊。在4款ADRF660x系列的產品封裝內集成了一個有源射頻混頻器、單端50歐輸入的射頻輸入平衡-非平衡轉換器(balun)、以及一個集成有壓控振蕩器(VCO)的鎖相環(PLL)頻率合成器。該有源混頻器提供6dB的電壓轉換增益。差分IF輸出工作于500MHz。ADRF6601接收混頻器工作在300到2500MHz,內部LO范圍是750到1160MHz。在12dBm輸入功率時,它達到1dB的壓縮并可實現30dBm的輸入三階截點。該混頻器的單邊帶(SSB)噪聲是12dB。

圖1:射頻調制器和下變頻器包含一個集成PLL,它是一個多模N倍頻合成器,支持LTE 100KHz通道光柵。

每款ADRF670x調制器的都在射頻IC內集成了模擬同相/正交(I/Q)調制器、RF輸出開關、帶壓控振蕩器的鎖相環。該調制器輸入帶寬為500MHz。ADRF6701 I/Q調制器的PLL/合成器使用一個N分頻(fractional-N)PLL,它將LO信號倍頻后饋送至I/Q調制器。PLL的參考輸入接受從12MHz到160MHz的信號。調制器的輸出頻率是400至1300MHz。其內部L0頻率范圍是750到1160MHz。該器件在1dB壓縮點和29dBm輸出三階截點條件下,可提供14dBm的輸出功率,并提供158dBm/Hz的噪聲本底。

對PA的集成要求

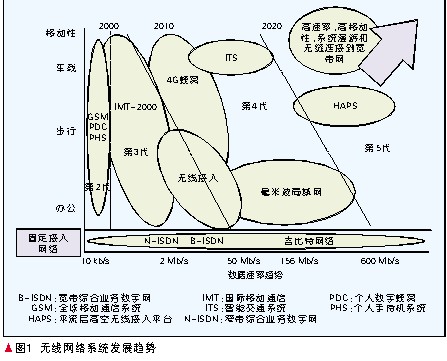

隨著3G無線網絡的完善并逐漸向4G系統過渡,分布式架構和有源天線系統的應用推動著對更小、更高效收發器和PA的需求。例如,美信集成產品(Maxim)公司的MAX9947就承諾可簡化滿足天線接口標準組織(AISG)的基站和塔安裝設備(圖2)的實施。這款尺寸為3x3mm,采用 TQFN形式封裝的單芯片收發器包含了發射器、接收器和有源濾波器。

圖2:收發器集成了帶Autodirection功能的輸出,可用來處理塔安裝設備的總線仲裁而無需MCU。

其中,發射器包括一個OOK調制器、一個符合AISG頻譜輻射規范的帶通濾波器和一個輸出放大器。接收器包括一個中心頻率在2.176MHz、帶寬為200kHz的帶通濾波器。它還包括一個用于重構數字信號的比較器和OOK解調器。在50Ω輸入阻抗條件下,MAX9947具有-15到 +5dBm的輸入動態范圍。其可由電阻調控的輸出功率(7至12dBm)補償了外部電路和線路的損耗。該收發器支持所有的AISG數據速率:9.6、38.4和115.2kb/s。

在PA方面,設計師面臨很高的峰-均值比以及嚴苛的頻譜生長規范的約束。Scintera Networks公司希望能以其SC1887自適應***線***頻域可執行復雜的信號處理。SC1887由標準CMOS工藝制造,采用了該公司的千兆赫茲信號處理技術(GSP)。這種可編程模擬信號處理器(ASP)平臺,力圖降低模擬方案的功耗及實現更小尺寸,而這原本是數字信號處理(DSP)的優勢。SC1887射頻輸入和射頻輸出方案支持獨立于基帶和收發器子系統的模塊化PA設計。SC1887的功耗小于600mW,非常適合低功率發射器。這款SoC覆蓋 698到1000或1800到2800MHz頻段。它支持的輸入信號帶寬可達60MHz、峰均值比為10dB。該芯片可實現將相鄰信道泄漏功率比(ACLR)改善至26dB。

對更高效率的追求,也是Nujira和RF Micro Devices(RFMD)這兩家公司開發PA的動力。這兩家公司稱,無線基礎設施供應商能夠利用它們的PA開發出可滿足世界各種傳輸標準的單一的多模、寬帶射頻前端。其PA設計主要針對4G基站,它集成了RFMD的RFG1M09180 180W氮化鎵(GaN)寬帶功率晶體管與Nujira的Coolteq.h包絡跟蹤功率調制器。僅使用一個RFG1M器件和一個Coolteq.h模塊,這款RFMD Nujira的RF前端就可工作(發射)在728到960MHz頻段。它具有45dBm的平均輸出功率,效率在50%以上。采用RFMD 目前開發的GaN器件,這兩家公司期望只使用三個寬帶PA就能覆蓋700至2600MHz的蜂窩頻率。

通過采用碳納米管作為PA晶體管的散熱材料,Fujitsu Laboratories

使用倒裝芯片結構,碳納米管焊球(bump)經過放大器頂部電極和基板之間。此外,在放大器的背面加裝一個散熱器,這樣,從放大器的兩面都可將熱量帶走。為在高頻獲得高放大倍率,互連至少需10μm長。富士通利用鋁-鐵(Al-Fe)膜將碳納米管延長至20μm,它與板垂直。與傳統方法比,這項新技術有望將散熱效率提高1.5倍。

這項工作凸顯了許多移動通信設計工程師對有效熱管理的關注。東芝(美國)電子元件公司主管微波、射頻和小信號器件的開發經理Homayoun Ghani表示,更高效的設計僅需一個更小的散熱器,這使得在移動系統應用中可采用更小更輕的器件。他指出,“接下來面臨的挑戰主要來自這些小器件產生的熱量,以及如何正確地設計一個有能力處理這些熱量的系統。”Ghani指出,一些系統集成商采用液冷技術。

在蜂窩手機集成化設計過程中,會遇到他們自身的障礙。TriQuint公司負責移動器件的市場營銷高級主管Shane Smith表示,“對于模擬集成,半導體公司正在開發支持多模、多頻段工作的PA。目前,帶EDGE和GMSK調制的五頻段WCDMA需要客戶購買6個PA。 2010-2011年,客戶將只需購買一個PA模塊就可實現相同功能。”

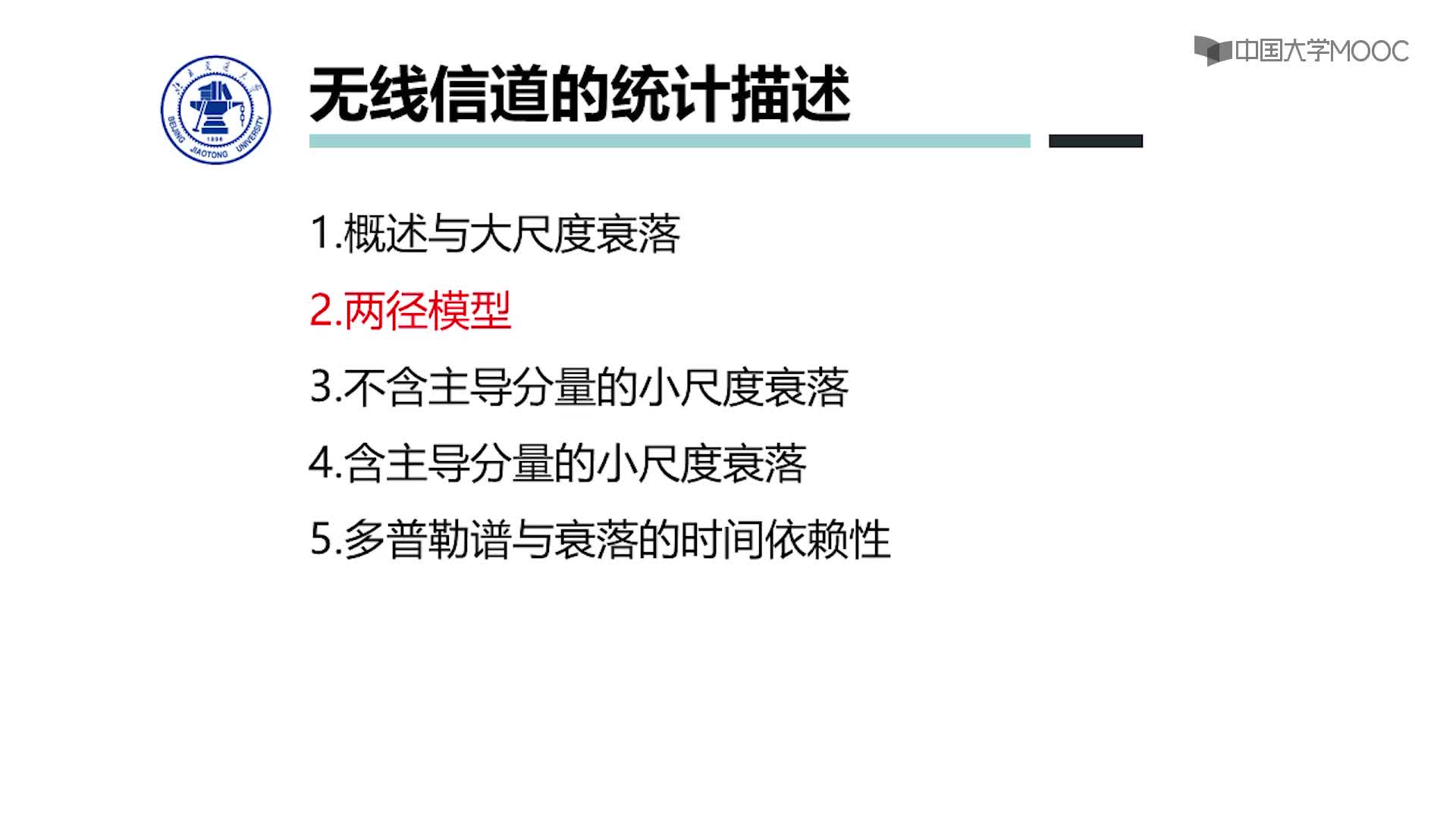

以3G/4G融合手機架構為目標,TriQuint Semiconductor提供TriQuint一體化移動前端架構(TRIUMF,圖3)。該模塊提供了由GSM、EDGE、WCDMA和HSPA組成的射頻功能。與標準多頻段模塊方案比,以這種方式,有望將體積減小50%。通過將4個獨立PA模塊整合在一起,TRIUMF降低了手機組裝成本。由于整合了天線開關、模式/頻段(開關)、開關和雙工器的集成PA模塊會減小前端電路板面積,因而可使射頻系統小型化。

圖3:通過使用集成模塊替代多個分立模塊,手機制造商可以節省大量空間用于功能設計,如Wi-Fi、GPS、藍牙、照相機以及收音機等。

雖然CMOS在具成本效益的整合方面有許多顯著優點,但在手機應用中,CMOS功率放大器一直無法匹敵或超過砷化鎵(GaAs)PA的性能。Javelin Semiconductor的營銷副總裁Patrick Morgan解釋說,“Axiom Microdevices開發出基于分布式有源變換器(DAT)的2G PA架構,DAT是一種模擬技術。ACCO Semiconductor開發出一種用于PA的稱為MASMOS的新晶體管技術。總之,各公司試圖解決CMOS PA的挑戰的方法主要有以下三種:數字信號處理;新型的模擬架構衍生;對標準CMOS工藝流程進行重大變革。”

針對W-CDMA和HSPA無線通信推出的JAV5001 PA,是采用標準CMOS工藝實現的。JAV5001整合了基帶和收發器。在3×3mm封裝內,它集成了功率調節、PA偏置、輸入和輸出匹配以及功率控制電路。JAV5001采用單電源供電。在W-CDMA調制時,其線性輸出功率可達28.0dBm。其增益范圍從5dB(低功率模式)到27dB(高功率模式)。達到2.5kV的人體模式(HBM) 防靜電(ESD)等級。其相鄰信道泄漏功率比(ACLR)的典型值是-40dBc(最大值是-38dBc),偏置是±5MHz。在大功率模式,JAV5001的功率附加效率(PAE)是40%;在中 功率模式,JAV5001的PAE是28%。在 2400到2484MHz,其最大噪聲是 -150dBm/Hz;在RX頻段,噪聲是-147dBm/Hz;偏置是190MHz。

隨著數字電路能處理或支持的高頻功能越來越多,最大的障礙可能在于保持模擬性能。正如TowerJazz的市場營銷及業務拓展總監Ramesh Ramchandani指出的:“力促將數字和模擬功能真正集成于一個芯片內的IC設計人員發現,與單獨模擬芯片比,要想從數字/模擬集成芯片中獲得預期性能是越來越難了。許多工程師在發揮創造力以尋找能彌補模擬性能不理想的電路方案。但是,其中的一個缺點是這里面必須包含一個額外的電路,而且為得到同等性能,可能需要額外增加電容、電阻、電感等無源元件。”這一歷時數十年的困境仍“毫不妥協”:集成非常有必要,但不能以犧牲絲毫性能為代價。

電子發燒友App

電子發燒友App

評論