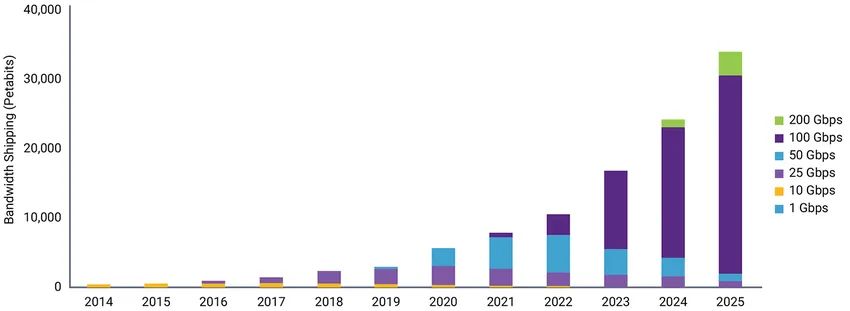

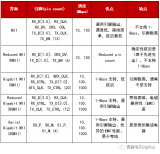

隨著云計算和超大規(guī)模數(shù)據(jù)中心對帶寬網(wǎng)絡(luò)設(shè)備和連通性的要求越來越高,交換機(jī)技術(shù)從 25Tb/s 升級到了 51Tb/s,并很快會達(dá)到 100Tb/s。業(yè)界已選擇以太網(wǎng)來推動交換機(jī)市場,目前采用 112G SerDes 或 PHY 技術(shù),未來將采用 224G SerDes。正如 Arista Network 聯(lián)合創(chuàng)始人兼董事長 Andreas Bechtolsheim 在圖 1 中強(qiáng)調(diào)的那樣,112G SerDes 的部署將在 2025 年達(dá)到峰值。本文介紹了設(shè)計師如何克服設(shè)計挑戰(zhàn)(例如功耗、面積、封裝、信號完整性、電源完整性),以及使用 112G 以太網(wǎng) PHY IP 實現(xiàn) 800G 以太網(wǎng) HPC 系統(tǒng)。

圖 1:交換機(jī)芯片 SerDes 的速度從每通道 100G 提升到 200G

來源:市場焦點(diǎn):通往 800G 及更高速率之路 - Arista Networks

設(shè)計挑戰(zhàn)

面積和功耗

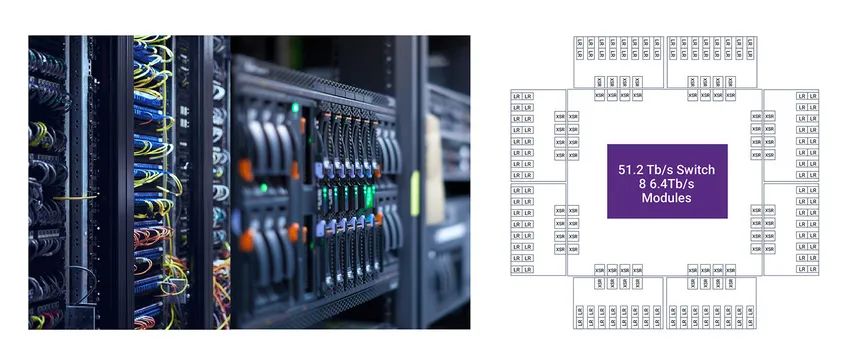

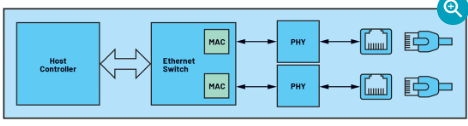

隨著使用更低功率調(diào)制技術(shù)(如PAM-4)和高速 SerDes 技術(shù)(如 112 以太網(wǎng) PHY)的增加,從 7nm 到 5nm 到 3nm 過渡到更先進(jìn)的工藝技術(shù),降低功率和縮減面積成為一個關(guān)鍵焦點(diǎn)。此外,由于良率問題,晶粒尺寸也存在限制。因為服務(wù)器盒和計算盒必須安裝在機(jī)架單元中的同一機(jī)箱中,因此,為了保持相同的大小,以太網(wǎng)交換機(jī)SoC中的組件需要更密集的集成,如圖 2 所示。

圖 2:數(shù)據(jù)中心和 ToR 交換機(jī) SoC 中服務(wù)器機(jī)架的空間限制

然而,SoC 組件的這種密集集成導(dǎo)致功耗增大,并且需要昂貴的冷卻系統(tǒng)。所有這些因素都使得面積、功耗和延遲成為高密度交換機(jī)的關(guān)鍵指標(biāo)或挑戰(zhàn)。它們還會影響性能,因為交換機(jī)的 SoC 包含數(shù)百條通道,使得系統(tǒng)性能比單個 SerDes 性能更重要。

演進(jìn)到共封裝光學(xué)器件

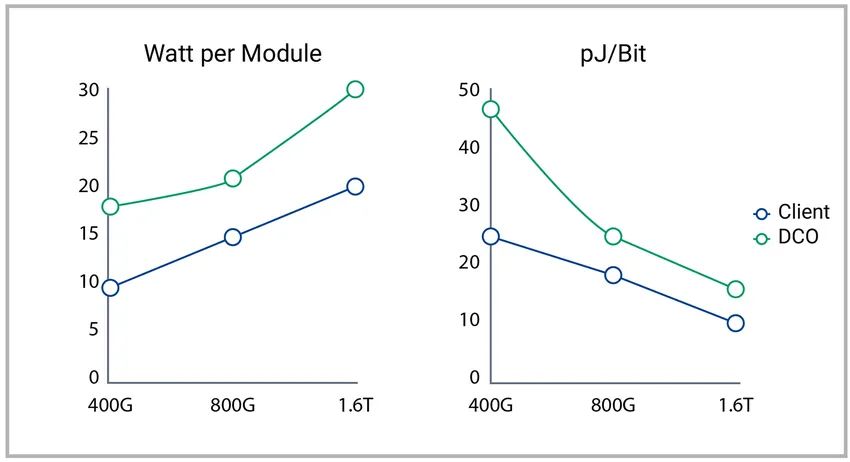

數(shù)據(jù)中心光學(xué)器件也在不斷演變,以支持更高帶寬的網(wǎng)絡(luò)需求。光學(xué)和 ASIC 都必須解決光開關(guān)互連中的面積、功率和延遲問題,并將光開關(guān)的電氣 I/O 功耗降至最低。圖 3 顯示了可插拔光學(xué)電源的演變,這是目前的首選技術(shù)。

圖 3:每比特光學(xué)器件功率顯著下降

資料來源:市場焦點(diǎn):通往 800G 及更高速率之路 - Arista Networks 包括甚短距離 (VSR) 和直接驅(qū)動(無 DSP)在內(nèi)的各種SerDes架構(gòu)正在解決交換機(jī)和光學(xué)模塊中的功耗挑戰(zhàn)。在下一代數(shù)據(jù)中心中,主機(jī)側(cè)具有 VSR PHY 的超高速可插拔光學(xué)器件的功耗將低于中距離或長距離 PHY的功耗。因此,放置在交換機(jī) SoC 附近,與 VSR PHY(消耗 2.5-3 pJ/b)的共封裝光學(xué)器件 (CPO) 的概念正在不斷發(fā)展。目前,CPO 概念的 12Tb/s,25Tb/s 器件已經(jīng)可用,51Tb/s 處于試點(diǎn)階段,預(yù)計很快會達(dá)到 100Tb/s 的批量部署。交換機(jī)接口上的長距離 PHY(無論是共封裝還是直接驅(qū)動光學(xué)組件)也可以通過消除 retimer 來降低功耗。一種新興的 2.5D/3D 硅光子光學(xué)連接技術(shù),它使從高密度可插拔 (OSFP-XD) 到 CPOs 的一系列光模塊成為可能。SerDes IP 提供商持續(xù)關(guān)注生態(tài)系統(tǒng),以繼續(xù)應(yīng)對功耗挑戰(zhàn)。

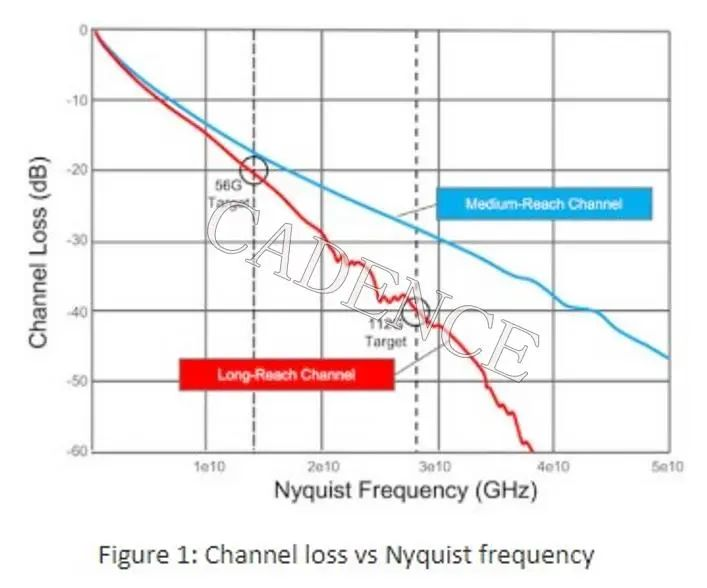

信號完整性

盡量減少影響上市時間的風(fēng)險因素是 SoC 設(shè)計師的關(guān)鍵目標(biāo)。克服系統(tǒng)信號完整性挑戰(zhàn)便是其中的一個風(fēng)險因素。100Gbps 的高速信號彼此之間必須具有最小的串?dāng)_ (xtalk) 影響,同時避開晶粒邊緣。增加封裝層數(shù)是解決方案之一,但會導(dǎo)致成本更高。為了滿足高速 SerDes 串?dāng)_規(guī)格,同時最大限度地減少出線層數(shù)量和外緣尺寸,設(shè)計師必須優(yōu)化通過封裝的高速信號路徑。封裝設(shè)計師和信號完整性專家必須與 SerDes 設(shè)計師一起創(chuàng)建 SerDes 封裝信號位置圖,并進(jìn)行布線研究和高頻仿真以驗證符合串?dāng)_規(guī)格。由于晶粒尺寸限制,51Tb/s 交換機(jī)和 AI 加速器需要將 112G SerDes 或 PHY 放置在所有晶粒邊緣和多個堆疊中。由于信號出線方向不同,因此需要對南北 (N/S)、東西 (E/W) 方向進(jìn)行封裝出線的研究。此外,設(shè)計師需要考慮宏單元的雙重堆疊。此外,還需要考慮附近的功耗和接地平面及其阻抗。

設(shè)計師還必須:

使用不同電源(數(shù)字和模擬)創(chuàng)建多通道 SerDes(51Tb/s 交換機(jī)的 512 通道)的配電網(wǎng)絡(luò) (PDN)

假設(shè)所有物理設(shè)備在任務(wù)模式下同時切換,執(zhí)行電源完整性仿真

驗證電源交流紋波和最大值/最小值。使用 AC PDN 分析和瞬態(tài)仿真來驗證 SerDes 的直流規(guī)格限制

使用 PDN 共享 RL 模型執(zhí)行 PDN 設(shè)計假設(shè)分析

與封裝和 PCB 一起進(jìn)行 IR 壓降分析

保持最低的 PCB 低通濾波器 (LPF) 直流阻抗以及 PDN 直流阻抗

具有有限金屬層的宏單元的多個堆疊可能需要間隔,或者宏單元和數(shù)字邏輯之間的通道可以放置在此類通道/間隔中。SoC 實施者需要提供穩(wěn)定的電源結(jié)構(gòu),并在通道上提供足夠的電源,以盡量減少任何 IR 壓降問題。在設(shè)計階段的早期,對全芯片進(jìn)行的 IR 壓降分析將顯示通道中的任何弱電網(wǎng)。由于 IR 壓降修復(fù)而導(dǎo)致的電源結(jié)構(gòu)和數(shù)字邏輯布局的任何變化都可能影響設(shè)計分區(qū),也可能改變芯片平面布局。因此,早期分析對于減少任何對進(jìn)度的影響是非常重要的。

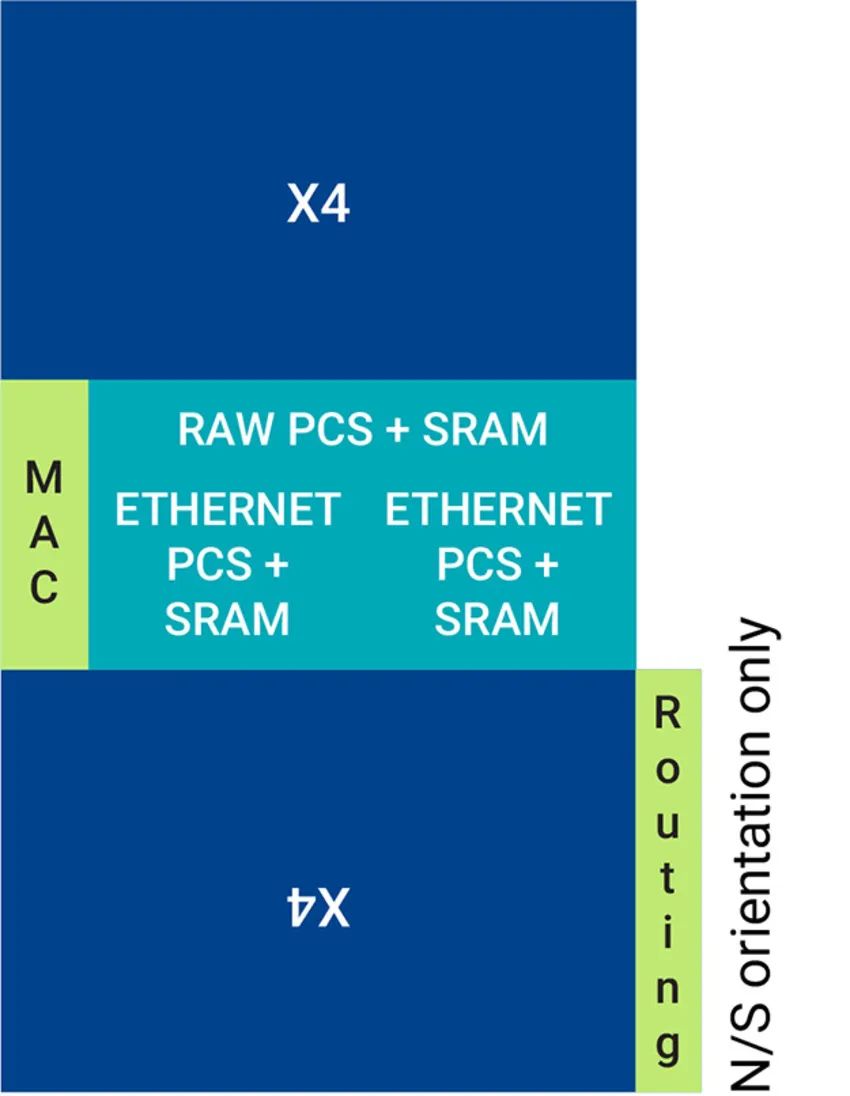

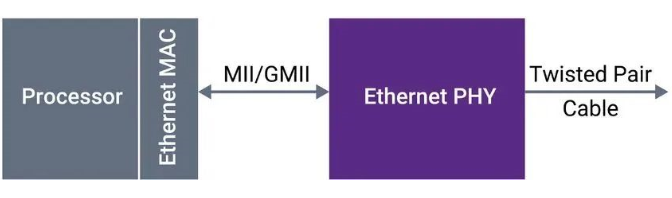

以太網(wǎng) MAC、PCS、PHY 實現(xiàn)

400G 和 800G 以太網(wǎng)的實現(xiàn)需要多個 PCS、MAC 和 PHY。SoC 設(shè)計師可以在考慮晶粒邊緣限制和核心區(qū)域限制后,在有或沒有宏單元堆疊時實現(xiàn)晶粒設(shè)計。這些晶粒塊可以是 N/S 和 E/W 方向,或是與方向無關(guān)的。通過有效的塊分區(qū),可以實現(xiàn)兩個方向的單個晶粒。采用塊分區(qū)和優(yōu)化的單個塊大小的假設(shè)分析可以靈活地重復(fù)使用晶粒所有邊緣周圍的塊。如果在早期設(shè)計階段發(fā)現(xiàn)了時序問題,就可以進(jìn)行設(shè)計改進(jìn),例如在不影響延遲的情況下,如果塊之間相距很遠(yuǎn),就可以進(jìn)行流水線設(shè)計。圖 4 展示了單個 800G 以太網(wǎng)晶粒的實現(xiàn)。

圖 4:可以把 PCS 和 MAC 放置在頂部 X4 宏和底部翻轉(zhuǎn) X4 宏之間的間隙中,以實現(xiàn)靈活的時序收斂

上述實施方式對于南北方向晶粒邊緣上的高速信號的出線可能是行不通的。各種布局的試驗需要數(shù)月的嘗試和問題分析,例如將單個塊放置在所需通道中,并最小化內(nèi)核芯片區(qū)域,都會導(dǎo)致時間延遲。由于多達(dá) 100 個通道設(shè)計和有限的晶粒面積和邊緣長度,具有指定邊界框的自上而下的設(shè)計方法正變得至關(guān)重要。塊式實現(xiàn)可確保所有晶粒邊緣的可重用性和無縫集成。

演進(jìn)之路

? ? 112G SerDes 或 PHY 正在推動云數(shù)據(jù)中心的下一代計算、存儲和網(wǎng)絡(luò)創(chuàng)新,以實現(xiàn)高性能計算和 AI/ML。實現(xiàn) 112G SerDes 或 PHY 技術(shù)的以太網(wǎng)交換機(jī) SoC 設(shè)計師必須考慮一系列關(guān)鍵指標(biāo)或挑戰(zhàn),如電源、面積、延遲、芯片堆疊、信號完整性、電源完整性和實現(xiàn),所有這些都是在設(shè)計師已經(jīng)很短的設(shè)計時間表中增加的任務(wù)。 借助先進(jìn) FinFET 節(jié)點(diǎn)中的經(jīng)過硅驗證的 PAM-4 112G 以太網(wǎng) PHY,以及 PCS、MAC 和先進(jìn) AI/ML 驅(qū)動的 EDA 工具,SoC 設(shè)計師能夠?qū)崿F(xiàn)最佳的功耗、性能、面積和延遲,同時解決系統(tǒng)可靠性、電源完整性和信號完整性問題。 新思科技已完成了所有必要的工作,例如封裝逃逸研究、PHY、SRAM、PCS 和 MAC 布局優(yōu)化,包括分區(qū)和平面圖、引腳布局、位置和路由、時序收斂和電遷移驗證/IR 壓降分析,幫助用戶成功完成例化上百個 112G SerDes 通道的大型 SoC 的定案。新思科技可以通過其邏輯庫、內(nèi)存編譯器、EDA 工具、系統(tǒng)解決方案(如 3DIC)、集成的第三方工具(如 Apache/Redhawk),以及與 PHY、MAC、PCS 設(shè)計師,實現(xiàn)專家和系統(tǒng)專家的密切合作,給客戶提供一個全面的解決方案。也就是說,新思科技可為 112G 以太網(wǎng) PHY、PCS 和 MAC 提供易于集成的交付產(chǎn)品,并提供專家級支持,幫助客戶縮短設(shè)計周期,加快產(chǎn)品上市時間。

電子發(fā)燒友App

電子發(fā)燒友App

評論