實現3nm以下微縮的關鍵技術之一涉及在芯片背面提供功率。這種新穎的方法增強了信號完整性并減少了路由擁塞,但它也帶來了一些新的挑戰,目前還沒有簡單的解決方案。 背面供電 (BPD) 消除了在晶圓正面的信號線和電源線之間共享互連資源的需要。相反,顧名思義,電源被轉移到晶圓背面,因此只有信號由正面互連傳輸。英特爾、三星和臺積電都宣布了在2nm節點附近以某種形式實施 BPD 的計劃。 除了消除RC瓶頸外,BPD還可以節省成本。英特爾高級副總裁兼邏輯技術開發聯席總經理Sanjay Natarajan表示:“背面供電消除了對較低層前端互連的供電軌道的需求。“然后,英特爾可以選擇在不跳過晶體管密度縮放的情況下,在互連縮放方面不那么激進。這允許不太復雜且最終更便宜的下層金屬圖案化。”

它還允許優化制造這些不同的金屬層——作為更寬的 Vdd 和 Vss 線,以及更細的線來傳輸信號。盡管如此,背面電源網絡帶來了巨大的晶圓加工挑戰——特別是因為這種變化可能發生在設備制造商從 finFET 轉向納米片晶體管的同一節點上。 例如,英特爾將在其20A (2nm) 節點引入RibbonFET和PowerVia。“圍繞PowerVia的第一個關鍵挑戰涉及在下一代RibbonFET晶體管周圍的狹小空間內圖案化電接觸特征,同時不影響其性能。第二個是減薄背面硅,以可重復和可控的方式提供盡可能直接和低電阻的連接,”Natarajan說。 由于BPD方法非常新,業界正在權衡不同架構的利弊。

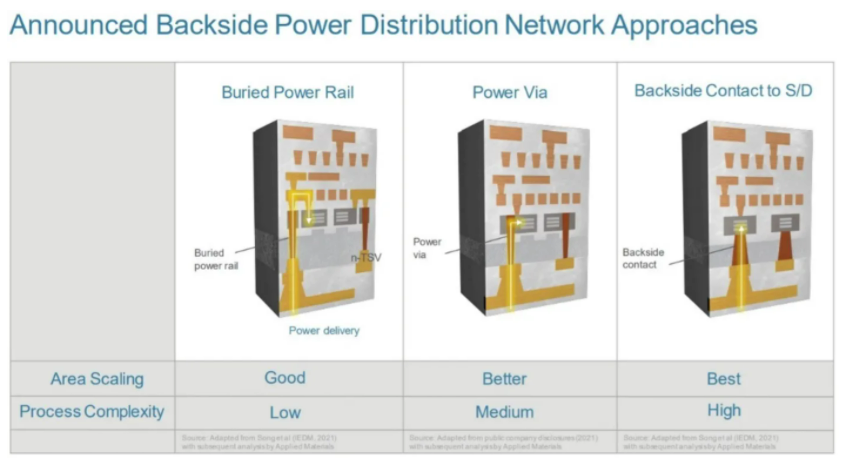

圖 2:BPD方案提供了與晶圓加工復雜性水平增加相關的不同縮放優勢。資料來源:應用材料

BPD方案一下

理想的供電網絡在任何活動期間向 IC 上的有源電路提供恒定、穩定的電源電壓。“關鍵參數是PDN在所有互連路徑中的直流電阻,從IC的電源引腳到電路中的晶體管。”?

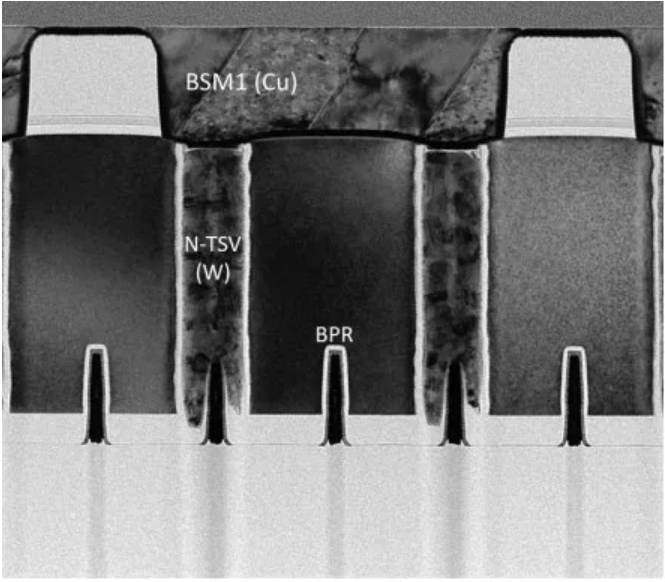

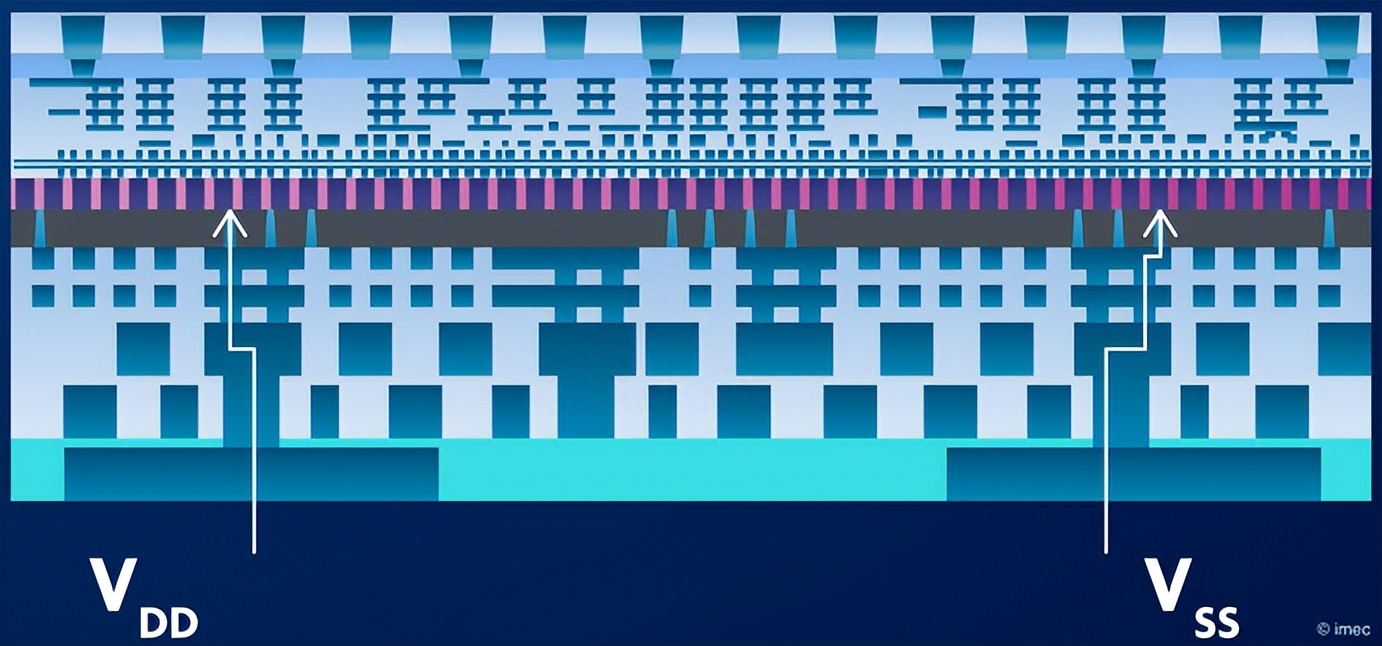

圖2顯示了背面供電網絡的三種實現方式。“在第一種方法中,邏輯單元保留電源軌,背面配電網絡通過納米TSV連接到電源軌,”應用材料公司董事總經理Mehul Naik說。“在第二種方法中,邏輯單元中沒有電源軌。相反,電源通孔直接將電源從背面網絡傳輸到電池或晶體管觸點。這種方法更復雜,但它提高了功率效率并增加了單元面積縮放。在第三種方法中,來自背面網絡的電源直接連接到每個晶體管的源極和漏極。” Imec是最早開發背面供電方法的公司之一,它使用所謂的埋入式電源軌 (BPR)。“如果我們做背面供電網絡,還有埋入式電源軌,從源極/漏極區域有一個通孔,從M0到那個BPR。所以我們有TSV穿過硅并落在掩埋的電源軌上,但是掩埋的電源軌甚至在晶體管制造之前就已經制作好了。它位于柵極形成之前和源極/漏極外延完成之前的納米片鰭片之間,”高級研究員、研發副總裁兼imec 3D系統集成項目總監Eric Beyne解釋道。“這就是銅永遠不會用于此的原因之一。它必須經過所有的前端處理,所以它必須是兼容的——比如鎢或鉬。 將這些構建到制造流程本身就是一個挑戰。“這些電源軌是在您定義鰭片或片材的過程中制造的,這些鰭片之間的空間最大,因為一旦您沉積了環柵和金屬,鰭片更厚,兩個相鄰鰭片之間的間距非常窄,”Beyne說。“所以你必須用更小的特征尺寸制作非常深的通孔。” 他指出,到背面電源軌的短過孔可以位于 BPR 沿線的狹小空間內,從而提供良好的性能優勢。 BPR平行于鰭片方向,部分埋在淺溝槽隔離層中,部分埋在硅襯底中。這與在M0或M1中具有電源軌的傳統電網不同,它可以降低標準單元高度。 Natarajan說:“英特爾的 PowerVia 在背面供電網絡和傳統源觸點之間提供了更直接、單一功能的連接,我們相信與imec方法相比,它可以實現更低的電阻。”

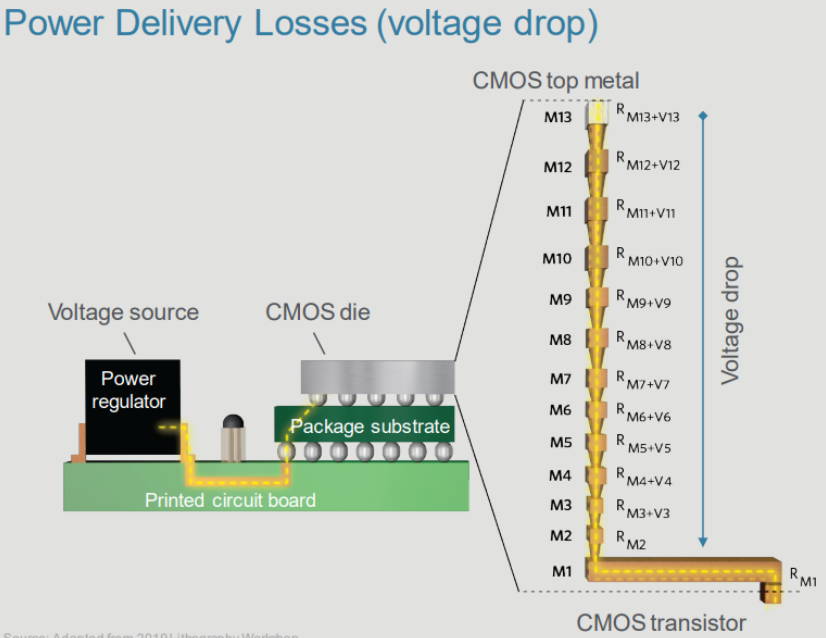

圖 3:供電網絡設計余量允許10%的IR壓降。更高的級別可能會威脅到設備性能。資料來源:應用材料

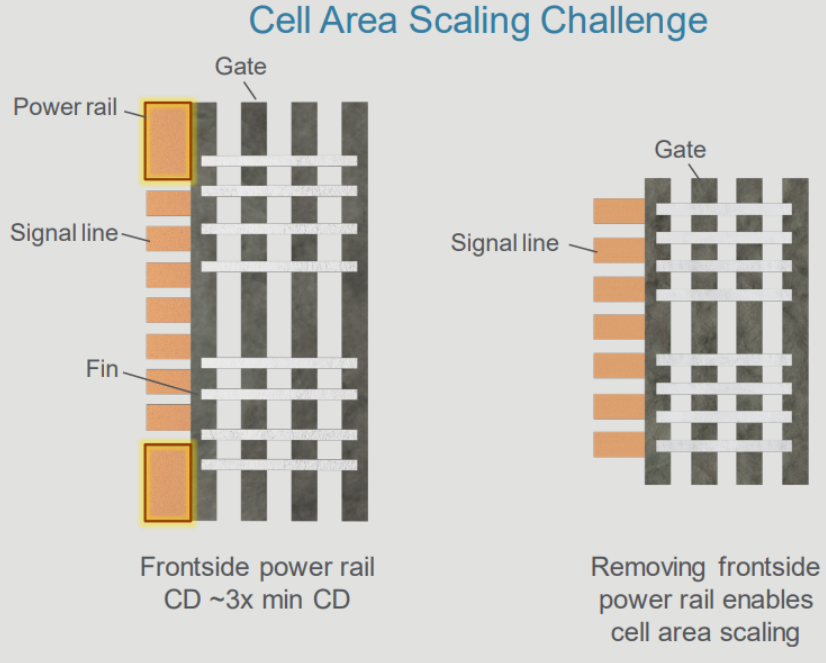

圖 4:通過移動電源軌,標準單元面積可以擴大20%到30%。資料來源:應用材料

為什么是背面供電,為什么是現在?

對向晶體管輸送電力的方式進行這種重大改變的原因與電壓 (IR) 損失有關,即電子必須穿過15層或更多層的互連線和通孔才能向數十億人輸送電力和數據現代SoC中的晶體管數量。[2] 電源效率可以達到90% 的規格限制,或者芯片穩壓器與其晶體管之間的10%電壓 (IR) 損耗(見圖3)。

在背面供電中,電源軌被移出邏輯單元,從而提高了邏輯密度,Applied Materials估計這相當于兩代光刻縮放(見圖4)。由于功率直接從晶體管下方輸送,因此IR壓降大大降低。 Arm和imec進行的模擬和制造研究確定,如果納米TSV之間的距離小于2μm,則背面功率傳輸的效率可以是正面功率傳輸網絡的7倍。 但是必須實現一些工藝和材料的變化才能使BPD在生產工廠中成為現實。“為了更好地利用區域和提高性能,背面供電 (BPD) 網絡是一個有吸引力的選擇。TEL企業創新部設備技術副總裁Tomonari Yamamoto表示:“為了實現它,不僅在薄膜、蝕刻、光刻和濕法,而且在晶圓鍵合和減薄技術方面都需要持續的工藝和工具改進。”事實上,許多較低電阻的金屬正在被評估為替代銅的潛在候選者,隨著BEOL互連CD深入到15nm以下,這將是必要的。

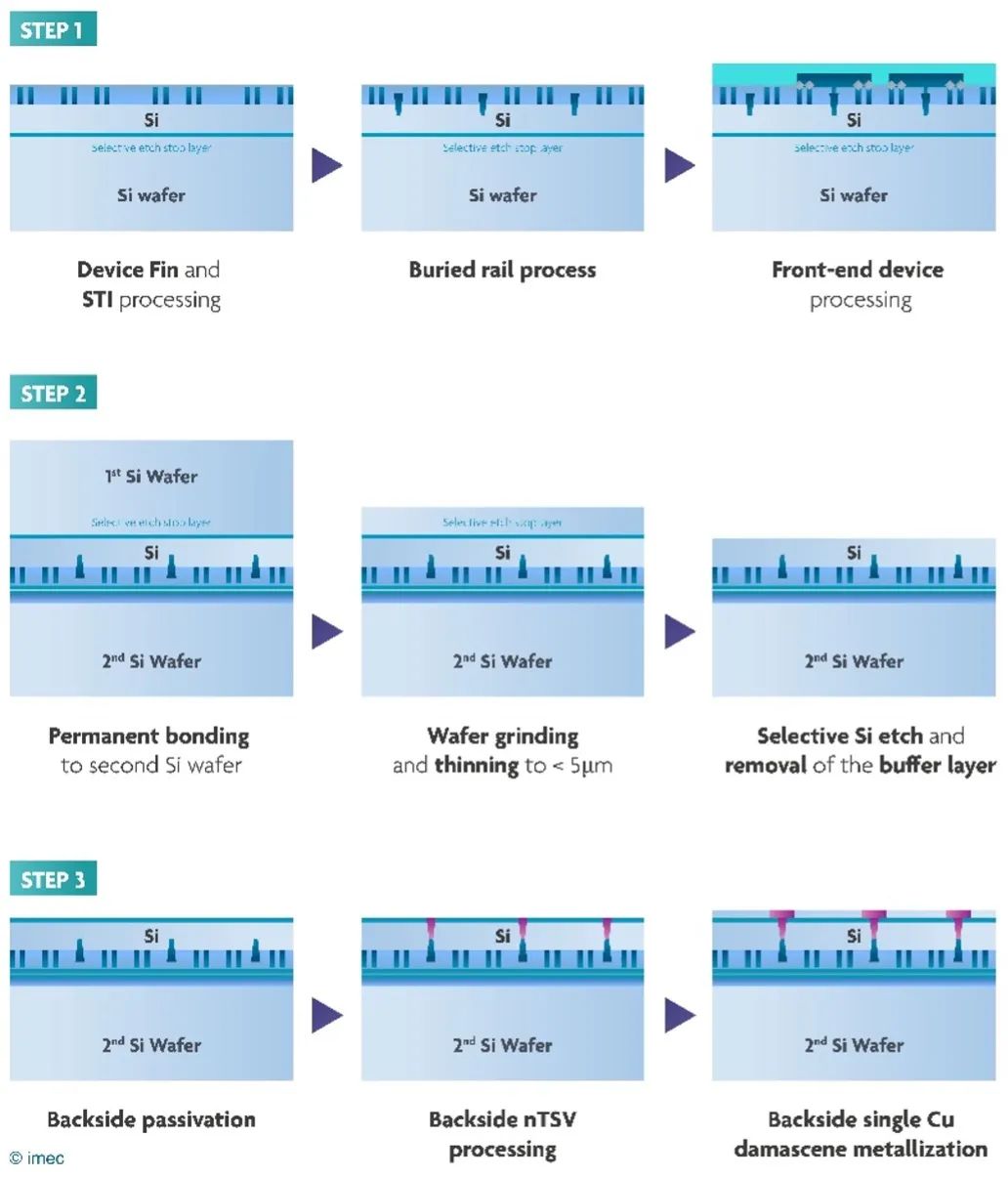

圖 5:背面功率傳輸網絡流程需要在具有350nm硅外延帽的50nm SiGe層上將晶圓極度減薄到<500nm。埋入式釕電源軌的電阻比鎢軌低40%。晶圓鍵合之后是減薄、CMP、干法和濕法蝕刻,然后是TSV和M1形成。資料來源:imec

埋入式電源軌和BPD

imec工藝流程(見圖 5)從SiGe的外延生長開始,然后是硅覆蓋層。高Ge濃度 (25%) 可提高薄膜上CMP停止的選擇性。然后在STI中蝕刻長掩埋的電源軌并延伸到硅中。Imec 比較了鎢和釕CVD薄膜,后者的電阻降低了40%。然后使用SiCN-SiCN電介質鍵合將晶圓永久鍵合到載體晶圓。然后晶圓進行背面研磨和CMP,然后進行干法和濕法蝕刻。通過化學蝕刻去除SiGe。

晶圓鍵合過程必須小心執行,以盡量減少干擾后續圖案化步驟的變形。“當你進行鍵合時,鍵合后圖案很可能會變形,而背面圖案必須糾正這些變形,”Beyne說。“它可能并不多,但即使在1ppm的縮放比例下,溫度甚至不超過1°C,你也會膨脹硅,最終可能會在晶圓邊緣出現150nm的未對準。” 接下來,納米TSV工藝從氧化物沉積 (LPCVD) 開始,然后是自對準DUV圖案化。使用先進的光刻校正方法,將x和y方向上的100nm重疊減少到10nm。博世蝕刻工具創建高AR nanoTSV,落在BPR氧化物和STI 上。接下來,將PECVD氧化物沉積在納米TSV內部,然后對BPR進行濺射蝕刻,以實現納米TSV和BPR之間的良好接觸。TiN ALD之后是W CVD和W CMP。然后銅鑲嵌形成背面金屬(見圖6)。

圖 6:無源測試結構的TEM橫截面顯示帶有90nm 納米TSV的背面銅箔落在掩埋的電源軌上。資料來源:imec Beyne說其他困難的挑戰包括背面圖案化和精確排列電源軌和標準電池尺寸。盡管采用EUV光刻技術的最先進疊加公差約為3nm,但在晶圓背面存在與晶圓鍵合相關的失真問題,疊加公差范圍約為20nm。 “當然,在互連處理、創建高縱橫比尺寸、沉積薄襯墊和無空隙阻擋層等方面,你會遇到所有常見的挑戰,”他說。 重要的是,如果像今天所有晶圓廠一樣首先處理晶體管,那么在2nm節點上就不一定要采用新的互連金屬。事實上,Intel的PowerVia似乎正好允許這樣做。“我們設計的PowerVia工藝與傳統的前端接觸金屬(包括鎢)和先進的金屬工藝兼容,以發揮PowerVia的最佳性能,”Natarajan說。 Naik將背面供電網絡描述為設計技術協同優化 (DTCO) 的一種形式,其中設計和工藝創新可帶來系統級優勢。他強調了在構建背面nanoTSV時存在的熱限制。 “我們需要設計晶體管源極的背面觸點,使其具有盡可能低的電阻,”Naik說。“這通常需要高溫外延和退火工藝。然而,由于背面觸點是在正面晶體管和互連件就位的情況下制造的,因此它們會因這些高溫而退化。為了解決這個問題,Applied正在開發一種低溫解決方案,該解決方案將高真空中的多達七個步驟組合在一起,包括用于預清潔、選擇性硅化物沉積、ALD或PVD襯里沉積以及新金屬填充的腔室。共同優化的CMP步驟留下完美均勻的背面接觸層,我們可以在其上構建銅背面配電網絡。” 提供充分隔離晶體管與電源網絡的沉積薄膜以及接近晶體管有源區域的蝕刻步驟將需要精確的工程設計。Lam Research計算產品副總裁David Fried表示:“在蝕刻中,無論采用哪種工藝流程,您都需要高各向異性、無缺陷和無損傷的結果。”?“在沉積中,一切都與您要沉積的材料參數有關。您需要低缺陷率、高產量以及設計這些材料的能力。” 一旦公司確實過渡到背面供電網絡,重要的是該方法也可以擴展到下一個工藝節點。“我們的標準單元間距是105nm,如果你將nanoTSV連接到每個其他埋入式電源軌,則每210nm就有一個連接——所以200nm線和200nm間距。這與標準單元分離,因此如果你縮小到80納米,它仍然可以工作,而且你不必在背面進行EUV光刻,在這種情況下,”Beyne說。 ?

最小化RC延遲的后續步驟

自22nm器件世代以來,隨著晶體管不斷縮小,BEOL RC延遲已占總器件延遲的更大部分。對于銅鑲嵌方法,無孔銅填充變得越來越具有挑戰性,并且需要超薄潤濕和封蓋CVD工藝改進。

“對于銅,我們可以降低到200納米左右,但你需要一個用于電鍍的銅種子層。對于納米TSV,使用ALD和CVD材料,鎢和其他金屬在高深寬比結構中的縮放效果更好,但您仍然需要TiN阻擋金屬,例如用于鎢。在某些時候,你擁有比塊狀金屬更多的勢壘,比如30納米尺寸,”Beyne說。“鉬對于這些TSV應用中的一些非常有吸引力,因為它是ALD并且它直接沉積在表面上。我想說鎢是當今最常見的材料。改進的選擇包括釕和鉬,但它們仍處于研究階段。”

TEL的山本也有類似的看法。“釕是一個候選材料,因為它對散射不太敏感,不需要厚的阻擋金屬,但只需要一個厚度小于1納米的粘附層。”?他補充說,鑲嵌工藝傾向于提供2的縱橫比,而減法蝕刻方案可實現更高的縱橫比,這將降低電阻,同時可以控制電容的增加,例如,通過用氣隙替換低k薄膜。

結論

優化背面網絡的互連性能與正面網絡的互連性能有些相似——確保背面金屬的低電阻和長期可靠性。然而,Natarajan指出,通過將背面金屬堆疊上的電源布線與正面金屬堆疊上的信號布線分開,工程師可以自由地獨立優化電阻與電容。公司也可能會根據性能需求做出不同的架構選擇,例如雙鑲嵌工藝與減材工藝(金屬沉積和蝕刻)。 領先的設備制造商將在2nm設計中采用背面供電,確保更清潔的供電并打破RC瓶頸。沉積、蝕刻、CMP、鍵合、晶圓減薄和DTCO的綜合進步將影響這個拐點。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論