完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > DDR內(nèi)存

DDR內(nèi)存全稱是DDR SDRAM(Double Data Rate SDRAM,雙倍速率SDRAM)。它是SDRAM 的升級(jí)版本,因此也稱為「SDRAM II」。

DDR SDRAM模塊部分與SDRAM模塊相比,改為采用184針(pin),4~6 層印刷電路板,電氣接口則由「LVTTL」改變?yōu)椤窼STL2」。在其它組件或封裝上則與SDRAM模塊相同。DDR SDRAM模塊一共有184個(gè)接腳,且只有一個(gè)缺槽,與SDRAM的模塊并不兼容。

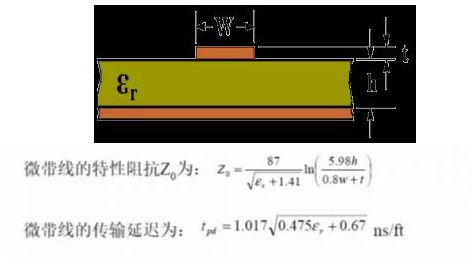

沒有阻抗控制的話,將引發(fā)相當(dāng)大的信號(hào)反射和信號(hào)失真,導(dǎo)致設(shè)計(jì)失敗。常見的信號(hào),如PCI總線、PCI-E總線、USB、以太網(wǎng)、DDR內(nèi)存、LVDS信號(hào)等,...

2023-12-18 標(biāo)簽:lvdsDDR內(nèi)存PCB 784 0

ZYNQ開發(fā)案例之DMA控制器系統(tǒng)設(shè)計(jì)

1. DMA外設(shè)特點(diǎn): 1. DMA引擎擁有一個(gè)靈活的指令設(shè)置DMA的傳輸; 2. 擁有8個(gè)cache線,每一個(gè)cache線寬度是4個(gè)字; 3. 擁有8...

2020-12-05 標(biāo)簽:dmaDDR內(nèi)存 4205 0

嵌入式DDR總線結(jié)構(gòu)介紹及硬件信號(hào)布線分析

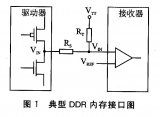

嵌入式DDR(Double Data Rate,雙數(shù)據(jù)速率)設(shè)計(jì)是含DDR的嵌入式硬件設(shè)計(jì)中最重要和最核心的部分。隨著嵌入式系統(tǒng)的處理能力越來越強(qiáng)大,實(shí)...

2018-04-14 標(biāo)簽:嵌入式DDR內(nèi)存 4436 0

用于VR13 CPU VCORE和DDR內(nèi)存的兩相D-CAP+?降壓控制器數(shù)據(jù)表立即下載

類別:電子資料 2024-04-25 標(biāo)簽:降壓控制器DDR內(nèi)存

DDR內(nèi)存布線指導(dǎo),DDR_Layout_Guide_[1]..立即下載

類別:PCB設(shè)計(jì)規(guī)則 2013-04-12 標(biāo)簽:LayoutDDR內(nèi)存

DDR(Double Data Rate)內(nèi)存的頻率與帶寬之間存在緊密的關(guān)系,具體可以從以下幾個(gè)方面進(jìn)行介紹: 一、頻率與帶寬的基本概念 頻率 :DDR...

2024-11-29 標(biāo)簽:帶寬頻率數(shù)據(jù)交換 853 0

DDR內(nèi)存的工作原理 DDR內(nèi)存的常見故障及解決辦法

DDR內(nèi)存的工作原理 DDR(Double Data Rate)內(nèi)存,即雙倍速率同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器,是一種高速的內(nèi)存技術(shù)。它允許在時(shí)鐘周期的上升沿和...

2024-11-29 標(biāo)簽:數(shù)據(jù)傳輸數(shù)據(jù)DDR內(nèi)存 443 0

測(cè)試DDR內(nèi)存的穩(wěn)定性是確保計(jì)算機(jī)系統(tǒng)穩(wěn)定運(yùn)行的重要步驟。以下是一些常用的測(cè)試DDR內(nèi)存穩(wěn)定性的方法: 一、使用專業(yè)測(cè)試軟件 MemTest86 : 功...

2024-11-29 標(biāo)簽:電源計(jì)算機(jī)內(nèi)存 626 0

DDR內(nèi)存與SDRAM的區(qū)別 DDR4內(nèi)存與DDR3內(nèi)存哪個(gè)好

DDR內(nèi)存與SDRAM的區(qū)別 1. 定義與起源 SDRAM (Synchronous Dynamic Random Access Memory) :同步...

2024-11-29 標(biāo)簽:SDRAM存儲(chǔ)器DDR內(nèi)存 697 0

DDR內(nèi)存與數(shù)據(jù)傳輸速度的關(guān)系

在計(jì)算機(jī)系統(tǒng)中,內(nèi)存是至關(guān)重要的組件之一,它直接影響到數(shù)據(jù)的處理速度和系統(tǒng)的響應(yīng)時(shí)間。DDR內(nèi)存作為一種高效的內(nèi)存技術(shù),其數(shù)據(jù)傳輸速度是衡量其性能的關(guān)鍵...

2024-11-20 標(biāo)簽:存儲(chǔ)器數(shù)據(jù)傳輸計(jì)算機(jī)系統(tǒng) 733 0

隨著計(jì)算機(jī)技術(shù)的飛速發(fā)展,內(nèi)存作為計(jì)算機(jī)的核心組件之一,其穩(wěn)定性和可靠性對(duì)整個(gè)系統(tǒng)的運(yùn)行至關(guān)重要。DDR(Double Data Rate)內(nèi)存以其高速...

2024-11-20 標(biāo)簽:計(jì)算機(jī)服務(wù)器硬件 680 0

DDR內(nèi)存,全稱為Double Data Rate Synchronous Dynamic Random Access Memory(雙倍數(shù)據(jù)速率同步動(dòng)...

2024-11-20 標(biāo)簽:數(shù)據(jù)傳輸電子設(shè)備DDR內(nèi)存 597 0

檢測(cè)DDR內(nèi)存性能是一個(gè)涉及硬件和軟件的綜合過程,可以通過以下幾個(gè)步驟來進(jìn)行: 1. 硬件檢查 1.1 確認(rèn)內(nèi)存規(guī)格 查看內(nèi)存條標(biāo)簽 :檢查內(nèi)存條上的標(biāo)...

隨著計(jì)算機(jī)硬件技術(shù)的快速發(fā)展,內(nèi)存的性能越來越受到重視。DDR內(nèi)存作為計(jì)算機(jī)運(yùn)行不可或缺的一部分,其性能直接影響到計(jì)算機(jī)的響應(yīng)速度和數(shù)據(jù)處理能力。超頻,...

2024-11-20 標(biāo)簽:計(jì)算機(jī)硬件超頻 461 0

消息稱三星Q2供應(yīng)超微HBM3E 下半年啟動(dòng)大規(guī)模量產(chǎn)

HBM,即高帶寬內(nèi)存,以其獨(dú)特的“樓房設(shè)計(jì)”概念,打破了傳統(tǒng)DDR內(nèi)存的設(shè)計(jì)局限,憑借出色的性能在市場(chǎng)中贏得了廣泛認(rèn)可。

2024-04-15 標(biāo)簽:DDR內(nèi)存HBM三星 929 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |