摘要

隨著芯片復(fù)雜度的增高和摩爾定律的放緩,半導(dǎo)體行業(yè)正在迅速向先進(jìn)封裝中的異質(zhì)芯片組裝轉(zhuǎn)型。這種轉(zhuǎn)變實(shí)現(xiàn)了通過組件的拆分與新的架構(gòu)配置下的重新集成來持續(xù)縮小線距和創(chuàng)新。然而也帶來了顯著的設(shè)計(jì)、驗(yàn)證、制造和供應(yīng)鏈等方面的挑戰(zhàn)。本文探討了實(shí)現(xiàn)異質(zhì)芯片組裝主流化所涉及的驅(qū)動(dòng)因素、方法、權(quán)衡取舍和未解決問題。

導(dǎo)言

50多年來,摩爾定律推動(dòng)了半導(dǎo)體行業(yè)的發(fā)展,其核心是每兩年單片硅晶圓上的晶體管數(shù)量就會(huì)翻一番。這種堅(jiān)持不懈的縮小線距使芯片可以更高度地集成,性能更強(qiáng),成本更低。但是,隨著芯片制造技術(shù)進(jìn)入10納米以下,繼續(xù)縮小線距的成本高得驚人。此外,單片系統(tǒng)級(jí)芯片(SoC)也遇到了***曝光范圍限制、良率問題和其他瓶頸。因此,行業(yè)正在大力向2.5D和3D堆棧等先進(jìn)封裝中更小的異質(zhì)芯片組裝轉(zhuǎn)變。這種方法通過組合匹配不同工藝節(jié)點(diǎn)和來源的組件,可以繼續(xù)提升芯片的集成度、帶寬、功耗和性能。然而,異質(zhì)集成也給設(shè)計(jì)、驗(yàn)證、制造和供應(yīng)鏈帶來了重大的新挑戰(zhàn)。工程師現(xiàn)在必須協(xié)同設(shè)計(jì)芯片本體、互連和封裝,以實(shí)現(xiàn)系統(tǒng)層面的最佳綜合。本文將探討異質(zhì)芯片組裝主流化的驅(qū)動(dòng)因素、方法、挑戰(zhàn)和展望。

異質(zhì)集成的驅(qū)動(dòng)力

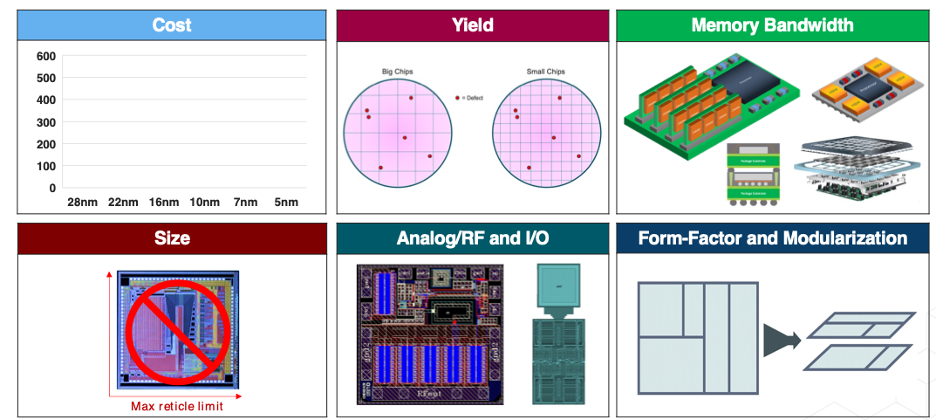

促使行業(yè)向多芯片架構(gòu)轉(zhuǎn)變的幾個(gè)關(guān)鍵因素:

經(jīng)濟(jì)性- 每一代領(lǐng)先工藝節(jié)點(diǎn)的成本呈指數(shù)增長,大多數(shù)芯片市場難以承受。芯片組裝可以混合使用成熟的先進(jìn)工藝。

良率- 更小的芯片具有更高的良率,可降低成本。但單個(gè)故障芯片可能導(dǎo)致整個(gè)封裝失效。

帶寬- 在封裝上集成高帶寬內(nèi)存可獲得巨大的帶寬提升。

定制化- 芯片組裝可以混合不同來源的IP,并在不同產(chǎn)品間重復(fù)利用。

尺寸- 新設(shè)備需要更小、更定制的封裝,而非單片解決方案。

如圖1所示,在摩爾定律放緩的情況下,芯片組裝可提供更好的技術(shù)和經(jīng)濟(jì)路徑。

圖1:采用chiplets的理由。僅依賴摩爾定律不再是最佳路徑。來源:Cadence

異質(zhì)集成方法

連接芯片組裝的兩種主要方法:

2.5D - 芯片并排放置在interposer或載板上。硅中間器可提供高密度互連,有機(jī)載板成本更低。

3D - 芯片垂直堆疊。這節(jié)省空間但會(huì)帶來熱問題。

芯片可以通過線鍵合、微突塊、硅通孔(TSV)以及UCIe、BoW等新興接口標(biāo)準(zhǔn)進(jìn)行連接。

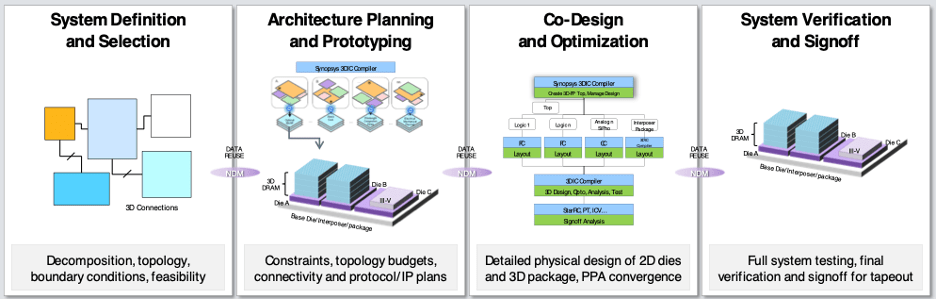

協(xié)同設(shè)計(jì)芯片、封裝和互連,以實(shí)現(xiàn)熱性能、功耗、性能和成本的最佳平衡,難度巨大。工程師必須從整體系統(tǒng)視角出發(fā),而不僅僅是設(shè)計(jì)單獨(dú)的ASIC芯片(圖2)。

圖2:多芯片系統(tǒng)設(shè)計(jì)。來源:Synopsys

關(guān)鍵挑戰(zhàn)

異質(zhì)集成前景廣闊但也帶來許多新挑戰(zhàn):

拆分- 如何在芯片間拆分功能以實(shí)現(xiàn)最佳重用性、功耗、性能和良率?這需要新的架構(gòu)和流程。

互連- 芯片間通信標(biāo)準(zhǔn)仍在形成。在帶寬、功耗和延遲方面存在復(fù)雜的權(quán)衡。

建模- 準(zhǔn)確建模完整的多芯片系統(tǒng)非常困難。需要Digital twins作為“黃金”參考。

噪聲- 與單片解決方案相比,芯片間會(huì)以新方式相互影響。需要廣泛的聯(lián)合仿真。

熱特性- 更多芯片的高密度集成會(huì)帶來必須建模和處理的新熱問題。

應(yīng)力- 薄芯片會(huì)彎曲變形,鍵合/去鍵合也可能損壞脆弱組件。

測試- 測試封裝芯片和裸芯片截然不同。已知良好芯片(KGD)方法很重要。

供應(yīng)鏈- 芯片組裝允許組件重用,但也增加了對(duì)第三方IP/芯片的依賴。

許多標(biāo)準(zhǔn)、工具和方法還在演進(jìn),以實(shí)現(xiàn)可靠的芯片組裝、驗(yàn)證和制造。工程師需要廣泛的新知識(shí),涵蓋多芯片設(shè)計(jì)、系統(tǒng)級(jí)驗(yàn)證、2.5D/3D封裝和測試。

展望

盡管異質(zhì)芯片集成非常復(fù)雜,它在摩爾定律時(shí)代結(jié)束后也可以持續(xù)縮小線距、創(chuàng)新和降低成本。業(yè)界正在大力開發(fā)圍繞封裝、接口標(biāo)準(zhǔn)、設(shè)計(jì)工具、建模、自動(dòng)化和制造的可靠解決方案和生態(tài)系統(tǒng)。

大公司已經(jīng)實(shí)現(xiàn)了多芯片設(shè)計(jì),但廣泛采用將取決于解決方案的成熟和成本降低。最終,基于芯片組裝的架構(gòu)將需要從根本上改變系統(tǒng)的構(gòu)思、設(shè)計(jì)、集成、驗(yàn)證、制造和支持,橫跨全球化的供應(yīng)鏈。這是重大變革,也是半導(dǎo)體行業(yè)一個(gè)激動(dòng)人心的新篇章。

總結(jié)

過去無止境的推進(jìn)摩爾定律縮小線距的結(jié)束,推動(dòng)了向異質(zhì)芯片先進(jìn)封裝的重大轉(zhuǎn)變。這種方法通過組件的混合匹配可以繼續(xù)獲得收益,但也給設(shè)計(jì)和制造流程帶來了重大新挑戰(zhàn)。各方正在積極開發(fā)標(biāo)準(zhǔn)、工具、方法、測試、供應(yīng)鏈等,以實(shí)現(xiàn)異質(zhì)集成的大規(guī)模應(yīng)用,將從根本上改變半導(dǎo)體行業(yè)的經(jīng)濟(jì)模式和實(shí)踐方式。

來源:逍遙設(shè)計(jì)自動(dòng)化

-

芯片

+關(guān)注

關(guān)注

455文章

50851瀏覽量

423886 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27390瀏覽量

219025 -

晶圓

+關(guān)注

關(guān)注

52文章

4917瀏覽量

128018 -

soc

+關(guān)注

關(guān)注

38文章

4169瀏覽量

218330

原文標(biāo)題:【光電集成】異質(zhì)芯片集成的發(fā)展

文章出處:【微信號(hào):今日光電,微信公眾號(hào):今日光電】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電腦主板芯片組的介紹

威盛 芯片組HyperionPro驅(qū)動(dòng)5.23

柔性電路板上倒裝芯片組裝技巧

芯片組是什么_芯片組驅(qū)動(dòng)是什么

芯片組驅(qū)動(dòng)不裝有什么影響_如何安裝芯片組驅(qū)動(dòng)程序

芯片組驅(qū)動(dòng)要不要更新_芯片組驅(qū)動(dòng)卸載了會(huì)怎么樣

快速成熟的智能照明市場有哪些驅(qū)動(dòng)因素

闡述芯片組與芯片組驅(qū)動(dòng)功能和發(fā)展

芯片組與芯片組驅(qū)動(dòng)功能的介紹和發(fā)展說明

影響可穿戴診斷設(shè)備發(fā)展的市場驅(qū)動(dòng)因素

了解風(fēng)門執(zhí)行器以及汽車HVAC系統(tǒng)中它們的驅(qū)動(dòng)因素

電子燈鎮(zhèn)流器IGBT門驅(qū)動(dòng)因素

剛性電路板的9個(gè)成本驅(qū)動(dòng)因素

異質(zhì)芯片組裝主流化的驅(qū)動(dòng)因素和方法

異質(zhì)芯片組裝主流化的驅(qū)動(dòng)因素和方法

評(píng)論