資料介紹

軟件無(wú)線電的出現(xiàn),是無(wú)線電通信從模擬到數(shù)字、從固定到移動(dòng)后,由硬件到軟件的第三次變革。簡(jiǎn)單地說(shuō),軟件無(wú)線電就是一種基于通用硬件平臺(tái),并通 過(guò)軟件可提供多種服務(wù)的、適應(yīng)多種標(biāo)準(zhǔn)的、多頻帶多模式的、可重構(gòu)可編程的無(wú)線電系統(tǒng)。軟件無(wú)線電的關(guān)鍵思想是,將AD(DA)盡可能靠近天線和用軟件來(lái) 完成盡可能多的無(wú)線電功能。

蜂窩移動(dòng)通信系統(tǒng)已經(jīng)發(fā)展到第三代,3G系統(tǒng)進(jìn)入商業(yè)運(yùn)行一方面需要解決不同標(biāo)準(zhǔn)的系統(tǒng)間的兼容性;另一方 面要求系統(tǒng)具有高度的靈活性和擴(kuò)展升級(jí)能力,軟件無(wú)線電技術(shù)無(wú)疑是最好的解決方案。用ASIC(Application Specific Intergrated CIRcuits)和DSP(Digital Singnal Processor)芯片搭建軟件無(wú)線電平臺(tái)是目前系統(tǒng)設(shè)計(jì)的主要方法,這種方法有兩個(gè)突出缺點(diǎn):一是系統(tǒng)速度跟不上高速動(dòng)態(tài)實(shí)時(shí)數(shù)字信號(hào)處理, 二是系統(tǒng)體積大功耗高。這兩個(gè)突出缺點(diǎn)制約了軟件無(wú)線電在高速實(shí)時(shí)通信領(lǐng)域的應(yīng)用前景。本文運(yùn)用目前基于FPGA(Field Programmable Gate Array)的SoPC (System on Programmable Chip)技術(shù)構(gòu)建軟件無(wú)線電平臺(tái)。大大提高了數(shù)字信號(hào)處理的能力和速度,并且降低了系統(tǒng)功耗,縮小了系統(tǒng)體積,為更高層次的3G無(wú)線通信要求提供了解決方案。

1 無(wú)線通信系統(tǒng)設(shè)計(jì)

1.1 系統(tǒng)設(shè)計(jì)

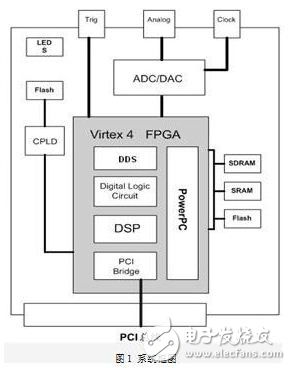

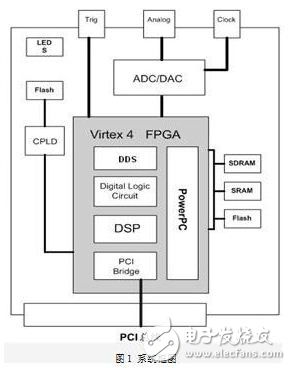

軟件無(wú)線電使得無(wú)線電具有更多的個(gè)性化特點(diǎn),它以軟件方式定義多個(gè)頻段及多種調(diào)制波形接口。軟件無(wú)線電系統(tǒng)包括信號(hào)發(fā)射和接收兩部分,本文重點(diǎn)以接收流 程進(jìn)行論述。軟件無(wú)線電的RF(Radio Frequency)部分是一個(gè)多波束天線陣,可同時(shí)接收多個(gè)頻段、多個(gè)方向的射頻信號(hào),并將射頻轉(zhuǎn)換為中頻信號(hào)。如圖1所示,系統(tǒng)中包括Virtex- 4 FX系列FPGA,模擬信號(hào)輸入端口,同步觸發(fā)端口,外接時(shí)鐘源,F(xiàn)lash(加載FPGA配置程序),CPLD,SDRAM,PCI接口,LED信號(hào)燈等部分。

提取用戶窄帶信號(hào)進(jìn)行抽取由專用ADC芯片完成,數(shù)字下變頻部分由FPGA中的IP(Intellectual Property)模塊完成。用專用芯片進(jìn)行模數(shù)轉(zhuǎn)換可以提高系統(tǒng)的穩(wěn)定性和可靠性;用IP模塊完成數(shù)字下變頻功能可以降低功耗,提高速率。

數(shù)字下變頻后進(jìn)行解調(diào),經(jīng)過(guò)解調(diào)后的信號(hào)為一個(gè)比特流序列,比特流處理部分需要完成信息的加密解密、編碼譯碼等。如圖1所示,這部分功能可以用 Verilog-HDL語(yǔ)言編寫(xiě)DSP處理模塊完成,也可以用Matlab的FDATool進(jìn)行設(shè)計(jì)后自動(dòng)生成Verilog-HDL源代碼和 PowerPC指令程序;本文采用Verilog-HDL直接編寫(xiě)DSP模塊的辦法,這樣可以對(duì)硬件處理流程進(jìn)行更好的掌控,并且獲得更高的信號(hào)處理性 能。由于將DSP模塊嵌入FPGA中,通過(guò)增加或減少DSP邏輯電路可以使得設(shè)計(jì)更加靈活,例如可以將2FSK調(diào)制解調(diào),F(xiàn)IR濾波和FFT分別封裝成為 單元模塊,編寫(xiě)地址驅(qū)動(dòng)后PowerPC程序執(zhí)行時(shí)可直接進(jìn)行調(diào)用,相比DSP專用處理器僅調(diào)用乘法器和移位寄存器的方法可以節(jié)省上百個(gè)指令周期,大大提 高了實(shí)時(shí)信號(hào)處理的能力,具有在高端領(lǐng)域廣闊的應(yīng)用前景。

比特流序列處理完成后,可將數(shù)據(jù)傳入主機(jī)磁盤(pán)陣列經(jīng)行儲(chǔ)存,PowerPC通過(guò)PCI橋控制本系統(tǒng)和主機(jī)的數(shù)據(jù)傳輸,以滿足未來(lái)數(shù)據(jù)回放和可視化界面要求。

1.2 ADC模數(shù)轉(zhuǎn)換

軟件無(wú)線電要求ADC,DAC盡可能的靠近天線,這需要很高的ADC的采樣率,采樣精度,動(dòng)態(tài)范圍等特征。AD9042是一款高性能高速ADC芯片,采 用的是兩級(jí)子區(qū)式轉(zhuǎn)換結(jié)構(gòu),這種設(shè)計(jì)既保證了所需的轉(zhuǎn)換精度和轉(zhuǎn)換速度,又降低了功耗,同時(shí)也減小了芯片尺寸,AD9042系統(tǒng)原理如圖2所示。 AD9042可以保證的最小采樣率可達(dá)41MHZ, 12bit精度,80dB無(wú)寄生動(dòng)態(tài)范圍。

蜂窩移動(dòng)通信系統(tǒng)已經(jīng)發(fā)展到第三代,3G系統(tǒng)進(jìn)入商業(yè)運(yùn)行一方面需要解決不同標(biāo)準(zhǔn)的系統(tǒng)間的兼容性;另一方 面要求系統(tǒng)具有高度的靈活性和擴(kuò)展升級(jí)能力,軟件無(wú)線電技術(shù)無(wú)疑是最好的解決方案。用ASIC(Application Specific Intergrated CIRcuits)和DSP(Digital Singnal Processor)芯片搭建軟件無(wú)線電平臺(tái)是目前系統(tǒng)設(shè)計(jì)的主要方法,這種方法有兩個(gè)突出缺點(diǎn):一是系統(tǒng)速度跟不上高速動(dòng)態(tài)實(shí)時(shí)數(shù)字信號(hào)處理, 二是系統(tǒng)體積大功耗高。這兩個(gè)突出缺點(diǎn)制約了軟件無(wú)線電在高速實(shí)時(shí)通信領(lǐng)域的應(yīng)用前景。本文運(yùn)用目前基于FPGA(Field Programmable Gate Array)的SoPC (System on Programmable Chip)技術(shù)構(gòu)建軟件無(wú)線電平臺(tái)。大大提高了數(shù)字信號(hào)處理的能力和速度,并且降低了系統(tǒng)功耗,縮小了系統(tǒng)體積,為更高層次的3G無(wú)線通信要求提供了解決方案。

1 無(wú)線通信系統(tǒng)設(shè)計(jì)

1.1 系統(tǒng)設(shè)計(jì)

軟件無(wú)線電使得無(wú)線電具有更多的個(gè)性化特點(diǎn),它以軟件方式定義多個(gè)頻段及多種調(diào)制波形接口。軟件無(wú)線電系統(tǒng)包括信號(hào)發(fā)射和接收兩部分,本文重點(diǎn)以接收流 程進(jìn)行論述。軟件無(wú)線電的RF(Radio Frequency)部分是一個(gè)多波束天線陣,可同時(shí)接收多個(gè)頻段、多個(gè)方向的射頻信號(hào),并將射頻轉(zhuǎn)換為中頻信號(hào)。如圖1所示,系統(tǒng)中包括Virtex- 4 FX系列FPGA,模擬信號(hào)輸入端口,同步觸發(fā)端口,外接時(shí)鐘源,F(xiàn)lash(加載FPGA配置程序),CPLD,SDRAM,PCI接口,LED信號(hào)燈等部分。

提取用戶窄帶信號(hào)進(jìn)行抽取由專用ADC芯片完成,數(shù)字下變頻部分由FPGA中的IP(Intellectual Property)模塊完成。用專用芯片進(jìn)行模數(shù)轉(zhuǎn)換可以提高系統(tǒng)的穩(wěn)定性和可靠性;用IP模塊完成數(shù)字下變頻功能可以降低功耗,提高速率。

數(shù)字下變頻后進(jìn)行解調(diào),經(jīng)過(guò)解調(diào)后的信號(hào)為一個(gè)比特流序列,比特流處理部分需要完成信息的加密解密、編碼譯碼等。如圖1所示,這部分功能可以用 Verilog-HDL語(yǔ)言編寫(xiě)DSP處理模塊完成,也可以用Matlab的FDATool進(jìn)行設(shè)計(jì)后自動(dòng)生成Verilog-HDL源代碼和 PowerPC指令程序;本文采用Verilog-HDL直接編寫(xiě)DSP模塊的辦法,這樣可以對(duì)硬件處理流程進(jìn)行更好的掌控,并且獲得更高的信號(hào)處理性 能。由于將DSP模塊嵌入FPGA中,通過(guò)增加或減少DSP邏輯電路可以使得設(shè)計(jì)更加靈活,例如可以將2FSK調(diào)制解調(diào),F(xiàn)IR濾波和FFT分別封裝成為 單元模塊,編寫(xiě)地址驅(qū)動(dòng)后PowerPC程序執(zhí)行時(shí)可直接進(jìn)行調(diào)用,相比DSP專用處理器僅調(diào)用乘法器和移位寄存器的方法可以節(jié)省上百個(gè)指令周期,大大提 高了實(shí)時(shí)信號(hào)處理的能力,具有在高端領(lǐng)域廣闊的應(yīng)用前景。

比特流序列處理完成后,可將數(shù)據(jù)傳入主機(jī)磁盤(pán)陣列經(jīng)行儲(chǔ)存,PowerPC通過(guò)PCI橋控制本系統(tǒng)和主機(jī)的數(shù)據(jù)傳輸,以滿足未來(lái)數(shù)據(jù)回放和可視化界面要求。

1.2 ADC模數(shù)轉(zhuǎn)換

軟件無(wú)線電要求ADC,DAC盡可能的靠近天線,這需要很高的ADC的采樣率,采樣精度,動(dòng)態(tài)范圍等特征。AD9042是一款高性能高速ADC芯片,采 用的是兩級(jí)子區(qū)式轉(zhuǎn)換結(jié)構(gòu),這種設(shè)計(jì)既保證了所需的轉(zhuǎn)換精度和轉(zhuǎn)換速度,又降低了功耗,同時(shí)也減小了芯片尺寸,AD9042系統(tǒng)原理如圖2所示。 AD9042可以保證的最小采樣率可達(dá)41MHZ, 12bit精度,80dB無(wú)寄生動(dòng)態(tài)范圍。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 解析無(wú)線電偽碼測(cè)目標(biāo)距離系統(tǒng)的設(shè)計(jì) 0次下載

- 軟件無(wú)線電基礎(chǔ) 50次下載

- GNU Radio:開(kāi)放的軟件無(wú)線電平臺(tái) 10次下載

- 軟件無(wú)線電RFID測(cè)試平臺(tái)課件下載 32次下載

- 如何使用軟件無(wú)線電實(shí)現(xiàn)OFDM系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn) 11次下載

- 如何使用FPGA實(shí)現(xiàn)軟件無(wú)線電平臺(tái)的設(shè)計(jì)

- SORA軟件無(wú)線電平臺(tái)的介紹和使用說(shuō)明

- 如何實(shí)現(xiàn)軟件無(wú)線電臺(tái)的組網(wǎng)方案設(shè)計(jì) 13次下載

- 如何實(shí)現(xiàn)一種低功耗軟件無(wú)線電信號(hào)處理平臺(tái) 3次下載

- 如何使用軟件無(wú)線電實(shí)現(xiàn)QDPSK調(diào)制解調(diào)算法的硬件 6次下載

- USRP軟件無(wú)線電平臺(tái)的產(chǎn)品說(shuō)明資料免費(fèi)下載 9次下載

- 軟件無(wú)線電設(shè)計(jì)中ASIC、FPGA和DSP的重要準(zhǔn)則 1次下載

- DSP軟件無(wú)線電平臺(tái)系統(tǒng)設(shè)計(jì)方案 0次下載

- 基于FPGA的軟件無(wú)線電通信平臺(tái) 93次下載

- 實(shí)現(xiàn)軟件定義無(wú)線電和認(rèn)知無(wú)線電的自適應(yīng)特性

- 基于濾波器和混頻器實(shí)現(xiàn)軟件無(wú)線電的應(yīng)用設(shè)計(jì)方案 1852次閱讀

- 基于TigerSHARC201和FPGA實(shí)現(xiàn)軟件無(wú)線電平臺(tái)的設(shè)計(jì) 2187次閱讀

- 基于Xilinx Virtex6 FPGA的通用軟件無(wú)線電平臺(tái)設(shè)計(jì) 1498次閱讀

- 基于新型Virtex FPGA實(shí)現(xiàn)小型軟件無(wú)線電平臺(tái)SFF SDR設(shè)計(jì) 1205次閱讀

- 軟件無(wú)線電硬件平臺(tái)的FPGA動(dòng)態(tài)配置 1045次閱讀

- 基于搭建一種具有優(yōu)秀可移植性的高性能通用軟件無(wú)線電平臺(tái)的目的 4165次閱讀

- 軟件無(wú)線電架構(gòu)的詳細(xì)概述 1.6w次閱讀

- 以軟件無(wú)線電為核心的在FPGA基礎(chǔ)上的DQPSK調(diào)制解調(diào)系統(tǒng)設(shè)計(jì)方案詳解 4350次閱讀

- 基于FPGA的軟件無(wú)線電平臺(tái)設(shè)計(jì)詳細(xì)教程 3411次閱讀

- 最新小型軟件無(wú)線電平臺(tái)SFF SDR介紹 2699次閱讀

- 基于FPGA的通用軟件無(wú)線電平臺(tái)設(shè)計(jì) 3556次閱讀

- 采用軟件定義無(wú)線電開(kāi)發(fā)RFID測(cè)試平臺(tái) 814次閱讀

- 基于雙緩沖與單緩沖比較總線設(shè)計(jì)方案 1406次閱讀

- 基于軟件無(wú)線電中頻接收系統(tǒng)的設(shè)計(jì)方案 2834次閱讀

- 基于FPGA的數(shù)字核脈沖分析器硬件設(shè)計(jì)方案 2078次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1491次下載 | 免費(fèi)

- 2單片機(jī)典型實(shí)例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識(shí)別和講解說(shuō)明

- 4.28 MB | 18次下載 | 4 積分

- 5開(kāi)關(guān)電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費(fèi)

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機(jī)和 SG3525的程控開(kāi)關(guān)電源設(shè)計(jì)

- 0.23 MB | 4次下載 | 免費(fèi)

- 8基于AT89C2051/4051單片機(jī)編程器的實(shí)驗(yàn)

- 0.11 MB | 4次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33562次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開(kāi)關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21539次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537793次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183277次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問(wèn)

提問(wèn)  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論