電子發(fā)燒友網(wǎng)核心提示 :本文介紹了最新的Xilinx Zynq-7000 FPGA開發(fā)板 Zedboard 。Zedboard是基于Xilinx Zynq-7000擴展式處理平臺(EPP)的低成本開發(fā)板,也是行業(yè)首個面向開源社區(qū)的Zynq-7000擴展

2012-11-26 15:09:01 55135

55135 電子發(fā)燒友網(wǎng)編輯現(xiàn)為讀者整合《玩轉(zhuǎn)賽靈思Zedboard開發(fā)板》系列文章, 其中包括在ZedBoard開發(fā)板上的一些應(yīng)用實例。本文主要講述Zedboard上的嵌入式linux應(yīng)用,包括使用SDK設(shè)計最簡單的linux應(yīng)用程序、linux交叉編譯環(huán)境搭建、設(shè)備驅(qū)動編寫等內(nèi)容...

2013-01-24 13:38:18 16892

16892 Helo人,我一直在使用Zedboard進行一些項目。我的USB_UART適配器與電路板斷開連接,無法再次連接。我聯(lián)系了Xilinx和Digilent,但根據(jù)它們無法修復(fù)。現(xiàn)在有一個解決方案是買一個

2020-04-02 07:00:45

在Zedboard上實現(xiàn)了Linux,接下來我們就可以像其他的嵌入式linux開發(fā)一樣來使用Zedboard了。SDK提供了標(biāo)準(zhǔn)可視化的linux-arm交叉編譯鏈,不需要再進行交叉編譯環(huán)境的搭建

2018-06-28 11:10:51

Hiteam,我有一個zedboard和vivado 13.4許可證。一切都很好,我已經(jīng)成功實現(xiàn)了一些設(shè)計我調(diào)查了adau1761 ADC并試圖通過logico axi4lite spdif來提供它

2018-12-10 10:29:01

你好我已經(jīng)在zedboard上成功開發(fā)了SD / MMC驅(qū)動程序,我的海量存儲應(yīng)用程序運行正常。 zedboard是否支持SDIO?我正在為AR6K3無線驅(qū)動程序工作。在開發(fā)SDIO驅(qū)動程序時,當(dāng)我

2019-03-14 07:59:03

大家好我用的是zedboard開發(fā)板,現(xiàn)在我有一個60M的數(shù)據(jù)需要處理,全部為十進制整形,每個數(shù)據(jù)長度至少8位,目前嘗試先放入SD卡,但讀取出現(xiàn)了問題,我用的是xilinx SDK提供的庫函數(shù)

2016-05-25 10:26:07

本人學(xué)生,在實驗室打算做EMD算法的硬件實現(xiàn),看了一些論文,感覺主要是單獨用FPGA實現(xiàn),或者用DSP+FPGA實現(xiàn)(DSP做EMD算法,F(xiàn)PGA做數(shù)據(jù)流控制),請問大家用哪種架構(gòu)做硬件實現(xiàn)EMD算法比較好?

2018-04-25 21:04:33

硬件控制算法可應(yīng)用的電路系統(tǒng)一般由模擬電路和數(shù)字電路組成。模擬電路用于電信號的處理和提供電源;數(shù)字電路則用于采集非電信號數(shù)據(jù)和控制系統(tǒng)。一般來說系統(tǒng)控制使用MCU、DSP或FPGA通過軟件編程實現(xiàn)

2021-09-01 08:05:42

C語言實現(xiàn)數(shù)字信號處理算法

2012-08-16 23:17:38

FPGA實現(xiàn)的 FFT 處理器的硬件結(jié)構(gòu)。接收單元采用乒乓RAM 結(jié)構(gòu), 擴大了數(shù)據(jù)吞吐量。中間數(shù)據(jù)緩存單元采用雙口RAM , 減少了訪問RAM 的時鐘消耗。計算單元采用基 2 算法, 流水線結(jié)構(gòu), 可在

2017-11-21 15:55:13

我試圖將ov7670相機與zedboard接口。我已經(jīng)使用了倉鼠代碼。但是當(dāng)合成和實現(xiàn)獲得大量的關(guān)鍵警告時,忽略是否安全?我的比特流也沒有產(chǎn)生它的顯示錯誤。我正在接受我所做的一切。請幫忙

2018-10-30 18:04:23

現(xiàn)想用如圖算法實現(xiàn)2700個CCD像元值的平滑處理,不知道用labview怎么實現(xiàn),求助各位大神

2016-11-24 17:16:45

實現(xiàn)了一種I/O流水線接口,該接口具有I/O連接加速器的典型性能。FPGA/PowerPC/APU接口FPGA允許硬件設(shè)計工程師利用單芯片上的處理器、解碼邏輯、外設(shè)和協(xié)處理器實現(xiàn)一個完整的計算系統(tǒng)

2015-02-02 14:18:19

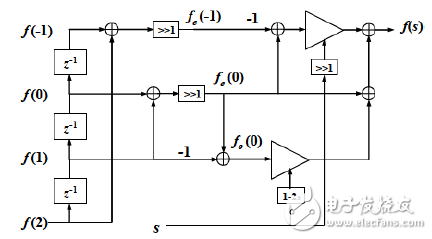

了大量的算術(shù)運算,而且計算中像素相關(guān)性的要求需要存儲大量像素,所以硬件實現(xiàn)必須適當(dāng)減少硬件資源和RAM的使用量,從而降低ASIC的面積,本文提出如下的解決方法。4.1 流水線式的運算處理由式(1)、式

2019-07-17 04:00:00

自行命名它,然后點選“一鍵燒錄”, 即可將固件欄中加載的固件按照填好的地址燒錄入脫機燒錄器中。

隨后點擊“退出配置”即可退出FlashLoader狀態(tài),就可以單獨使用脫機燒錄器給開發(fā)板燒錄程序了

2023-04-28 20:32:32

盡快開發(fā)出這個功能,另外如果能讓燒錄器轉(zhuǎn)換成在線燒錄器并可以讀取FLASH,那么這個燒錄器功能就更加全面了,不過為了產(chǎn)品的差異化及開發(fā)成本考慮,估計這個可能性比較小。

不知道,有沒有大神借助這個硬件進行

2023-05-14 15:50:42

、會不會出現(xiàn)脫機燒錄器和仿真器并存的情況呢,仿真階段就實現(xiàn)了程序代碼下載到脫機燒錄器中。

真心感謝野火團隊的辛勤付出!

2023-05-24 21:36:23

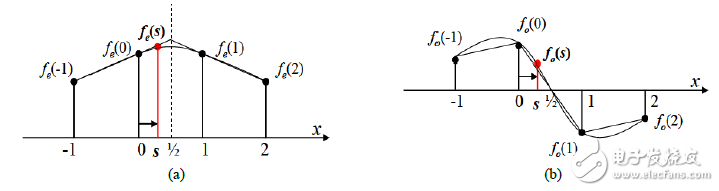

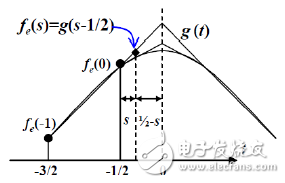

針對視頻的輸出顯示要求,重點介紹了基于雙線性插值算法的實現(xiàn)。ModelSim的仿真結(jié)果表明,該算法符合多屏幕顯示系統(tǒng)的要求。關(guān)鍵詞 視頻監(jiān)控;視頻圖像處理;雙線性插值;FPGA;多屏幕

2019-06-28 07:06:54

技術(shù)文檔。任職要求:1、電子、計算機、自動化、通信等專業(yè)本科以上學(xué)歷;2、一定的C/C++語言編程能力;3、精通matlab編程;4、有圖像處理算法基礎(chǔ);5、有ISP調(diào)試測試經(jīng)驗;6、熟悉3D相機成像

2018-08-28 15:29:00

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實現(xiàn)算法加速?

2021-04-13 06:39:25

什么是歸一化算法呢?怎樣去使用歸一化算法呢?

2022-02-25 06:19:05

本帖最后由 eehome 于 2013-1-5 10:06 編輯

從算法設(shè)計到硬件邏輯的實現(xiàn)(夏宇聞).pdfPCB打樣找華強 http://www.hqpcb.com 樣板2天出貨

2012-11-10 16:51:04

大家好,我是硬件和軟件的初學(xué)者。我的目標(biāo)是通過zedboard對視頻應(yīng)用我自己的過濾器。我已經(jīng)有了matlab代碼,我想切換到VHDL。我想通過HDLcoder轉(zhuǎn)換到simulink然后

2020-05-22 08:09:56

你好,我使用Ubuntu 14.4 lts并且我安裝了vivado和petalinux(V2015.4),所以當(dāng)我想使用SD卡在ZEDboard上啟動時,我嘗試做我的第一個項目,所以當(dāng)我嘗試下面

2020-05-25 09:17:33

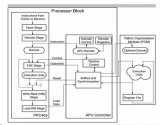

對基于軟件的算法處理進行編譯,微控制器可以在其地址空間中看到FPGA/MP模塊,并采用分布式DMA架構(gòu)優(yōu)化功能和存儲器模塊之間的數(shù)據(jù)流。圖1顯示了硬件/軟件劃分以及使用IP模塊庫來實現(xiàn)算法的整個步驟,IP

2008-09-27 11:42:55

單片機在硬件上是怎樣去實現(xiàn)CRC算法計算引擎的?

2022-02-23 06:10:19

卡爾曼濾波算法是怎么實現(xiàn)對數(shù)據(jù)的預(yù)測處理的

2023-10-10 08:28:02

本帖最后由 gk320830 于 2015-3-8 21:23 編輯

開始科創(chuàng),老師給了我們一個題基于FPGA的FFT算法硬件實現(xiàn)。但是什么都不會,想找些論文看看,求相關(guān)的論文

2012-05-24 22:14:40

是處理數(shù)字信號如圖形、語音及圖像等領(lǐng)域的重要變換工具。快速傅里葉變換(FFT)是DFT的快速算法。FFT算法的硬件實現(xiàn)一般有3種形式:1)使用通用DSP來實現(xiàn);2)用專用DSP來實現(xiàn);3)通過FPGA來

2009-06-14 00:19:55

了采用OpenMP 技術(shù)對電磁場FDTD算法程序實現(xiàn)并行化的方法,并將該并行方法在三維瞬態(tài)場電偶極子輻射FDTD程序中進行了驗證,也相當(dāng)于對該并行方法進行了一定的推廣,并通過實驗證明了該并行計算的有效性。

2019-07-04 06:00:19

和少量 C++ 類構(gòu)成,同時提供了Python、Ruby、MATLAB等語言的接口,實現(xiàn)了圖像處理和計算機視覺方面的很多通用算法,基于OpenCv可以方便的實現(xiàn)各種機器視覺的圖形算法處理,起提供了各種

2018-09-21 10:42:31

本帖最后由 gk320830 于 2015-3-8 06:44 編輯

大家來討論一下用蟻群算法實現(xiàn)路徑規(guī)劃的硬件實現(xiàn)問題,不僅僅是用matlab做仿真算法,具體的硬件連接都可以再下面討論,謝謝大家,共同學(xué)習(xí)~~

2013-04-26 17:19:54

如何去實現(xiàn)AES算法走D1芯片硬件CE模塊補丁呢?有哪些步驟?如何去測試?

2021-12-28 06:59:42

如何去實現(xiàn)一種基于stateflow圖形化編程的控制算法?有哪些步驟?

2021-07-21 08:11:20

一階低通濾波算法為例,在硬件電路中我們可以通過RC電路實現(xiàn)低通濾波功能,利用的便是電容原件的充放電特性。在

2021-08-09 08:23:30

能夠充分利用有限位長。這樣處理比定點方法擴大了動態(tài)范圍,并且提高了精度,比浮點運算在速度上有了提高。塊浮點結(jié)構(gòu)如圖4所示。3 結(jié) 語著重討論基于FPGA的64點高速FFT算法的實現(xiàn)方法。采用高基數(shù)結(jié)構(gòu)和流水線

2019-06-17 09:01:35

嗨,我是Vivado環(huán)境的新手,我正在嘗試通過Zedboard進行連接,以便我可以對其進行編程。我目前正在關(guān)注Hello World教程。我還引用了用于配置電路板的Zedboard Basic

2020-08-14 09:17:26

請問如何設(shè)計一個脫機型儀表硬件平臺?

2021-04-20 06:28:28

大家好,我需要將8位SRAM(例如,http://www.issi.com/WW/pdf/61LV5128AL.pdf)連接到我的Zedboard。我想我可以制作PCB,將SRAM焊接到其上并

2020-03-20 08:29:27

隨著移動通信用戶不斷增多,業(yè)務(wù)需求不斷多樣化,無線接入網(wǎng)的負(fù)載也逐漸增大,基站建設(shè)成本不斷升高[ 1 ]。將基帶信號處理算法用軟件來實現(xiàn)可以大大降低基站的硬件規(guī)模和成本,因而目前移動通信研究中對軟件

2019-08-02 08:21:55

急求直方圖均衡化的Verilog代碼或者是FPGA上算法處理的資料,多謝了

2015-06-02 17:51:33

本帖最后由 eehome 于 2013-1-5 10:04 編輯

指紋識別算法的研究及基于FPGA的硬件實現(xiàn)

2012-05-23 20:14:46

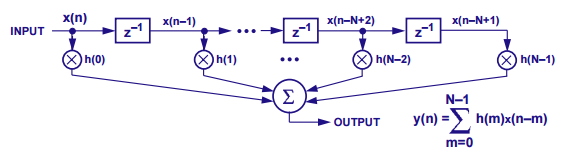

與解調(diào)、反卷積、SVD、獨立分量分析及同太民濾波等)、平穩(wěn)隨機信號的基本概念、經(jīng)典功率譜估計、參數(shù)模型功率譜估計、數(shù)字信號處理中的有限字長問題及數(shù)字信號處理的硬件實現(xiàn)等內(nèi)容。書中介紹了數(shù)字信號處理中所

2023-09-19 08:01:36

系統(tǒng)介紹數(shù)字信號處理理論、相應(yīng)的算法,以及實現(xiàn)這些算法的軟件和硬件

2016-05-04 21:29:42

不改變,轉(zhuǎn)子就會固定一個角度“鎖定”。一般不是太大的外力是不會使它轉(zhuǎn)動的。而如果掉電(脫機)了,那么轉(zhuǎn)子就完全“放松”了,外力輕易的就可以把它轉(zhuǎn)動。因此,一個步進電機如果此時沒有轉(zhuǎn),

2021-07-08 06:17:27

用FPGA硬件實現(xiàn)。 現(xiàn)在我沒有FPGA硬件實現(xiàn)的經(jīng)驗,不知道如何用FPGA硬件實現(xiàn)小波算法。 懇請賜教!謝謝!

2012-11-20 21:35:16

本文在詳細(xì)分析傳統(tǒng)算法的優(yōu)劣基礎(chǔ)上,提出了新的圖象重組算法,而流水線式分時復(fù)用資源的實現(xiàn)方法節(jié)省了接近一半的資源,很好地克服了模塊實時性要求,主頻時鐘限制和demosaicing算法復(fù)雜性帶給硬件實現(xiàn)資源成本高的問題。

2021-06-04 06:39:20

本人大四,做一個關(guān)于腦電信號特征提取的算法分析,然后優(yōu)化后用硬件實現(xiàn),要求比較簡單,就是只要能把腦電信號中比如α波或者β波分離出來,通過對基本節(jié)律的頻域分析,提取其基本的強度等特征,進而對大腦實時

2013-05-15 19:15:24

用FPGA實現(xiàn)優(yōu)化的指紋識別預(yù)處理算法在選取較優(yōu)化的指紋識別預(yù)處理算法的基礎(chǔ)上,根據(jù)算法的結(jié)構(gòu)選取具有并行處理、低功耗、速度快等特點的FPGA作為實現(xiàn)算法的基本器件。由于用FPGA實現(xiàn)復(fù)雜算法較傳統(tǒng)

2009-09-19 09:38:11

我的畢業(yè)設(shè)計課題,網(wǎng)絡(luò)接口可脫機時間繼電器控制模塊的設(shè)計與實現(xiàn),基本上沒有什么頭緒,求各位大神指導(dǎo),現(xiàn)在連開題報告都不知道怎么寫,還有硬件電路,軟件編程,各種煩人啊,求求各路大神給點思路,謝謝啊

2014-02-26 10:11:14

觸摸屏數(shù)據(jù)處理算法研究及實現(xiàn)

2012-08-15 16:32:39

一般用硬件怎么實現(xiàn)rsa加密算法?

2023-10-17 07:02:42

如何使用Verilog硬件描述語言實現(xiàn)AES密碼算法?

2021-04-14 06:29:10

針對硬件實現(xiàn)的H.264視頻編碼算法改進,不看肯定后悔

2021-06-04 06:25:51

針對硬件實現(xiàn)的h.264視頻編碼算法改進針對硬件實現(xiàn)的視頻編碼算法改進上海交通大學(xué)圖像通信與信息處理研究所 周怡吳昊方向忠摘要’ 從硬件實現(xiàn)的角度分析了算法# 重點研究了占用最多運算時間的預(yù)測部分

2008-06-25 11:35:14

本文研究了SAR雷達(dá)原始數(shù)據(jù)BAVQ壓縮算法的硬件實現(xiàn)。采用ADSP21060(SHARC)芯片結(jié)合Altera公司的FLEX Xl OK l 0LC84-3芯片組成最簡的系統(tǒng),采用流水線并行處理高速有效的實現(xiàn)了BAVQ壓縮算法。

2009-05-09 10:55:24 21

21 在現(xiàn)有的二相混沌加密算法研究的基礎(chǔ)上,提出了一種改進的實用混沌加密算法,使其有限字長效應(yīng)得到了改善,并借助于數(shù)字信號處理器TMS320VC5402實現(xiàn)了改進方法。硬件實驗結(jié)

2009-05-16 11:18:58 25

25 提出用FPGA 來實現(xiàn)指紋識別算法, 代替了PC 機、通用MCU 或者DSP。算法由硬件來實現(xiàn), 提高了運算速度。同時具體說明了指紋識別系統(tǒng)的基本原理、系統(tǒng)總體結(jié)構(gòu)、FPGA 模塊劃分, 以及指

2009-07-22 15:17:27 0

0 基于圖像記錄設(shè)備小型化的需求,結(jié)合IDE 硬盤直寫存儲技術(shù)和硬件協(xié)議處理的以太網(wǎng)絡(luò)數(shù)據(jù)傳輸技術(shù),采用現(xiàn)場可編程門陣列設(shè)計實現(xiàn)了一種脫機圖像記錄系統(tǒng)。該設(shè)計可獨立于

2009-09-25 16:02:09 14

14 分別從整體和局部的角度,提出Camellia 算法幾種基于硬件編程實現(xiàn)的優(yōu)化方法。在整體角度,以輪循環(huán)和模塊復(fù)用方式實現(xiàn)緊湊型結(jié)構(gòu),而以流水線方式實現(xiàn)高速型結(jié)構(gòu);在局

2010-01-15 15:49:14 13

13 摘要! 在實際系統(tǒng)中對游程檢測的實現(xiàn)速度$電路規(guī)模有很高的要求# 而傳統(tǒng)的檢測方法性能 較低% 針對此問題提出了一種新的游程檢測算法% 該算法基于硬件實現(xiàn)#電路結(jié)構(gòu)簡單實現(xiàn)速度

2011-03-31 15:47:06 18

18 本內(nèi)容提供了數(shù)字信號處理-理論算法與實現(xiàn) 電子書,歡迎大家下載學(xué)習(xí)

2011-07-22 11:34:32 0

0 DV611芯片是美國ANALOG DEVICES公司生產(chǎn)的一種利用小波算法對視頻圖像進行實時壓縮/解壓縮處理的編/解碼芯片。本文介紹一種基于ADV611芯片、同時結(jié)合TI的DSP芯片TMS320C542實現(xiàn)的一種脫機視

2011-09-17 02:04:19 1175

1175

基于ZedBoard和linux的應(yīng)用程序HelloWorld的實現(xiàn)(完整工程)獲取Zedboard可運行的linux Digilent官網(wǎng)給出Zedboard的可運行l(wèi)inux

2013-01-24 14:15:46 152

152 從算法設(shè)計到硬件邏輯的實現(xiàn)

有需要的朋友下來看看

2015-12-29 16:47:54 6

6 ZEDBoard官方資料合集,包括用戶手冊、電路原理圖

2016-01-20 15:53:21 336

336 如何通過STM32的串口實現(xiàn)簡易脫機編程器如何通過STM32的串口實現(xiàn)簡易脫機編程器如何通過STM32的串口實現(xiàn)簡易脫機編程器如何通過STM32的串口實現(xiàn)簡易脫機編程器。

2016-04-25 09:38:10 59

59 順序形態(tài)圖像處理器的硬件實現(xiàn),下來看看。

2016-09-17 07:26:30 7

7 利用FPGA實現(xiàn)信號處理算法是一個難度頗高的應(yīng)用,不僅涉及到對信號處理算法、FPGA芯片和開發(fā)工具的學(xué)習(xí),還意味著要改變傳統(tǒng)利用軟件在DSP上實現(xiàn)算法的習(xí)慣,從面向硬件實現(xiàn)的算法設(shè)計、硬件實現(xiàn)、結(jié)構(gòu)優(yōu)化和算法驗證等多個方面進行深入學(xué)習(xí)。

2016-12-26 17:26:41 12

12 今天所討論的內(nèi)容就是通過QT開發(fā)的GUI軟件來控制ZedBoard板上的硬件外設(shè),完整的信號鏈如下:QT GUI → Linux Driver → AXI Bus → My_GPIO

2017-02-11 01:28:12 1887

1887

算法進行深入研究,面向Xilinx K7 410T FPGA 芯片設(shè)計SHA-1算法實現(xiàn)結(jié)構(gòu),完成SHA-1算法編程,進行測試和后續(xù)應(yīng)用。該算法在FPGA 上實現(xiàn),可以實現(xiàn)3.2G bit/s的吞吐

2017-10-30 16:25:54 4

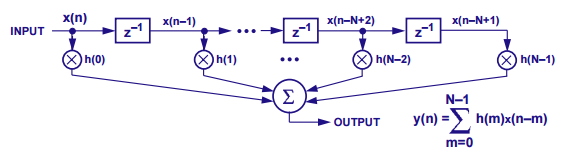

4 ) VECx技術(shù)以加速電路的計算性能,分析與評估硬件與軟件對實現(xiàn)FIR濾波算法的影響。實驗結(jié)果表明,采用硬件等效替代的方法能使單個FIR濾波能

2017-11-03 10:29:52 10

10 引導(dǎo)濾波算法被大量用于圖像處理領(lǐng)域中,在去雨雪、去霧、前景提取、圖像去噪、圖像增強、級聯(lián)采樣等方面有很好的處理效果。但是對于實時應(yīng)用,軟件實現(xiàn)難以滿足需要。提出了在SDSoC環(huán)境下利用軟硬件協(xié)同開發(fā)

2017-11-16 14:40:18 1254

1254 慢耗時長的問題,設(shè)計實現(xiàn)一種基于Zedboard的掌靜脈快速識別認(rèn)證系統(tǒng)。該系統(tǒng)由片上處理系統(tǒng)(Processing System,PS)完成掌靜脈圖像采集、預(yù)處理,可編程序邏輯陣列

2017-11-17 04:53:01 1365

1365

了ZedBoard平臺的硬件結(jié)構(gòu),并針對SCA架構(gòu)在專用硬件平臺上無法實現(xiàn)的問題,通過分析研究MHAL硬件抽象層技術(shù)和OCP接口規(guī)范,設(shè)計了符合ZedBoard平臺硬件環(huán)境的MHAL硬件抽象接口和FPGA波形

2017-11-17 07:19:14 5298

5298

該文介紹了ZedBoard平臺下可編程邏輯端SPI接口和ARM處理器端以太網(wǎng)遠(yuǎn)端傳輸?shù)脑O(shè)計。結(jié)合實例闡述了可編程邏輯端SPI接口設(shè)計和Linux下IP驅(qū)動生成,以及采用UDP/IP協(xié)議實現(xiàn)以太網(wǎng)傳輸?shù)募夹g(shù)。實驗結(jié)果證明了該系統(tǒng)能夠精確地完成實時數(shù)據(jù)傳輸。

2017-11-17 12:12:10 2586

2586 針對GPS抗干擾問題,常用手段是在信號處理系統(tǒng)中采用自適應(yīng)調(diào)零算法來實現(xiàn)抗干擾。結(jié)合該算法文中給出了一種信號處理系統(tǒng)的硬件實現(xiàn)方案。首先概述GPS自適應(yīng)調(diào)零天線的系統(tǒng)結(jié)構(gòu),然后給出信號處理系統(tǒng)的硬件設(shè)計思路及其功能模塊的實現(xiàn),最后通過實測數(shù)據(jù)驗證硬件模塊可以滿足自適應(yīng)調(diào)零算法的要求。

2017-11-24 16:19:35 2067

2067

當(dāng)今的設(shè)計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現(xiàn)嵌入式設(shè)計。在嵌入式系統(tǒng)中,通常是由相對數(shù)量較少的算法決定最大的運算需求。使用設(shè)計自動化工具可以將這些算法快速轉(zhuǎn)換到硬件協(xié)處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級的性能。

2018-07-22 11:54:00 1121

1121

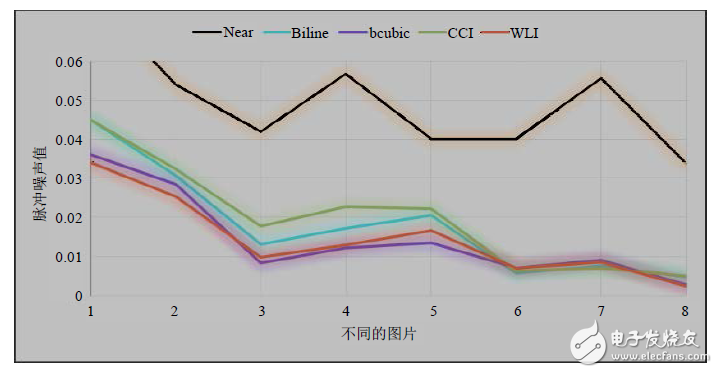

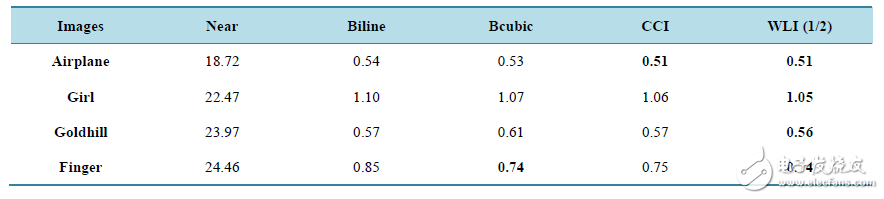

、邊緣模糊等級和脈沖噪聲等指標(biāo)評估基于該算法圖像處理效果。與傳統(tǒng)時域算法作對比,對比結(jié)果表明該算法在處理效果和運算速度上的優(yōu)異性。基于Zedboard開發(fā)板,運用Vivado HLS高級綜合工具將算法的C程序綜合成硬件IP,并搭建了包含ARM處理器和VGA等

2017-12-12 14:07:38 2

2 zedboard可以將邏輯資源和軟件分別映射到PS和PL中,這樣可以實現(xiàn)獨一無二和差異換的系統(tǒng)功能,主要分為兩大部分,處理系統(tǒng)和可編程邏輯。以及二者之間的互聯(lián)特性。這篇筆記主要記錄zedboard的大體架構(gòu)。

2018-06-26 06:24:00 6394

6394 Zedboard是一個基于Xilinx Zynqtm-7000全可編程SoC(AP SoC)的評估和開發(fā)板,它結(jié)合了雙COREX-A9處理系統(tǒng)(PS)和85000系列7可編程邏輯(PL)單元,可以

2019-02-12 17:20:32 87

87 本文檔的主要內(nèi)容詳細(xì)介紹的是使用ZedBoard技術(shù)實現(xiàn)LED燈的教程免費下載。

2019-12-06 10:36:00 36

36 對微處理器的處理能力提出了更高的要求。由于通用數(shù)字信號處理芯片能夠通過編程實現(xiàn)各種復(fù)雜的運算,處理精度高,具有較大的靈活性,而且尺寸小、功耗低、速度快,所以一般選擇DSP芯片作為微處理器來實現(xiàn)ATR算法的工程化和實用化。 為了保證在DS

2022-12-20 18:37:09 746

746 功能.文中將軟硬件實現(xiàn)的順序形態(tài)圖像處理圖片在處理效果和速度兩個方面作了比較.算法在FPGA芯片上的高速實現(xiàn)特征使數(shù)學(xué)形態(tài)學(xué)在圖像實時處理領(lǐng)域的應(yīng)用成為可能。

2021-04-01 11:21:46 8

8 數(shù)字信號處理——理論、算法與實現(xiàn)說明。

2021-04-26 09:17:38 40

40 面向硬件實現(xiàn)的HEVC幀內(nèi)編碼快速算法

2021-06-21 16:30:15 10

10 較大。為了易于算法的硬件實現(xiàn),提出用線性逼近計算覆蓋區(qū)域邊長和對數(shù)的算法。該算法用一次移位和一次加法實現(xiàn)覆蓋區(qū)域邊長計算,用一次加法實現(xiàn)對數(shù)計算,降低了硬件實現(xiàn)成本。在Xinx的ZC706開發(fā)板上實現(xiàn)了文中算法,實驗結(jié)果表明,該算法所計

2021-06-21 17:04:17 8

8 當(dāng)今的設(shè)計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現(xiàn)嵌入式設(shè)計。在嵌入式系統(tǒng)中,通常是由相對數(shù)量較少的算法決定最大的運算需求。使用設(shè)計自動化工具可以將這些算法快速轉(zhuǎn)換到硬件

2021-09-28 10:38:04 3586

3586

之前我們基于matlab板級支持包在matlab的控制下,利用ZedBoard+AD9361的硬件板卡套裝產(chǎn)生了點頻信號。

2022-12-30 11:06:37 1024

1024 在 MATLAB 或 Simulink 中實現(xiàn)任何信號處理算法后,下一個自然步驟是使用從將要運行的實際 SDR 硬件系統(tǒng)獲取的真實數(shù)據(jù)來驗證算法的功能。作為第一步,使用從系統(tǒng)捕獲的不同輸入數(shù)據(jù)集完成算法的驗證。

2023-01-08 10:48:21 843

843

到目前為止,我們已經(jīng)描述了DSP處理器的物理架構(gòu),解釋了DSP如何提供與傳統(tǒng)模擬電路相比的一些優(yōu)勢,并研究了數(shù)字濾波,展示了DSP的可編程特性如何適用于此類算法。現(xiàn)在,我們來看看在硬件平臺

2023-06-17 11:49:03 923

923

微處理器芯片對圖像進行編/解碼處理來實現(xiàn)。這種脫機的圖像處理系統(tǒng)由于體積小和靈活簡便而受到廣泛關(guān)注。微處理器芯片可以采用專用圖像編/解碼芯片。

2023-07-23 16:15:53 368

368

電子發(fā)燒友App

電子發(fā)燒友App

評論