Cassie Ren,復睿微電子架構專家,畢業于新加坡國立大學,曾就職于新加坡瑞昱半導體,在芯片低功耗、信息安全等領域工作經驗豐富。

背景

從陸續出臺的相關政策上來看,自動駕駛行業是當前國家重點支持的領域,近些年來,我國的自動駕駛行業也在多方的支持下蓬勃發展。隨著軟件和硬件條件的日趨成熟,新車搭載L2級別自動駕駛功能正逐漸成為智能汽車的前裝標配。當前我國量產乘用車的自動駕駛級別也在從L2向L3+過渡,甚至很多科技公司已經開始研發L4級別的自動駕駛芯片及其解決方案。隨著市場對汽車自動駕駛等級需求的提高,汽車搭載的自動駕駛芯片的算力需求也越來越高,而算力更高的芯片也會帶來更高的功耗。對于消費者和車廠來說,功耗問題一直都是他們關注的焦點,如何實現低功耗高性能,是芯片設計方及其上游要一起解決的問題。

1降低功耗的優點

為什么需要功耗管理呢?這里來簡單聊一下。

1) 功耗過大會縮短使用時間,常用手機等電子設備的我們也知道,頻繁充電會大大降低我們的用戶體驗。

2) 功耗過大會造成更高的溫度,較高的溫度會引起電子遷移或者其他的熱失效機制,從而降低芯片的穩定性。

3) 對于汽車而言,自動駕駛芯片的功耗超過一定限度,則會需要車廠采用水冷措施來降溫而不是風冷系統,這也會提高整車的制造成本。

4) 功耗大也會影響電池壽命,使電池壽命更短,這也從一定程度上提高了用戶的成本及降低了用戶的產品體驗。

所以片上系統的功耗是一個非常重要的話題,作為芯片設計方,使搭載到智能汽車的自動駕駛芯片擁有更低的功耗貫穿了我們工作的始終,從前期芯片非自研IP選型,到中期芯片設計,到后期的軟件及解決方案,我們將從每個階段盡量降低芯片的功耗,在保證算力的同時提供更穩定更具市場競爭力的自動駕駛芯片。

2降低功耗的方式[1]

2.1基本概念

首先要介紹兩個概念:動態功耗和靜態功耗。SoC的功耗包括動態功耗(Dynamic Power)和靜態功耗(Static Power)。

動態功耗(Dynamic Power)

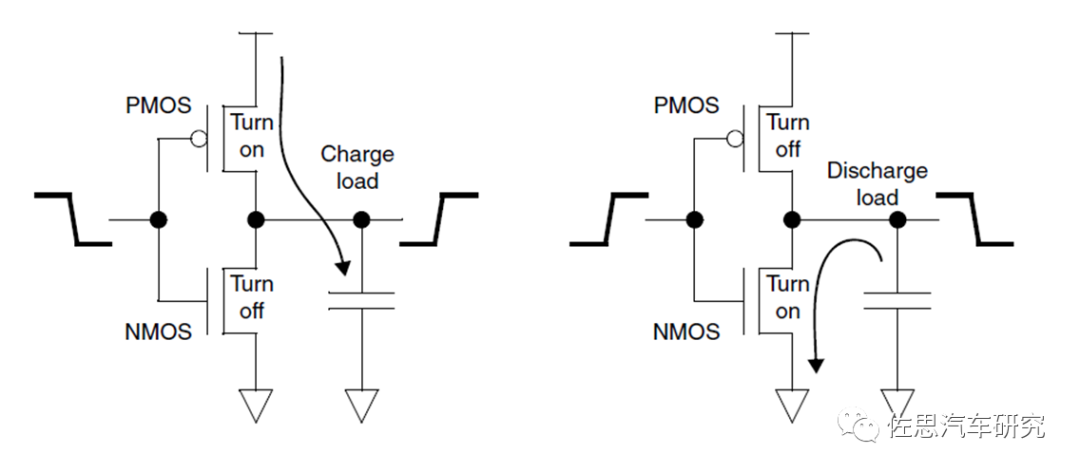

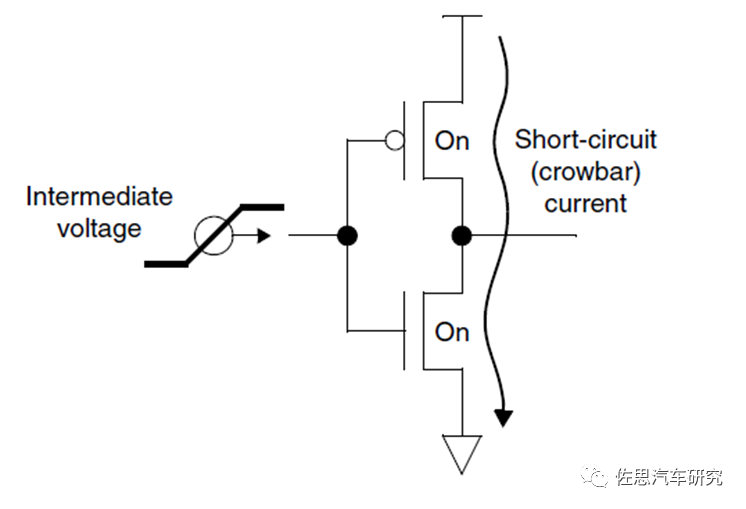

動態功耗是因為信號值改變帶來的功耗損失。動態功耗由兩部分組成:開關功耗(switching power)和內部功耗(internal power)。開關功耗是外部電容充放電消耗的功率(如圖1所示),內部功耗是電路邏輯狀態變化時流過PMOS-NMOS堆的短路電流消耗的功率(如圖2所示)。

圖1

圖2

靜態功耗(Static Power)

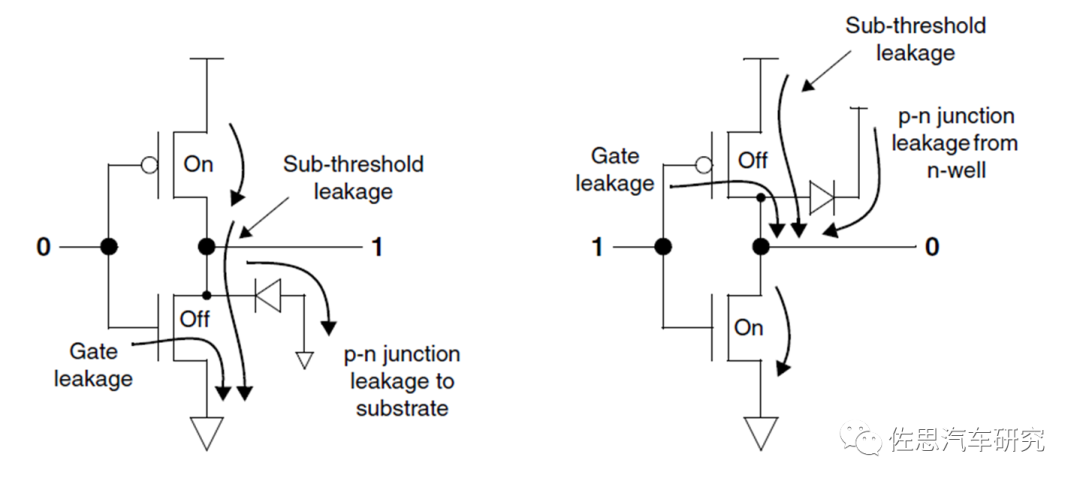

靜態功耗是設備還在上電狀態但是沒有信號值改變時消耗的功率。在CMOS設備中,靜態功耗來源于漏電(如圖3所示)。

圖3

2.2降低功耗的方式

2.2.1 降低供電電壓(Supply VoltageReduction)

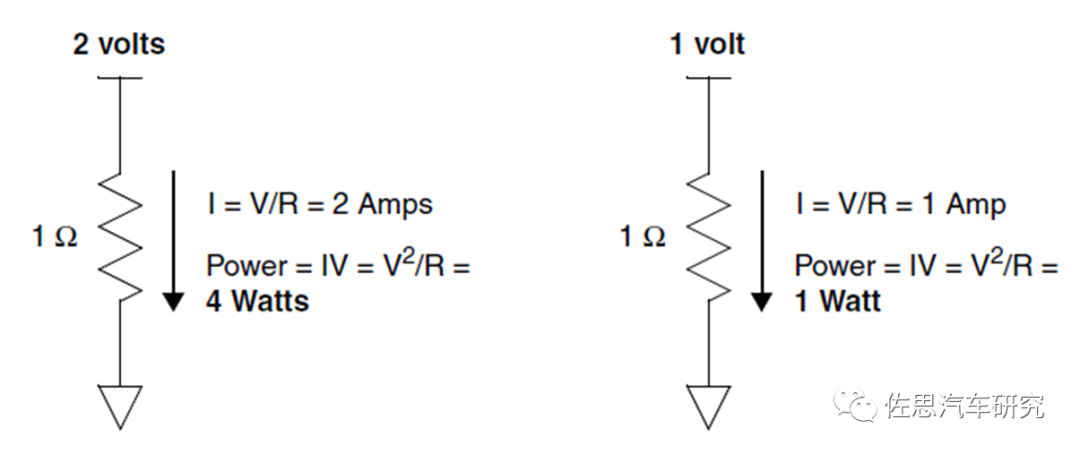

最基礎的降低功耗的方式是降低供電電壓。功耗與電壓的平方成正比。所以如果降低50%的電壓,功耗會降低75%(如圖4所示)。CMOS技術的不斷更新迭代使供電電壓越來越低以降低功耗,供電電壓從上世紀八十年代的5V降低到當前0.75V甚至更低。

圖4

2.2.2 時鐘門控(Clock Gating)

時鐘門控(clock gating)是一種降低動態功耗的方式。對于那些很多個時鐘周期下都需要保持同一個數值的寄存器來說,這種降低功耗的方式非常有用,因為這種方式可避免每個時鐘周期都重新加載寄存器而帶來的不必要的功耗損失。這個方法最大的挑戰是如何找到最優的位置來放置時鐘門控,以保證在合適的時間開關時鐘。

時鐘門控技術沿用了多年,也很成熟。Power Compiler等綜合工具可以監測到低吞吐量的數據路徑,然后在時鐘路徑上合適的位置自動插入時鐘門控單元。時鐘門控的實現也比較簡單,它只需要改網表,而不需要額外增加電源供電或者其它電源設施。

2.2.3 多Vt庫單元(Multiple-Vt Library Cells)

一些CMOS技術支持具有不同電壓閾值的標準庫單元。在這種情況下,單元庫可以提供兩種甚至更多不同的閾值電壓單元來實現相同的邏輯功能。舉個例子:庫里可以提供兩種反相器單元:一種是low-Vt晶體管,一種是high-Vt晶體管。

Low-Vt單元有更高的速度,但是同時擁有更大的漏電流。High-Vt單元有更低的漏電流,但是速度更慢。所以綜合工具可以根據速度和功耗的tradeoff來選擇合適類型的單元。比如可以用low-Vt單元在timing-critical的路徑以達到更高的速度,至于對timing要求不是很高的路徑可選用high-Vt單元以減少功耗。

2.2.4 多電壓設計(Multi-voltage Design)

芯片不同的部分有不同的速度需求。比如CPU和RAM需要比外設擁有更高的速度。就像前面提到的,低電壓不僅會降低功耗也會降低速度。為了得到最大的速度和更低的功耗,可以給CPU和RAM提供較高的供電電壓,而給外設部分提供較低的供電電壓。但是在同一個芯片上提供兩個或多個供電會增加設計復雜性和成本。比如需要更多的管腳來給芯片供電,而且電源網格必須將每個電壓源分別分配給適當的模塊。

2.2.5 電源開關(Power Switching)

電源開關是在芯片的某個模塊長時間不用的情況下,通過關掉電源的方式來節省功耗的一種方式。比如一個手機芯片,當手機處于待機模式的時候關掉聲音處理模塊。當用戶收到電話或者打電話的時候,這個模塊會被喚醒。

電源開關進一步降低了靜態功耗和動態功耗。但是它也帶來了一些挑戰,比如它的實現需要一個電源控制器,一個電源開關網絡,隔離單元(isolation cells)和retention寄存器。

電源控制器就是一個決定什么時候上下電的邏輯模塊。但是上電和下電會帶來一定的時間和功耗代價,所以控制器必須決定一個合適的時間來開關電源。

一個可以被下電的模塊必須從電源開關網絡中收到供電,電源網絡由大量在always-on的電源軌道和供電引腳單元之間有source-to-drain連接的晶體管組成。電源開關必須在該模塊周圍或者內部。這個網絡,當打開電源時,連接了電源和邏輯門,當關上電源時,電源供電就從邏輯門斷開連接。

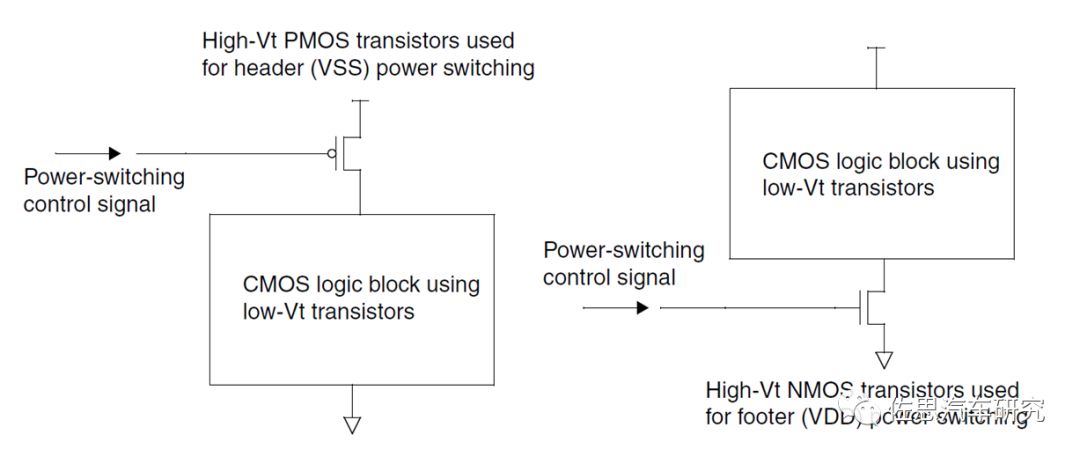

我們常常會把High-Vt晶體管用作電源開關(power switch),因為它可以有更小的漏電流并且我們也不關心它的開關速度。如圖5所示,PMOS header 開關可以被放在VDD和模塊供電電源管腳中間,或者NMOS footer 開關可以被放在VSS和模塊地管腳中間。 ?

圖5

上面描述的電源開關策略是粗粒度的開關策略,因為這個電源開關可以控制整個模塊的上下電。如果是細粒度策略,則每個庫單元都有自己的電源開關,允許更細粒度的控制電源上下電。這種方式可以更好的節省功耗,但是也要求更大的面積。

2.2.6 動態電壓頻率調整(Dynamic Voltage FrequencyScaling)

根據前面提到的多電壓(Multi-voltage)的概念,我們可以將其拓展成操作過程中根據當前的工作負載而動態調整電壓。比如一個芯片在做簡單的計算時可以用更低的電壓和更低的頻率,如果需要更高的性能,則可以提高電壓和頻率。這種實時調整電壓和頻率的方式叫做DVFS。

芯片的供電電壓可以被設計為多個檔位或者一個連續的范圍,動態調壓要求多檔位的供電及一個能準確判斷給定任務的最優電壓值的邏輯模塊。因為要分析和考慮到不同的電壓等級和頻率的結合,所以這對設計、執行、驗證和測試來說都是不小的挑戰。

我們可以將動態調壓和電源開關結合起來,讓模塊既可以根據當前工作負載調整電壓也可以在完全不用的時候關掉電源,以達到更多的功耗節省。

3功耗管理模塊[2]

隨著當代SoC的復雜程度的提高,越來越多的芯片設計者選擇將SoC中的功耗管理的角色獨立出來,選擇一個小的處理器結合軟件來負責整個SoC的功耗管理。

以前是用操作系統(OS)來管理SoC的功耗和性能,但是慢慢發現形成和維護一個通用的OS kernel來支持不同供應商非常困難,且現在的SoC也有越來越多的限制,也迫使有能多的功能安全和信息安全的要求,這些對OS來說都過于復雜以至于無法在管理的同時滿足最優負載性能。這就迫使工業界把基于OS的集中的控制機制剝離出來,形成一個專門用來控制和管理功耗和性能的小系統。

前面提到動態調壓調頻(DVFS), DVFS會根據OS的工作負載選擇{頻率,電壓}對,這就要求OSkernel要知道該平臺支持的所有的{頻率,電壓}對的信息,然后還要知道如何讀取和設置它們。每個SoC的讀取和設置信息對的方式不同,所以如果需要OS kernel來管理功耗和性能,就需要根據每個SoC的設計更改kernel,這個與大家想保持kernel的通用性的想法相悖。因此,我們可以將平臺支持的{頻率,電壓}對記錄在功耗管理小系統中,并將性能等級與頻率電壓對進行一一對應,OS kernel僅需發出調整頻率電壓請求給小系統,小系統便可根據請求對頻率和電壓進行相應的調整。這樣做既達到了控制的效果,也維護了OS kernel的通用性。

在功能安全方面,當出現偶發事件時,通常來說硬件的反應時間小于固件的反應時間小于內核Kernel的反應時間。圖6展示了典型場景下,硬件hardware、固件firmware、OSKernel對SoC平臺偶發事件的反應時間。從圖6可以看出,kernel的反應時間遠大于固件的反應時間。而且,Kernel也無法知道SoC上所有功能安全相關的操作,所以這些事情也可以委派給到功耗控制小系統。該小系統有更快的反應時間且可以提供功能安全的保證,也可以享有控制SoC內其他的硬件的權力。

圖6

此外,在信息安全方面,OS的DVFS實現在kernel,kernel位于BL1,而BL1是不可信(untrusted)的。如果kernel擁有頻率和電壓的控制權是比較危險的。不可信的軟件可能會把SoC平臺置于overclocked或者undervolted的狀態。所以我們把對頻率和電壓的控制權轉交給一個可信的firmware,這個firmware可以對要求的性能等級進行可信度檢查,以避免惡意編程帶來的危害。

4系統低功耗模式及設計

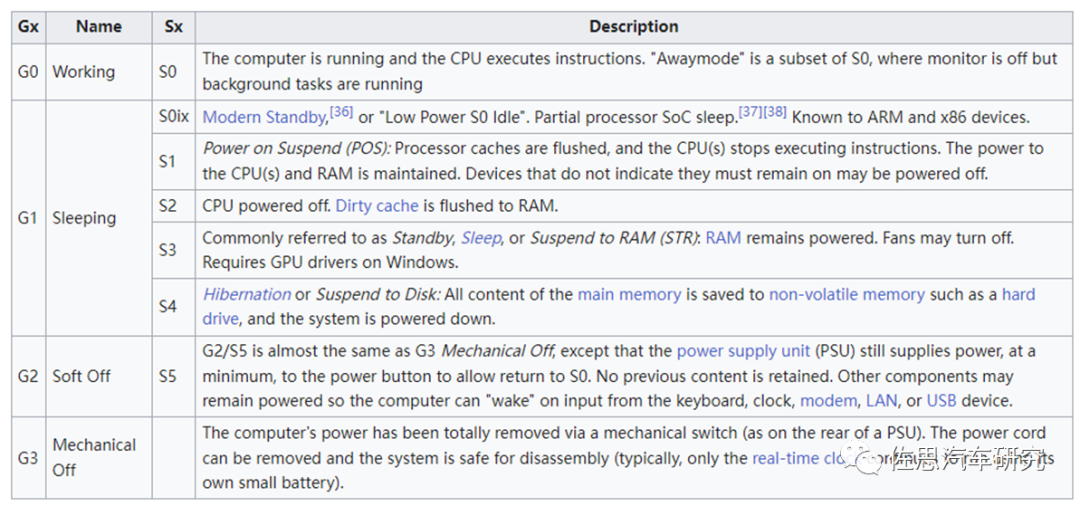

ACPI[3]定義了G0~G3四種電源狀態,G0是工作狀態,G3是關電狀態。G1和G2又分出了S0ix到S5的睡眠狀態,且定義了每種睡眠狀態下CPU,GPU及memory等模塊的狀態(如表1所示)。

表1

對于SoC而言,首先需要支持工作和關電兩種電源狀態,然而介于這兩種狀態之間的睡眠態是應用場景需求決定的。當前汽車行業仍處于一個發展階段,對于自動駕駛芯片的功耗模式定義尚未形成較固定的方案。根據當前自動駕駛芯片串聯座艙芯片的場景來分析,現在很多汽車會支持前裝哨兵模式,該模式則需要在汽車熄火且人離開汽車后,汽車上的傳感器可以感知物體靠近來喚醒車身上的攝像頭。喚醒攝像頭意味著控制其的芯片也需被喚醒,使其將周圍發生的情況通過攝像頭記錄并保存下來。然而,如果該功能下自動駕駛芯片完全關電,喚醒時芯片從上電到可以工作的時間可能要10秒以上,這是無法滿足場景需求的。所以這就要求在該模式下自動駕駛芯片支持一個快速喚醒的低功耗狀態。為什么需要一個低功耗狀態?因為如果還保持之前的工作狀態,芯片的耗電量會比較大,從而造成車機很快沒電,非常影響用戶體驗及電池壽命。所以前裝哨兵模式需要自動駕駛芯片必須支持至少一種低功耗模式。

此外,一些車廠可選擇汽車熄火后不完全給自動駕駛芯片和座艙芯片關電,而是選擇讓它們處于一種超低功耗的模式。這樣做帶來的好處是一旦點火,車機系統可以非常快的啟動到離開車前的狀態。一般座艙芯片會采用Android系統,Android系統的啟動可能需要十秒以上的時間,也就是說用戶從啟動汽車到看到顯示屏顯示可能需要十幾秒甚至更久的時間,這會大大降低用戶的產品體驗。低功耗模式可以將下電前的軟件現場保存在DDR連接的DRAM顆粒中,并使DRAM顆粒處于一種retention狀態,且僅保持一個耗電量很小的處理器小系統在工作。這個小處理器在收到喚醒信號后,可以將現場快速恢復到車機系統到離車前狀態。這個狀態耗電量很小,且可以快速喚醒,可以在耗費很小電量的同時解決因操作系統啟動較慢而造成的不良體驗的問題。這種功能也需要自動駕駛芯片支持低功耗模式。

4.1系統低功耗模式設計

4.1.1 電源域

首先要介紹一下電源域概念,電源域是指同一個電壓域內,共享相同電源開關邏輯的模塊合集。前面有提到,多電壓設計是降低功耗的一種方式,不同的電壓就會是不同的電源域。對于現在功能比較復雜的SoC而言,多電源域設計是必須的選擇。

4.1.2 基于多電源域的低功耗模式設計

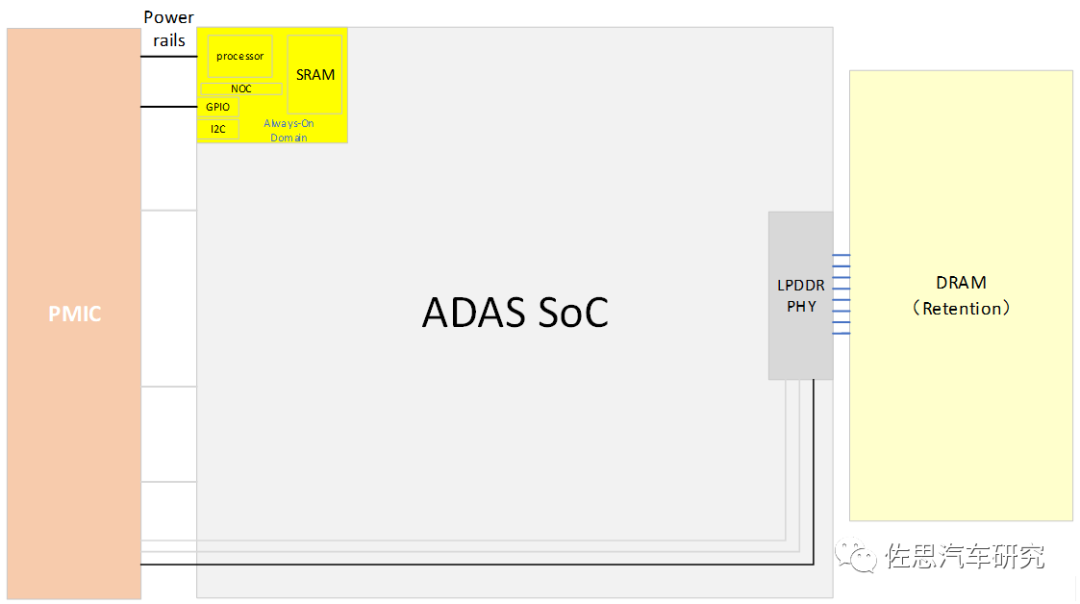

前面提到自動駕駛芯片的應用場景,如果要支持低功耗模式,如何降低功耗?整體思路就是要把該模式下不需要用到的模塊做關電處理,以節省動態功耗和靜態功耗。而對于無法做關電處理的模塊,我們保留其供電,但是在供電狀態下,選擇該模塊的低功耗模式以達到最多的功耗節省。比如memory,我們需要用到連接到LPDDR的DRAM顆粒保存軟件棧現場的信息,RAM的特性是一旦下電,數據就會消失,所以我們會采用保存其數據不消失但最省電的一種功耗模式-Retention模式。之前我們還提到,SoC的功耗管理模塊是一個以一個處理器為核心的小系統,所以該場景下需要該處理器保持運行,以監測外界的喚醒信息及幫助其他處理器核快速恢復現場。之前介紹了電源域,電源域中通常會有一個常電(Always-On)電源域,該電源域享有最高的電源等級,即在所有電源域中它掉電的優先級最低。低功耗模式下,該處理器要在上電狀態,所以該處理器處于Always On電源域。處理器要運行,還需要內存來及時讀寫變量,所以該處理器要使用的SRAM也是在電狀態。此外,還要有GPIO作為接收喚醒中斷信息的源頭,該GPIO收到喚醒中斷信息并將其傳給處理器,處理器接收到喚醒中斷后啟動其恢復現場程序。所以總的來說,該低功耗模式下需要一個管理功耗的子系統處于運行狀態和DRAM顆粒處于Retention模式,其中子系統應包括一個處理器核,一塊運行程序的內存,用于接收喚醒信號的GPIO,用于與PMIC通信的接口,及用于聯通各個子模塊的內部總線等。這樣的一個功耗管理小系統加DRAM顆粒retention狀態的設計即可滿足在耗電量極低的情況下快速喚醒整片SoC的需求。示意圖如圖7,其中亮黃色為功耗管理小系統,處于Always-On電源域。除此之外,有一路供電給到DDR PHY以保持DRAM的Retention狀態。

圖7

結語

本文對自動駕駛芯片的功耗管理做了一個簡單的介紹,除了上面提到的部分,還有很多可以節省出功耗的方法。芯片只是這個行業鏈上的一個部分,整個系統的功耗控制才是最終的目標,需要每個環節上的人做出努力。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論