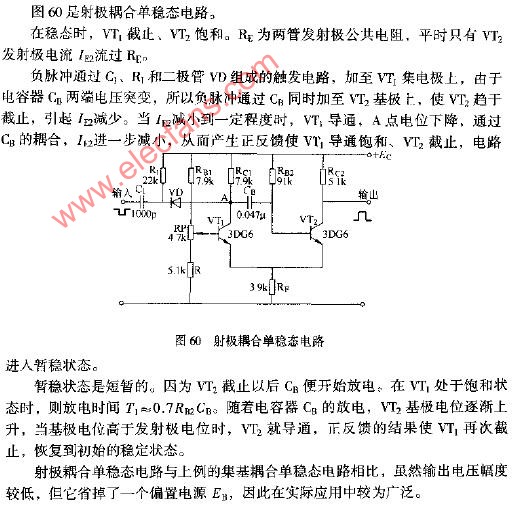

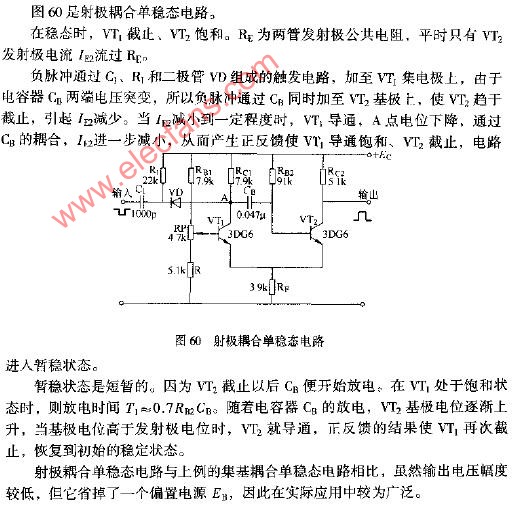

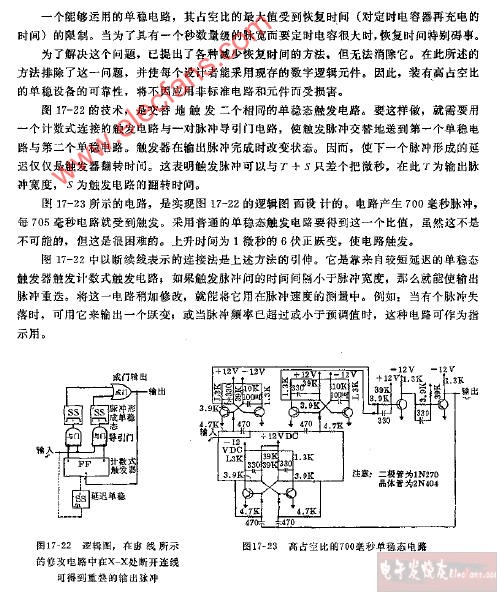

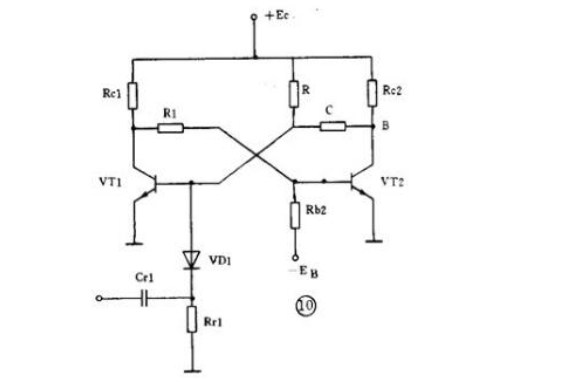

射極耦合單穩態電路圖

2010-03-29 17:43:59 1420

1420

隨著電子技術特別是數字集成電路技術的迅猛發展,市面上出現了FPGA、CPLD等大規模數字集成電路,并且其工作速度和產品質量不斷提高。

2015-05-22 11:33:02 3086

3086

單穩態電路中定時電容器的漏電流對定時時間有何影響?如何提高定時精度?

2023-04-12 14:15:23

輸出脈沖。單穩態多諧振蕩器僅在經過RC耦合電路的時間常數確定的時間后,才返回到其最初的原始穩定狀態。考慮左側的MOSFET電路。電阻器R和電容器C形成RC定時電路。由于電容器兩端的電壓,N溝道增強模式

2020-11-25 09:45:23

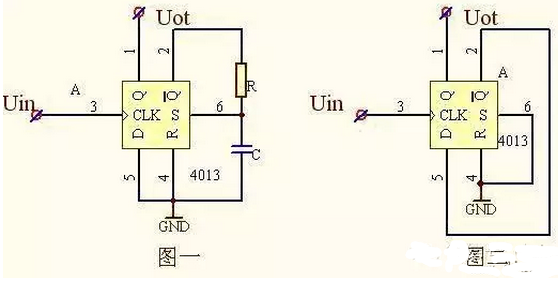

單穩態延時觸發器

2019-11-08 09:01:59

什么是單穩態觸發器?單穩態觸發器的工作特點是什么?

2021-04-22 06:09:01

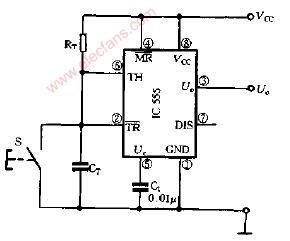

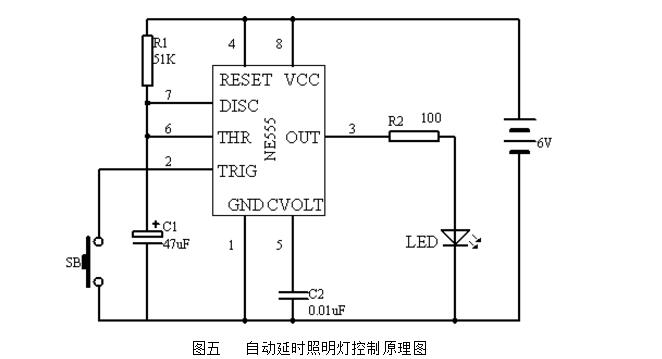

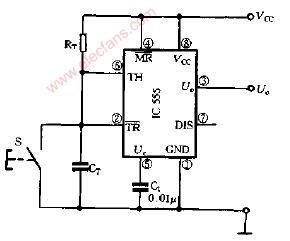

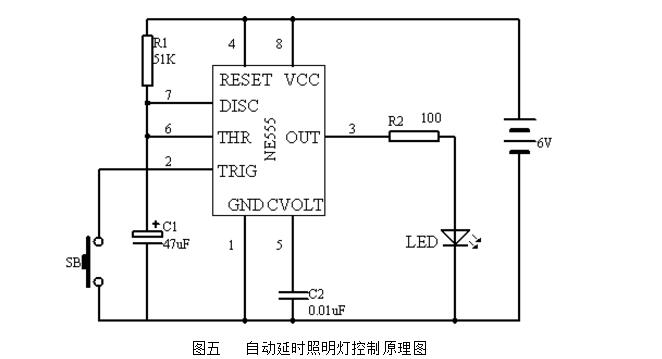

這是一款單穩態觸發式定時電路,該電路將555時基電路接成單穩態形式,平時按鈕開關S為常開狀態,555時基電路的③腳輸出低電平,此時內部放電開關閉合,電容C上的電壓為零。

2021-05-06 13:47:24

電路設計--正弦穩態電路.ppt

2017-09-10 14:12:32

電路設計--正弦穩態電路.ppt

2017-09-14 16:41:24

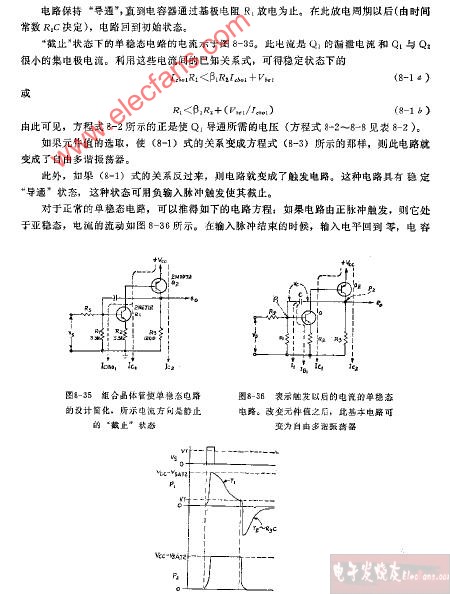

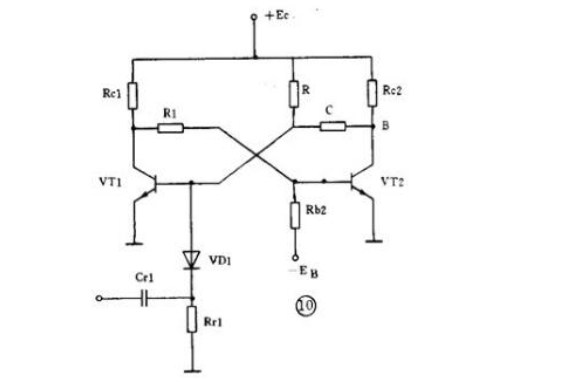

轉等。三,單穩態電路電源接通時,一個三極管始終保持截止狀態不變,另一個三極管始終保持飽和狀態不變。當有外來信號觸發時,原來截止的變為飽和狀態,原來飽和的變為截止狀態。但經過一段時間,兩個三極管又恢復到

2008-05-26 13:41:13

幾個信息:①用CD14538設計的單穩態電路,采用的是上升沿觸發。②觸發脈沖寬度大于14538的暫穩態時間。③發現一個觸發脈沖會引起進入2次暫穩態。如果觸發脈沖寬度小于暫穩態時間就不會

2020-04-29 09:01:47

words:FPGA/CPLD;Synchronous design;Clock;Metastable state利用FPGA/CPLD實現數字系統電路設計時,如何設計出可讀性強、重復利用率高、工作穩定可靠

2009-04-21 16:42:01

FPGA與CPLD的區別

盡管很多人聽說過CPLD,但是關于CPLD與FPGA之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單

2011-09-27 09:49:48

說起亞穩態,首先我們先來了解一下什么叫做亞穩態。亞穩態現象:信號在無關信號或者異步時鐘域之間傳輸時導致數字器件失效的一種現象。

2019-09-11 11:52:32

各位大神,你們好 我是新手,求助。開始我連接好M74LS123P單穩態觸發器電路進行測試沒有問題,后來發現穩態時芯片發熱,然后就不能工作了 應該是被燒壞,工作電壓安說明書設置,請問大神指點發熱燒壞是什么原因?謝謝!

2015-09-02 14:58:36

各位大哥,有誰用altium designer 仿真過單穩態觸發器的嗎?比如74ls123之類的,我在庫里怎么找不到仿真模型啊!是原本就不帶嗎?有沒有高手自己寫過啊!求幫助!

2012-03-01 15:15:18

請問大家為什么multisim里電容的充電過程比預計的慢使用的是mulitisim14.0,用555單穩態電路來實現觸摸延時功能運行時電路邏輯沒有問題,給下降沿時進入暫態,電容充電到2/3VCC時輸出為低電平,但是電容的充電時間比計算的1.1RC長很多。

2022-05-19 08:27:09

請問什么是電路的穩態?

2019-12-05 17:24:33

本白皮書介紹FPGA 中的壓穩態,為什么會出現這一現象,它是怎樣導致設計失敗的。介紹怎樣計算壓穩態MTBF,重點是對結果造成影響的各種器件和設計參數。

2021-05-06 08:35:22

使用單穩態觸發器74HC123輸出固定脈寬,奇怪的是我在使用面包板單片驗證的時候,輸出脈寬是64ms,將器件焊接上印制板后(外圍的RC值不變),輸出脈寬變成了71ms,差距為什么這么大呢…請各位老師幫忙解答一下。

2021-09-06 23:57:50

按照網站所示,在multisim中,對555可重復單穩態電路進行仿真,發生仿真錯誤。。。輸入為2khz的方波,電路延時時間為1.1ms,大于輸入周期0.5ms,電路原理上應該沒問題。。。收斂助手解決失敗,按網上說的修改步長也沒用,想問下還有啥方法可以解決問題嗎

2021-01-12 00:21:46

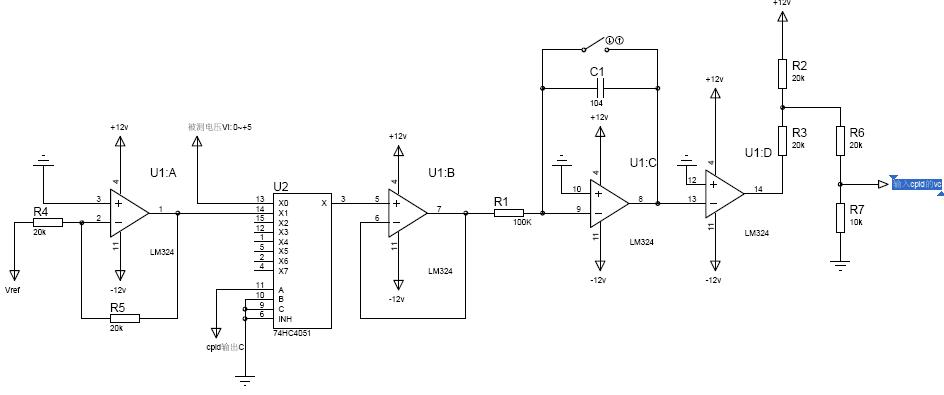

隨著電子技術特別是數字集成電路技術的迅猛發展,市面上出現了FPGA、CPLD等大規模數字集成電路,并且其工作速度和產品質量不斷提高。利用大規模數字集成電路實現常規的單穩態集成電路所實現的功能,容易

2019-08-16 06:12:46

數字增益控制電路的原理是什么如何用CPLD器件實現DAGC運算?數控衰減器在中頻電路中引入的沖擊振蕩問題數控衰減器的實現方法

2021-04-08 06:02:44

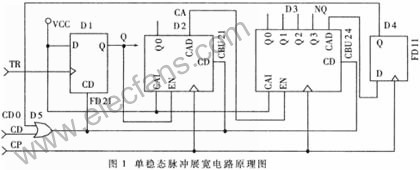

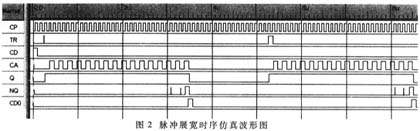

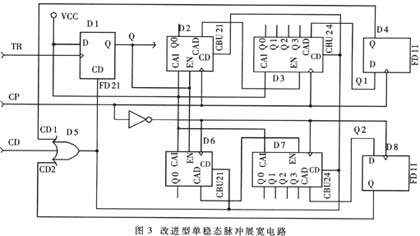

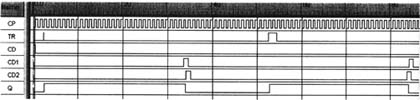

在數字電路設計中,當需要將一輸入的窄脈沖信號展寬成具有一定寬度和精度的寬脈沖信號時,往往很快就想到利用54HC123或54HC4538等單穩態集成電路。

2019-11-05 06:07:18

微分型單穩態觸發器的Multisim分析

2012-08-06 13:13:22

我正在嘗試在CPLD xc2c64a上實現雙穩態多諧振蕩器。我需要這個雙穩態多諧振蕩器電路來檢測三相輸入的相序。結果對A- > B ---> C序列有好處,但對A- > C-

2019-04-16 10:51:29

大家好,我想找一款高速的帶有單穩態(monostable)的比較器,鑒別到一個脈沖后能夠輸出固定寬度的波形。謝謝!

2018-09-06 14:32:06

單穩態電路可以使用分立元件或數字邏輯門輕松制造,但單穩態電路也可以使用運算放大器構建。運算放大器單穩態多諧振蕩器(單發多諧振蕩器)電路是僅具有一個穩定狀態的正反饋(或再生)開關電路,產生指定

2021-01-12 09:26:20

555無穩態電路圖

2008-01-09 17:23:08 5

5 介紹利用Altera 公司CPLD 器件實現對電機高精度、寬范圍調速的控制方案,并給出簡明扼要的VHDL 程序結構與仿真結果。

2009-05-15 14:00:03 23

23 CPLD 器件應用隨著生產工藝的逐步提高以及 CPLD 開發系統的不斷完善,CPLD 器件容量也由幾百門飛速發展到百萬門以上,使得一個復雜數字系統完全可以在一個芯片中實現。HDL

2010-01-27 11:40:02 48

48 CPLD 器件在單片機控制器中的使用摘要:CPLD 器件與單片機結合,可以優勢互補,組成靈活的、硬軟件都可現場編程的控制器,縮短開發周期,適應市場需要。結合實際工作的經驗

2010-02-08 09:49:56 42

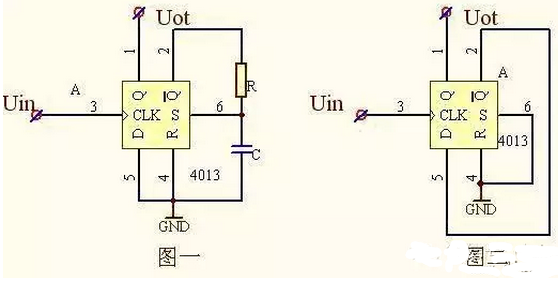

42 穩態電路原理及設計及應用圖一為雙穩態電路,它是由兩級反相器組成的正反饋電路,有兩個穩定狀態,或者是BG1導通、BG2截止;或者是BG1截止、BG2導通,由于它具

2010-03-03 10:20:40 24

24 當利用CPLD/FPGA開發系統完成數字電路或系統的開發設計并仿真校驗通過之后,就需要將獲得的CPLD/FPGA編程配置數據下載到CPLD/FPGA芯片中,以便最后獲得所設計的硬件數字電路或系

2010-06-01 10:14:46 23

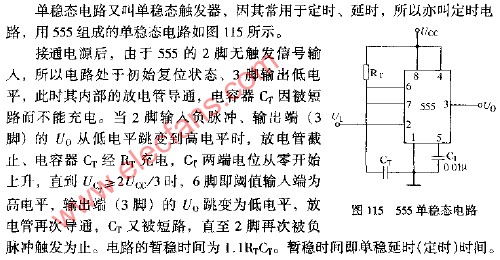

23 555時基電路是一種線性集成電路, 它在定時、檢測 控制等方面應用卜分廣泛。用555時壯電路掏成的無穩態與單穩態電路多種多樣.本文簡述兒倒.供參考。

2010-08-06 15:44:33 272

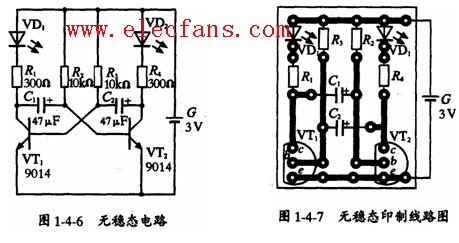

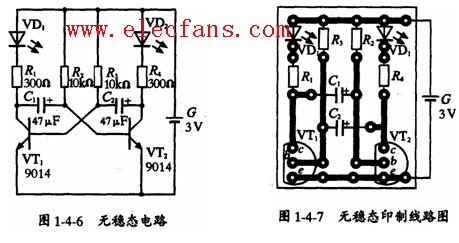

272 三極管無穩態電路

2008-05-26 13:38:47 3982

3982

長脈寬單穩態電路圖

2009-05-08 13:57:03 677

677

典型的單穩態電路圖

2009-05-08 14:02:14 4987

4987

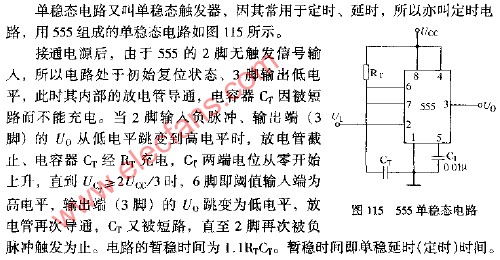

555單穩態基本電路原理圖

2009-05-08 14:49:24 3508

3508

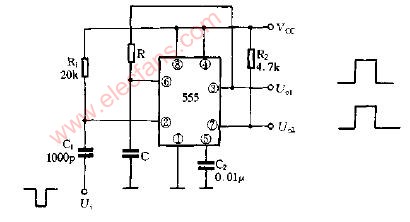

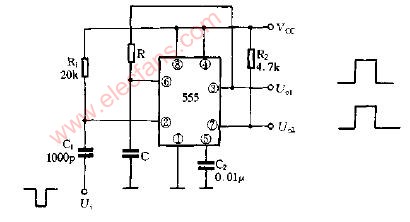

雙路輸出的單穩態電路圖

2009-05-08 14:57:34 944

944

【摘 要】 介紹了一種基于CPLD器件設計看門狗電路的方法。 關鍵詞:CPLD,看門狗,計數器

1 引 言 隨著現代電子技

2009-05-16 19:18:28 700

700

一、 配置方式

ALTERA CPLD器件的配置方式主要分為兩大類:主動配置方式和被動方式。主動配置方式由CPLD器件引導配置操作過程,它控制著外部存儲器和

2009-06-20 10:58:14 1928

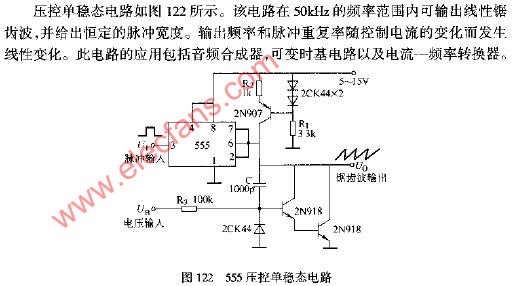

1928 電調脈寬的單穩態電路圖

2009-06-26 13:14:04 748

748

簡單型單穩態電路圖

2009-06-29 11:23:08 2370

2370

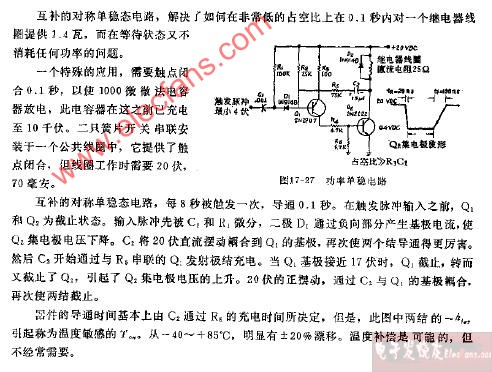

高占空比的單穩態電路圖

2009-07-03 11:42:38 518

518

功率單穩態電路圖

2009-07-03 11:43:16 378

378

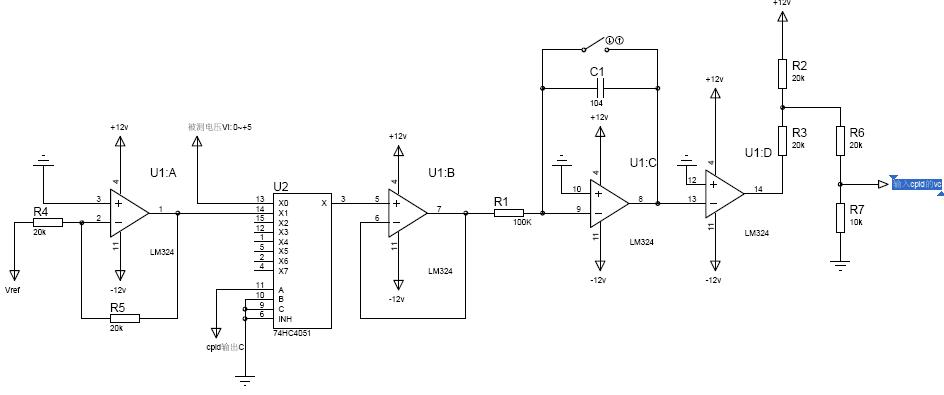

cpld的輸入電源電路

2009-09-08 00:48:28 896

896

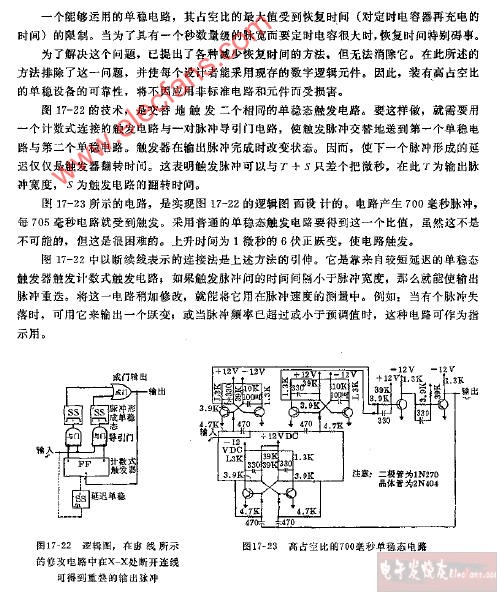

CPLD邏輯電路 圖6是CPLD內部邏輯電路,CPLD選用的是LATTICE公司的ispLSI1016E,邏輯設計采用原理圖輸入法,主要功能是對MUX的通道進行選擇、對A/D轉換器進

2009-11-13 12:04:13 2502

2502

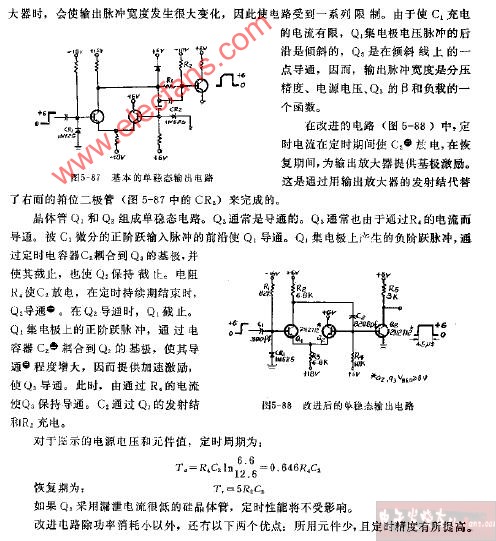

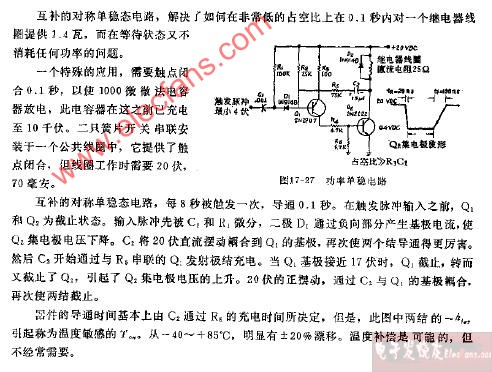

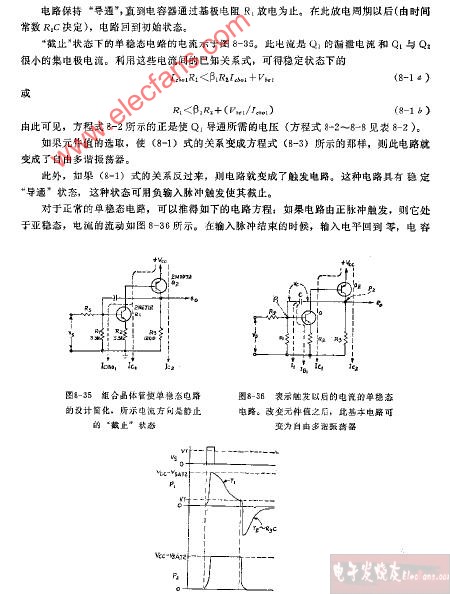

互補管單穩態電路

圖4示出兩種形式的互補管單穩態電路,圖4(b)為常態時兩管飽和的互補管單穩態電路。當滿足

2010-03-10 16:33:56 975

975

CPLD,CPLD是什么意思

CPLD是指結構比較復雜的可編程邏輯器件,它包括下述輸出宏單元結構:

(1)可編程I/O 允

2010-03-26 17:08:50 3081

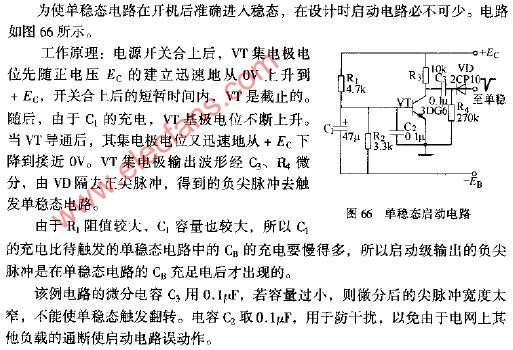

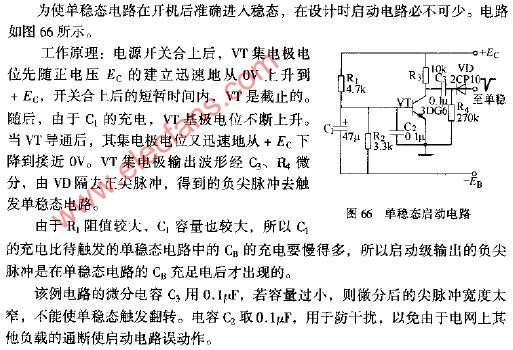

3081 單穩態啟動電路原理圖

2010-03-29 15:54:52 2217

2217

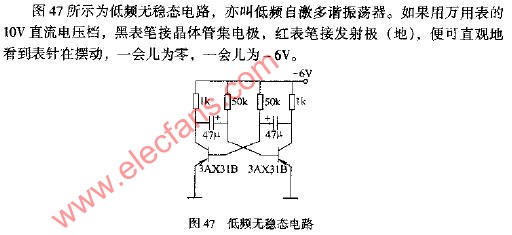

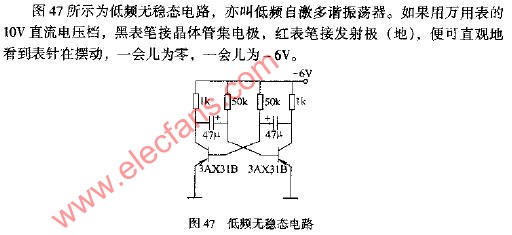

低頻無穩態電路原理圖

2010-03-29 15:55:45 1957

1957

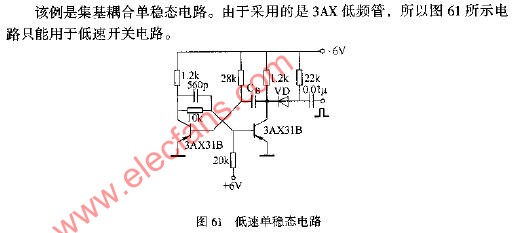

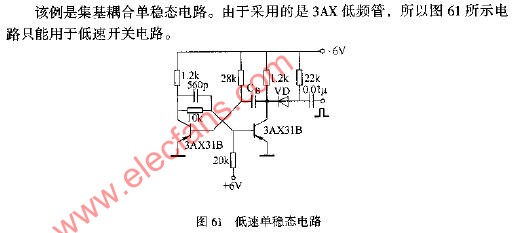

低速單穩態電路原理圖

2010-03-29 15:56:24 1693

1693

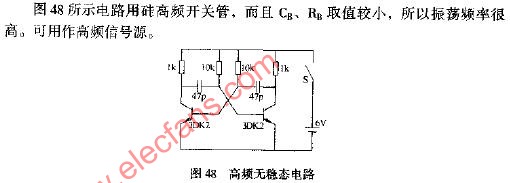

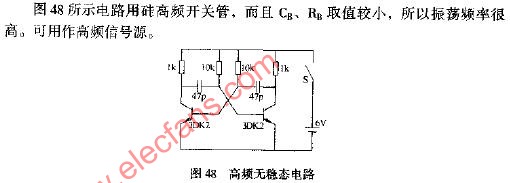

高頻無穩態電路

2010-03-29 16:05:13 414

414

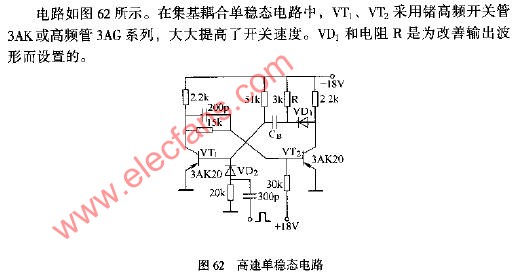

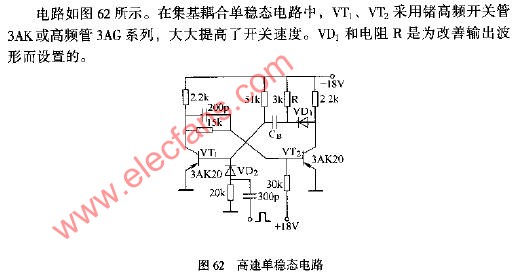

高速單穩態電路原理圖

2010-03-29 16:05:56 626

626

集基耦合單穩態電路圖

2010-03-29 16:07:32 1259

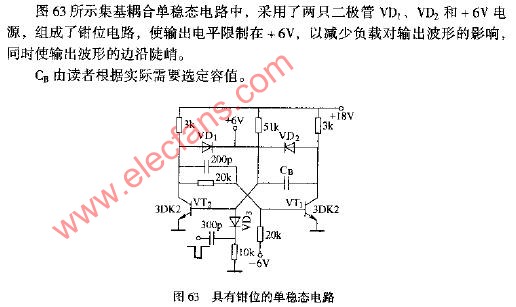

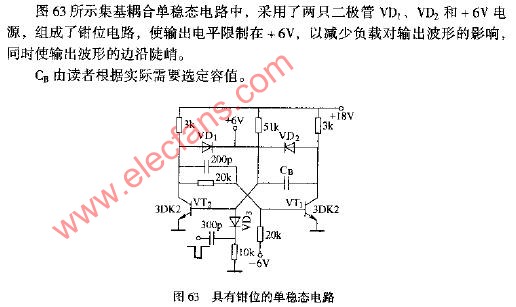

1259 具有鉗位的單穩態電路圖

2010-03-29 16:57:42 1084

1084

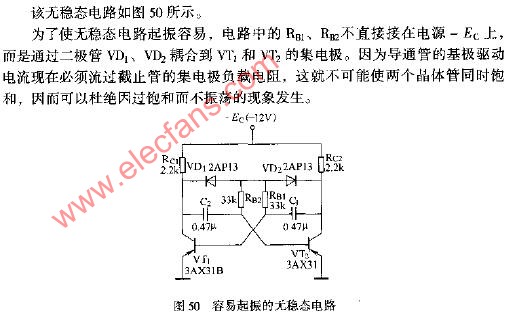

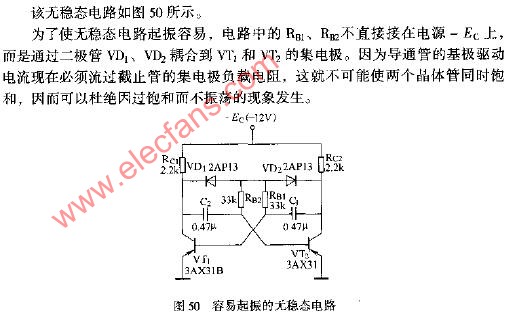

易起振的無穩態電路圖

2010-03-29 17:29:10 925

925

三管無穩態電路圖(二)

2010-03-29 17:31:30 485

485

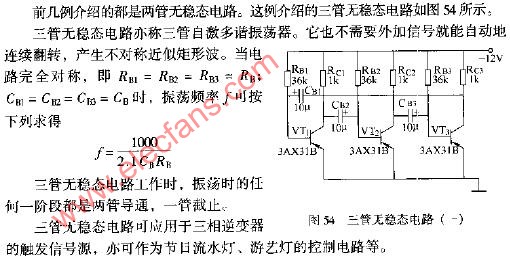

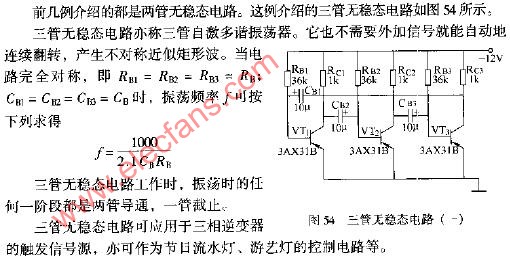

三管無穩態電路圖(一)

2010-03-29 17:32:20 1034

1034

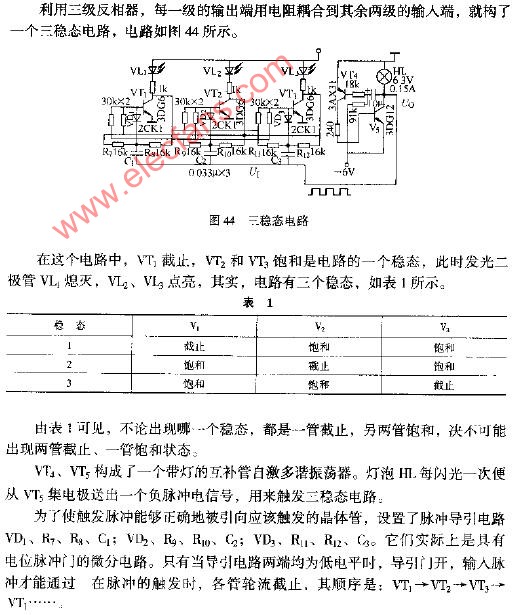

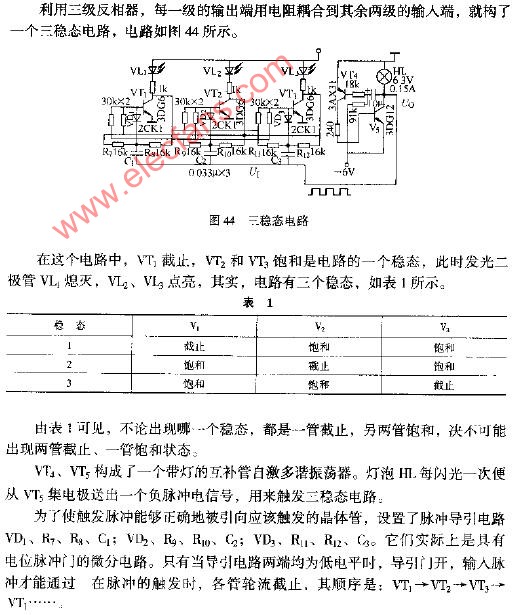

三穩態電路圖

2010-03-29 17:33:34 2116

2116

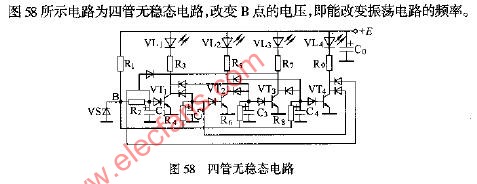

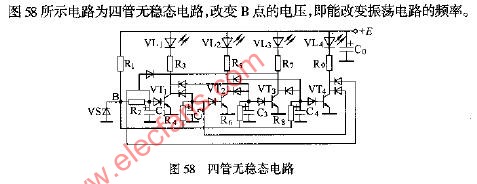

四管無穩態電路圖

2010-03-29 18:00:02 936

936

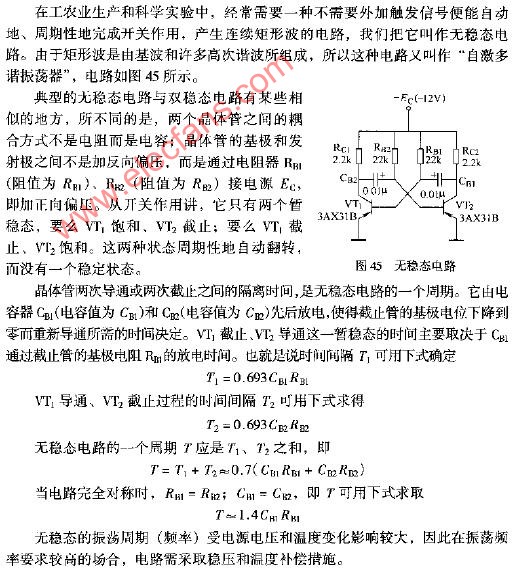

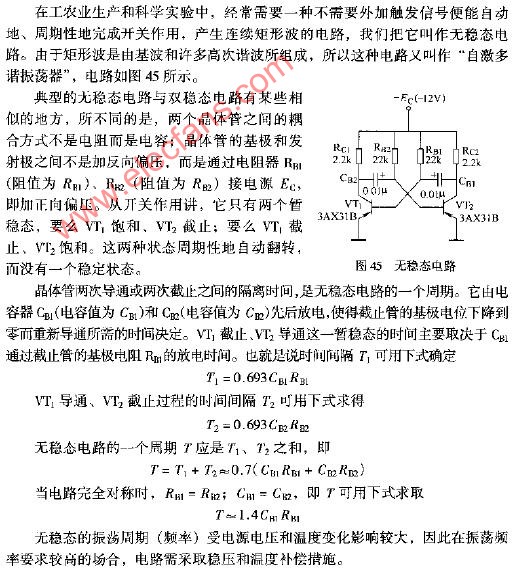

無穩態電路圖

2010-03-29 18:03:05 2812

2812

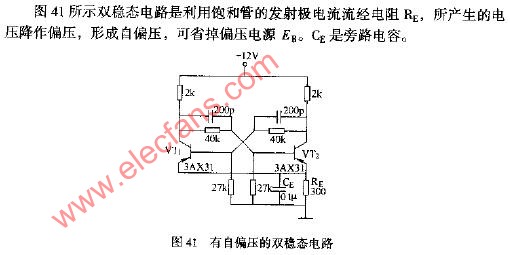

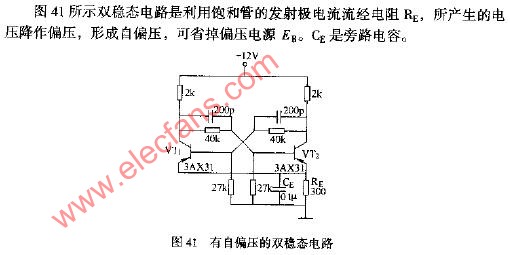

有自偏的雙穩態電路圖

2010-03-29 18:05:25 1190

1190

555單穩態電路圖

2010-03-30 14:50:53 619

619

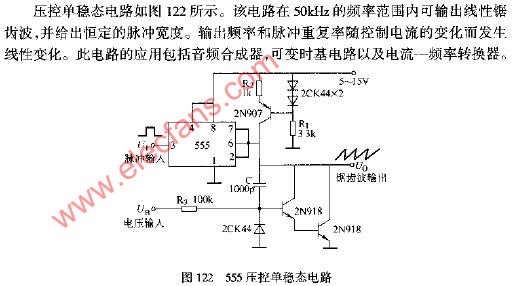

555壓控單穩態電路圖

2010-03-30 15:23:34 1358

1358

具體介紹了基于CPLD 器件設計單穩態窄脈沖展寬電路的詳細過程和這種單穩態窄脈沖展電路的特點,給出了相應的時序仿真波形,提出了提高展寬脈沖寬度精確度的方法。

2011-12-17 00:23:00 35

35 單穩態電路,數字電路重要的概念,快啦學習吧

2016-01-12 18:30:48 0

0 模擬PUT(可編程單結晶體管)器件雙穩態電路原理圖都是值得參考的設計。

2016-05-11 17:11:44 15

15 單穩態電路就是只有一種穩定輸出狀態的電路,如不自鎖的按鈕開關控制燈泡就是一個最典型、最簡單的單穩態電路:不按按鈕時,按鈕處于抬起位,其常開觸點斷開,燈泡熄滅。

2016-11-28 11:39:58 17527

17527

線性時不變動態電路在角頻率為ω的正弦電壓源或電流源激勵下,隨著時間的增長,當暫態響應消失,只剩下正弦穩態響應,電路中全部電壓電流都是角頻率為ω的正弦波時,稱電路處于正弦穩態。滿足這類條件的動態電路通常稱為正弦電流電路或正弦穩態電路

2017-05-05 10:06:36 33831

33831

單穩態電路就是只有一種穩定輸出狀態的電路,如不自鎖的按鈕開關控制燈泡就是一個最典型、最簡單的單穩態電路:不按按鈕時,按鈕處于抬起位,其常開觸點斷開,燈泡熄滅

2017-06-09 16:19:26 21080

21080

電路設計--正弦穩態電路

2017-08-07 09:31:19 0

0 隨著CPLD器件被廣泛應用于各種儀器、儀表設備的設計中,而且CPLD幾乎可模擬任何一種邏輯電路,所以,現在在設計時已完全沒有必要再放置一片獨立的看門狗器件,而完全可以將硬件看門狗電路整合于CPLD器件中,從而節省成本,降低系統的設計風險。下面具體介紹這種基于CPLD技術的看門狗電路的設計。

2018-03-05 16:58:01 2420

2420

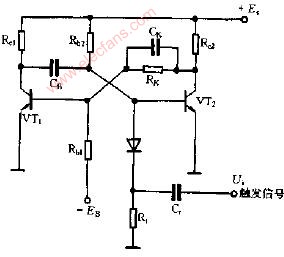

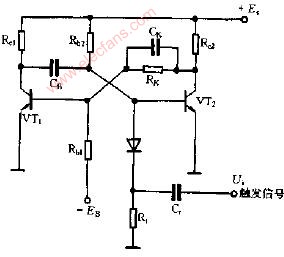

單穩態電路是一種具有穩態和暫態兩種工作狀態的基本脈沖單元電路。本文主要介紹了五款單穩態電路應用實例。

2018-03-27 09:42:38 55983

55983

CPLD的MAX系列器件庫max-13.0.1.232

2022-12-21 17:26:11 4

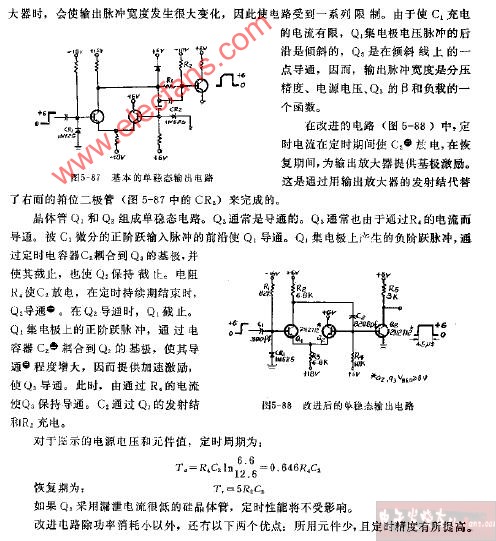

4 圖顯示了一組典型的基極耦合單穩態電路。它也是由兩級逆變器交叉耦合形成的正反饋電路。一半類似于多諧振蕩器,另一半類似于雙穩態電路,加上它還有一個差分觸發電路,所以可以想象它是一半不穩定電路和一半雙穩態

2023-07-03 14:49:17 723

723

本文檔主要描述了深圳市紫光同創電子有限公司(以下簡稱紫光同創)Compact 系列 CPLD 器件 的產品型號與資源規模列表、功能說明,以及直流和交流特性等內容,能讓用戶對 CPLD 器件有全面 的了解,方便用戶進行器件選型。

2023-07-04 14:52:43 7

7 單穩態觸發器是一種能夠在某個時間間隔內將輸入信號的電平轉換為期望的輸出信號電平的數字電路。在單穩態觸發器中,暫穩態時間是指當觸發器的輸入信號發生改變時,觸發器在從暫穩態過渡到穩態所需的時間。 暫穩態

2024-02-06 11:01:38 261

261 單穩態電路和雙穩態電路是電子電路中常見的兩種類型電路,它們在功能和特性上存在一些顯著差異。下面我將詳細介紹單穩態電路和雙穩態電路的區別,并解釋單穩態電路的主要功能。 單穩態電路是一種能夠在輸入脈沖

2024-02-06 11:04:48 349

349 單穩態觸發電路(Monostable Multivibrator Circuit)也被稱為單穩態多諧振電路或單搖擺電路,是一種產生一次性脈沖信號的電路。它具有穩態和非穩態兩個狀態,即在輸入觸發

2024-02-06 11:13:14 348

348

電子發燒友App

電子發燒友App

評論